Battery pressure monitor sensor Rev. 2.4 — 11 March 2022

NBP8

Product data sheet

# **1** General description

The NBP8 family is a fully integrated battery pressure monitoring sensor (BPMS). The NBP8 BPMS solution integrates an 8-bit central processing unit (CPU) running on factory-embedded firmware with serial data interface to create the ready-to-use battery pressure monitor sensor.

The NBP8 includes unique autonomous features such as periodic data management with host notification, pressure change detection with host wake up, and self-test.

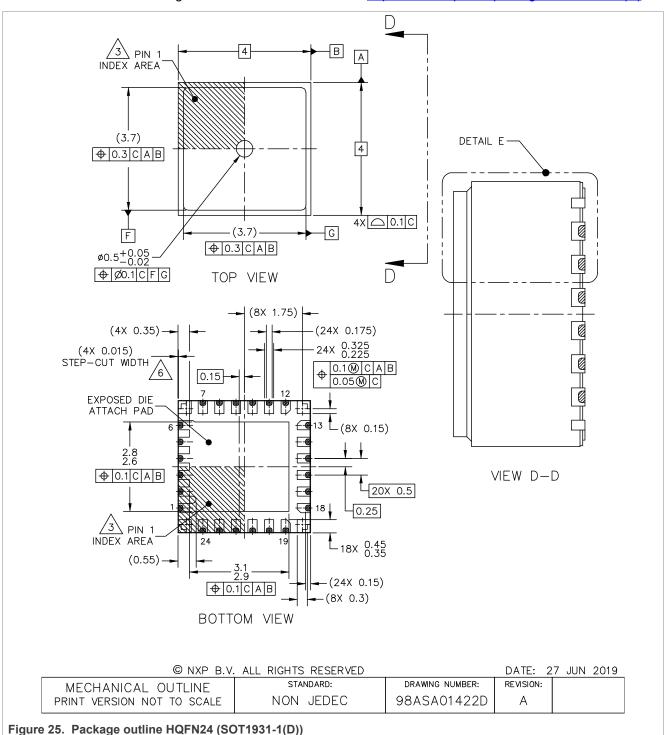

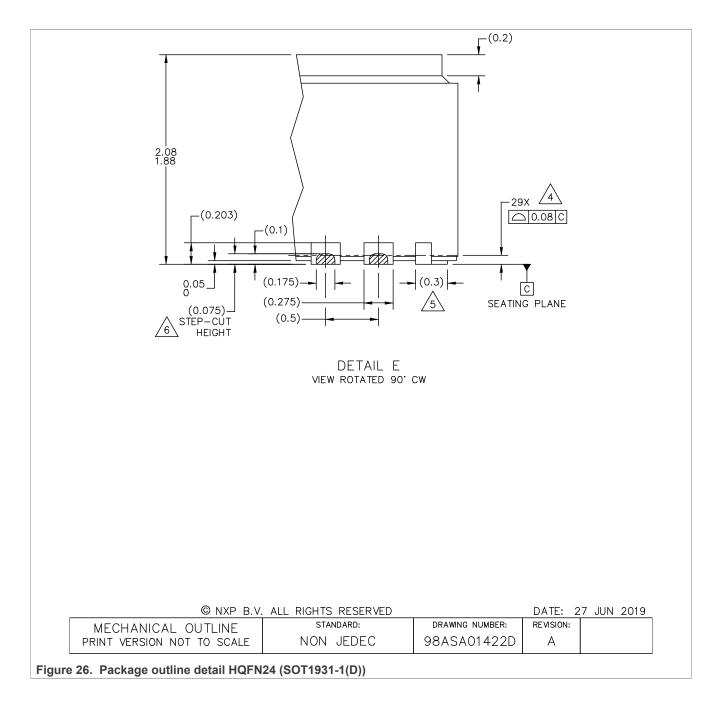

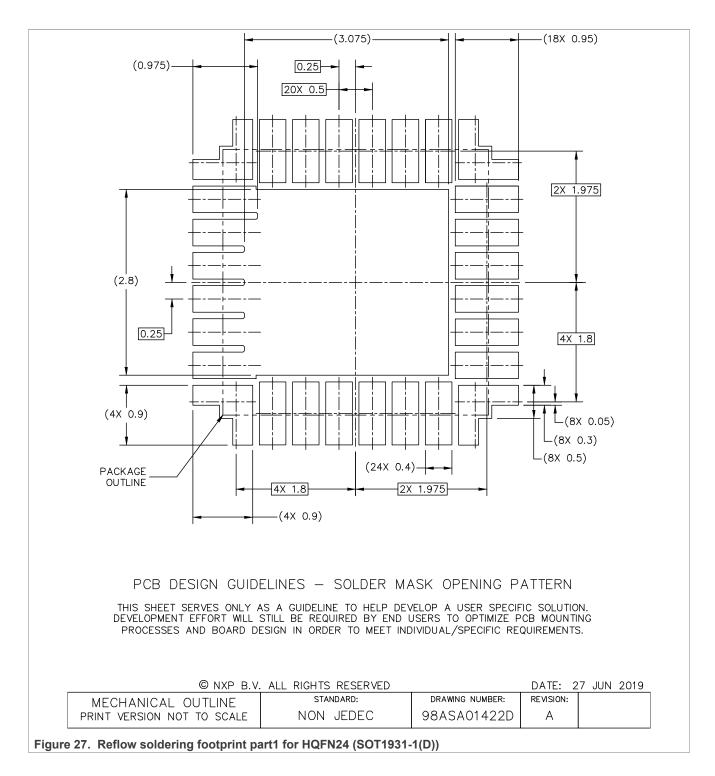

The NBP8 is packaged in a small 4 mm x 4 mm x 1.98 mm wettable-flank QFN, and is qualified to AEC-Q100 grade 1 and MSL 3 classifications.

## 2 Features and benefits

- Transducer measurement interfaces with low-power AFE:

- 10-bit compensated pressure sense element

- 8-bit compensated internal device temperature measurement

- 8-bit compensated internal device voltage measurement

- 12-entry pressure FIFO

- Selectable host wake-up indications:

- fixed pressure threshold

- relative pressure threshold

- pressure rate of change threshold

- Client SPI to support host access to internal peripherals, registers, and memory

- Qualified in compliance with AEC-Q100, Rev. H

- User-selectable sampling interval

- Low-voltage detection

# 3 Ordering information

#### Table 1. Ordering information

| Type number | Package |                                                                                                                                         |              |  |  |  |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|

|             | Name    | Description                                                                                                                             | Version      |  |  |  |  |  |  |

| NBP8        | VSON    | plastic thermal enhanced quad flat package; no leads, 0.1 dimple wettable flank; 24 terminals; 0.5 mm pitch, 4 mm x 4 mm x 1.98 mm body | SOT1931-1(D) |  |  |  |  |  |  |

#### Table 2. Ordering options

| Part Number | Pressure Range    | Pressure tolerances |

|-------------|-------------------|---------------------|

| NBP8FD4T1   | 40 kPa to 250 kPa | Standard tolerances |

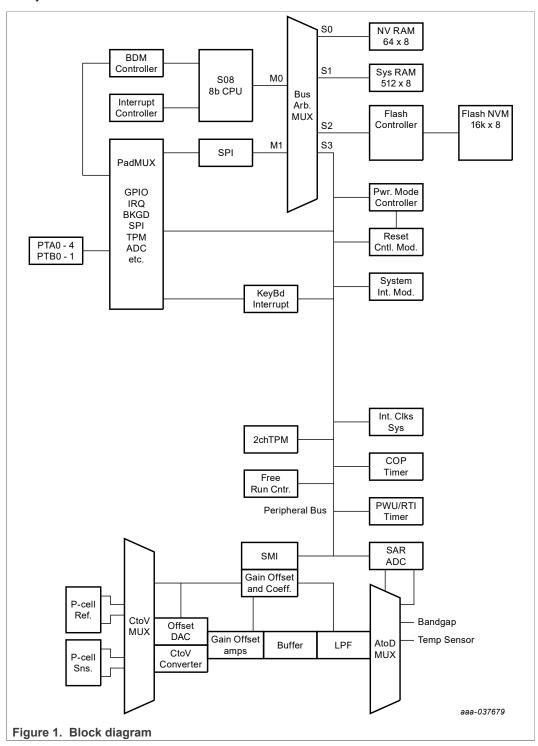

# 4 Block diagram

<u>Figure 1</u> presents the main blocks of the device and their signal interactions. Power management controls and bus control signals are not shown in this block diagram for clarity.

NBP8 Product data sheet

## 5 Pinning information

This section describes the pin layout and general function of each pin.

## 5.1 Pinning

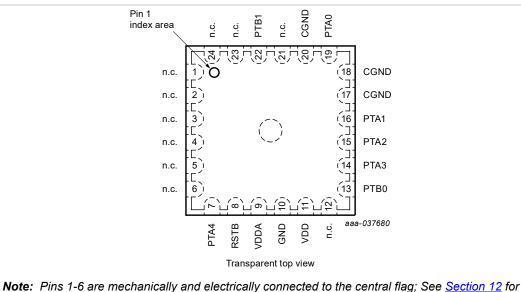

The device pinout is shown in Figure 2 for the orientation of the pressure port up.

**Note:** Pins 1-6 are mechanically and electrically connected to the central flag; See <u>Section 12</u> for details. If additional ground is desired, any of the pins 1-6 may be routed to circuit board ground plane, or the central flag may be connected to circuit board ground plane with vias.

Figure 2. Pin configuration

## 5.2 Pin description

| Symbol | Pin | Function | Description                                                       |

|--------|-----|----------|-------------------------------------------------------------------|

| n.c.   | 1   |          | Do not connect electrical signals to this pin; solder joint only. |

| n.c.   | 2   | _        | Do not connect electrical signals to this pin; solder joint only. |

| n.c.   | 3   | —        | Do not connect electrical signals to this pin; solder joint only. |

| n.c.   | 4   | —        | Do not connect electrical signals to this pin; solder joint only. |

| n.c.   | 5   | —        | Do not connect electrical signals to this pin; solder joint only. |

| n.c.   | 6   | _        | Do not connect electrical signals to this pin; solder joint only. |

#### NBP8 Product data sheet

Table 2 Div description

| Table 3. Pin descriptioncontinued |

|-----------------------------------|

|-----------------------------------|

| Symbol | Pin | Function                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-----|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTA4   | 7   | PTA4 / BKGD                                    | PTA4 Pin - The PTA4 pin places the device in the BACKGROUND DEBUG mode (BDM) to evaluate CPU code and transfer data to/from the internal memory. If the BKGD/PTA4 pin is held low when the device comes out of a power-on-reset (POR), the device switches into the ACTIVE BACKGROUND DEBUG mode (BDM).<br>The BKGD/PTA4 pin has an internal pullup device or can be connected to VDD in the application, unless there is a need to enter BDM operation after the device as been soldered into the PWB. If in-circuit BDM is desired, the BKGD/PTA4 pin should be connected to VDD through a resistor (~10 kΩ or greater) which can be over-driven by an external signal. This resistor reduces the possibility of inadvertently activating the debug mode in the application programs port A to GPIOs, PTA4 becomes output-only.                                                                                                  |

| RST_B  | 8   | Reset / V <sub>PP</sub><br>programming voltage | The RST_B pin is used for test and establishing the BDM condition and providing the programming voltage source to the internal FLASH memory. This pin will only be used by customers who intend to reprogram the NBP. The RST_B pin has an internal pullup device and can be connected to VDD in the application unless there is a need to enter BDM operation after the device as been soldered to the PWB. If in-circuit BDM is desired, the RST_B pin can be left unconnected; but should be connected to VDD through a low impedance resistor (<10 k $\Omega$ ) which can be over-driven by an external signal. This low impedance resistor reduces the possibility of getting into the debug mode in the application due to an EMC event. Activation of the external reset function occurs when the voltage on the RST_B pin goes below 0.3 × V <sub>DD</sub> for at least 100 ns before rising above 0.7 × V <sub>DD</sub> . |

| VDDA   | 9   | Analog supply                                  | The analog circuits operate from a single power supply connected to the unit<br>through the VDDA pin. VDDA is the positive supply and GND is the ground.<br>The conductors to the power supply should be connected to the VDDA and<br>GND pins and locally decoupled.<br>Care should be taken to reduce measurement signal noise by separating<br>the VDD, GND, VDDA, and no RFGND pins using a "star" connection such<br>that each metal trace does not share any load currents with other external<br>devices.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GND    | 10  | Digital and analog<br>ground                   | The digital circuits operate from a single power supply connected to the unit through the VDD and GND pins. GND is the ground. Care should be taken to reduce measurement signal noise by separating the GND pins using a "star" connection such that each metal trace does not share any load currents with other external devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VDD    | 11  | Digital supply                                 | The digital circuits operate from a single power supply connected to the unit through the VDD and GND pins. VDD is the positive supply. The conductors to the power supply should be connected to the VDD and GND pins and locally decoupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| n.c.   | 12  |                                                | Do not connect electrical signals to this pin; solder joint only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| РТВО   | 13  | PTB0 / TPMCH0 /<br>AD3                         | The PTB[0] pin is a general-purpose I/O pin. This pin can be configured<br>as a nominal bidirectional I/O pin with programmable pullup devices. User<br>software must configure the general-purpose I/O pin (PTB[1:0]) so that they<br>do not result in "floating" inputs. PTB0 can be mapped to TPM channel 0, or<br>to ADC channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Symbol | Pin | Function                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-----|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTA3   | 14  | PTA3 / KBI3 / SOCI          | The PTA[3] pin is a general-purpose I/O pin. The pulldown devices can only be activated if the wake-up interrupt capability is enabled. User software must configure the general-purpose I/O pins so that they do not result in "floating" inputs. PTA[3] maps to keyboard interrupt function bit [3]. When SPI is enabled, PTA[3] serves as SOCI.                                                                                                                                                                                                   |

| PTA2   | 15  | PTA2 / KBI2 / SICO          | The PTA[2] pin is a general-purpose I/O pin. The pulldown devices can only be activated if the wake-up interrupt capability is enabled. User software must configure the general-purpose I/O pins so that they do not result in "floating" inputs. PTA[2] maps to keyboard interrupt function bit [2]. When SPI is enabled, PTA[2] serves as SICO.                                                                                                                                                                                                   |

| PTA1   | 16  | PTA1 / KBI1 / SCLK          | The PTA[1] pin is a general-purpose I/O pin. The pulldown devices can only be activated if the wake-up interrupt capability is enabled. User software must configure the general-purpose I/O pins so that they do not result in "floating" inputs. PTA[1] maps to keyboard interrupt function bit [1]. When SPI is enabled, PTA[1] serves as SCLK                                                                                                                                                                                                    |

| CGND   | 17  | _                           | To be connected to ground by the application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CGND   | 18  | _                           | To be connected to ground by the application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PTA0   | 19  | PTA0 / KBI0 / CS_B /<br>IRQ | The PTA[0] pin is a general-purpose I/O pin. PTA[0] can be configured as a normal bidirectional I/O pin with programmable pullup or pulldown devices and/or wake-up interrupt capability. PTA[0] can be configured for external interrupt (IRQ). The pulldown devices can only be activated if the wake-up interrupt capability is enabled. User software must configure the general-purpose I/O pins so that they do not result in "floating" inputs. PTA[0] maps to keyboard interrupt function bit [0]. When SPI is enabled, PTA0 serves as CS_B. |

| CGND   | 20  | —                           | To be connected to ground by the application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| n.c.   | 21  | —                           | Do not connect electrical signals to this pin; solder joint only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PTB1   | 22  | PTB1 / TPMCH1 /<br>AD4      | The PTB[1] pin is a general-purpose I/O pin. This pin can be configured<br>as a nominal bidirectional I/O pin with programmable pullup devices. User<br>software must configure the general-purpose I/O pins (PTB[1:0]) so that they<br>do not result in "floating" inputs. PTB1 can be mapped to TPM channel 1, or<br>to ADC channel 4.                                                                                                                                                                                                             |

| n.c.   | 23  |                             | Do not connect electrical signals to this pin; solder joint only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| n.c.   | 24  |                             | Do not connect electrical signals to this pin; solder joint only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |     |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 3. Pin description...continued

Battery pressure monitor sensor

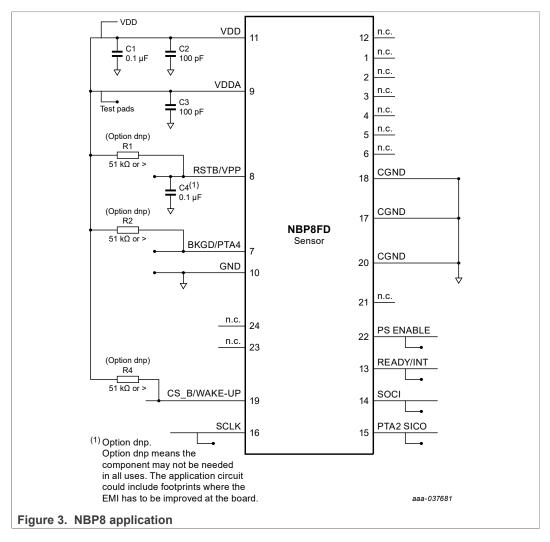

# 5.3 Application

NBP8 Product data sheet

# 6 Functional description

## 6.1 Communication between the NBP8 and external host

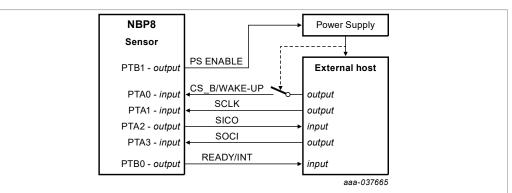

An example block diagram of NBP8 with an external host is shown in Figure 4:

| Pin                 | Description                                                                                                                                                                                                                                                                                        | Remarks                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS ENABLE<br>(PTB1) | Power supply enable.                                                                                                                                                                                                                                                                               | When enabled, the NBP8 asserts the PS ENABLE pin before generating a pulse on the INT pin.                                                                                                                                                                                                                                                                           |

| CS_B/WAKE UP (PTA0) | <ul> <li>When SPI is enabled: Client Select<br/>active low</li> <li>When SPI is disabled: WAKE-UP /<br/>low state triggers an interrupt on<br/>NBP8 side (no edge required)</li> </ul>                                                                                                             | When SPI is disabled, the WAKE-UP<br>signal can be used for the external host<br>to request SPI communication with the<br>NBP8, to read memory and change<br>settings, or trigger a self-test, firmware<br>verification, software reset, or clear<br>flags and user FIFO.<br>When SPI is enabled, Client Select<br>when active low, ready for SCLK clock<br>and data |

| SCLK (PTA1)         | SPI clock                                                                                                                                                                                                                                                                                          | SPI clock from external host                                                                                                                                                                                                                                                                                                                                         |

| SICO (PTA2)         | SPI SICO                                                                                                                                                                                                                                                                                           | Server-In-Client-Out data                                                                                                                                                                                                                                                                                                                                            |

| SOCI (PTA3)         | SPI SOCI                                                                                                                                                                                                                                                                                           | Server-Out-Client-In data                                                                                                                                                                                                                                                                                                                                            |

| READY / INT (PTB0)  | <ul> <li>READY signal: following a WAKE-UP event, the NBP8 indicates to the external host it is ready for the SPI transfers by asserting the pin.</li> <li>INT signal: the NBP8 notifies the external host that an event requiring attention occurred by generating a pulse on the pin.</li> </ul> | The external host should enable a pull<br>up/down to maintain the pin in idle state<br>as long as the NBP8 does not assert it.                                                                                                                                                                                                                                       |

Table 4. Connection pins description

**Note:** When the NBP8 is in sleep mode, the CS\_B/WAKEUP pin is configured as input with pull-up enabled. All other pins are in high impedance state, which means that the NBP8 does not maintain their levels. Specifically, the level of the PS ENABLE pin is not maintained by the NBP8 in sleep, so when this signal is used, its idle level must be maintained by an external circuit.

**Note:** If the external host will be switched off, the CS\_B/WAKE UP signal must be isolated to prevent inadvertent assertion; a fixed low level at the NBP8 CS\_B/WAKE UP input will cause the sensor to remain waiting for the SPI SCLK, and not collect new pressure measurements.

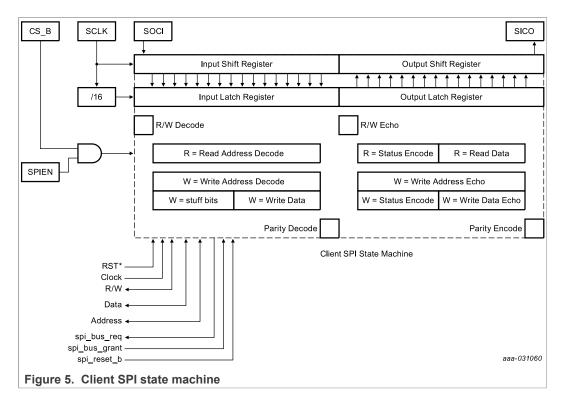

## 6.2 Serial peripheral interface (SPI) module

The SPI module is configured as a standard client SPI which allows a full duplex, synchronous, serial communication between the unit and a server SPI device.

The principal features of the SPI block are summarized as follows:

- Client only mode operation.

- Full-duplex, 4 wire, synchronous serial communication.

- Command-Response communication format.

- SCLK operation up to 10 MHz supported.

- Fixed Clock polarity and phase supported (CPOL=0, CPHA = 0).

- The SPI module requires the base clock value to be at the low state (CPOL = 0) with data captured on the rising edge of the clock and data propagated on the falling edge of the clock (CPHA = 0).

- Supports 8-bit register read and write operations via 16 clock transfers.

- Even Parity error-checking.

- Alternate bus controller for the system-on-chip (SoC) internal IP Bus system.

- SPI can be used to access the entire Memory map of the NBP8.

- Contains eight, 8-bit memory mapped registers for user and test mode operations.

- Decodes SPI test mode entry sequence and enables SPI test mode.

As a client, the SPI interface is compatible with SPI interface mode 00, corresponding to CPOL = 0 and CPHA = 0. For CPOL = 0, the idle value of the clock is zero, and the active value of the clock is 1. For CPHA = 0, data is captured on the rising edge (low to high transition) of the clock and data is propagated on the falling edge (high to low transition) of the clock.

As a client, the CS\_B pin is driven low at the start of a transaction, held low for the duration of the transfer, and then driven high again after the transaction is completed. During a transaction, the server toggles the clock (SCLK). The SCLK polarity is defined as having an idle value that is low, and an active phase that is high (CPOL = 0). Serial input and output data is captured on the rising edge of the colock and propagated on the falling edge (CPHA = 0). Single-byte read and single-byte write operations are completed in two strobes of CS\_B of 16 SCLK cycles each; multiple byte reads and writes are completed in additional multiples of 16 SCLK cycles. The first SCLK cycle latches the most significant bit on SOCI to select whether the desired operation is a read (R/W = 1) or a write (R/W = 0). The following 13 SCLK cycles are used to latch the client register read or write address. The final two SCLK cycles are used to latch the parity calculation results.

When memory is secured by SEC[1:0] settings, the SPI may access only the address ranges indicated in <u>Section 6.8 "Read/write targets accessible by the external host via</u> <u>SPI"</u>. Other access attempts result in an error status as defined below.

**Note:** The SPI and the CPU share the internal address, data, and control bus, and are arbitrated such that the SPI takes priority over the CPU. The user application must account for inhibited execution of CPU instructions during the time the SPI has taken control of the internal bus.

## Battery pressure monitor sensor

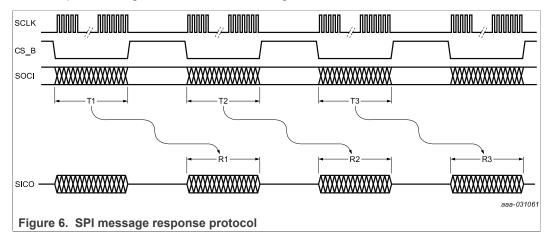

Transaction event schedule; T1 being the first server transmission, R1 being the first client response being concurrent with T2 being the second server transmission:

| Clock cycle    |    | c1  | c2  | c3  | c4  | c5  | с6  | с7 | c8 | c9 | c10 | c11 | c12 | c13 | c14 | c15 | c16 |

|----------------|----|-----|-----|-----|-----|-----|-----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| Bit assignment |    | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

| Read byte from | T1 | 0   | a12 | a11 | a10 | a9  | a8  | а7 | a6 | а5 | a4  | a3  | a2  | a1  | a0  | р1  | р0  |

| Address        | R0 | r   | s4  | s3  | s2  | s1  | s0  | r  | r  | r  | r   | r   | r   | r   | r   | р1  | р0  |

|                | T2 | t   | t   | t   | t   | t   | t   | t  | t  | t  | t   | t   | t   | t   | t   | р1  | р0  |

|                | R1 | 0   | s4  | s3  | s2  | s1  | s0  | d7 | d6 | d5 | d4  | d3  | d2  | d1  | d0  | р1  | р0  |

## Table 5. SPI protocol architecture

| Clock cycle    |    | c1  | c2  | c3  | c4  | c5  | c6  | c7 | c8 | c9 | c10 | c11 | c12 | c13 | c14 | c15 | c16 |

|----------------|----|-----|-----|-----|-----|-----|-----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| Bit assignment |    | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

| Write byte to  | T1 | 1   | a12 | a11 | a10 | a9  | a8  | a7 | a6 | а5 | a4  | a3  | a2  | a1  | a0  | р1  | p0  |

| Address        | R0 | r   | s4  | s3  | s2  | s1  | s0  | r  | r  | r  | r   | r   | r   | r   | r   | р1  | p0  |

|                | T2 | 1   | m   | m   | m   | m   | m   | d7 | d6 | d5 | d4  | d3  | d2  | d1  | d0  | р1  | p0  |

|                | R1 | 1   | a12 | a11 | a10 | a9  | a8  | a7 | a6 | а5 | a4  | a3  | a2  | a1  | a0  | р1  | p0  |

|                | Т3 | t   | t   | t   | t   | t   | t   | t  | t  | t  | t   | t   | t   | t   | t   | р1  | p0  |

|                | R2 | 1   | s4  | s3  | s2  | s1  | s0  | d7 | d6 | d5 | d4  | d3  | d2  | d1  | d0  | р1  | p0  |

#### Table 5. SPI protocol architecture...continued

Where:

c1 - c16 = SCLK cycles 1 (b15) through 16 (b0), most significant bit first, least significant bit last

b15:0 = bit assignments for each clock cycle, b15 = 0 for read; b15 = 1 for write

a12:0 = 13 LSBs of address being read or written; \$0000 to \$1FFF is direct; \$C000 to \$FFFF is indirect

p1:0 = "Even" parity bits, p1 calculated for contents of b15:9; p0 calculated for contents of b8:2

s4:0 = client status:

$0\ 0\ 0\ 0\ 0$  = all OK, no need for retry.

1 x x x x = reserved for future fault modes, default to 0 until defined

x 1 x x x =

the response in R0 for first T1 input after reset

in the case of commands ignored by SPI due to error in previous read command; that is, invalid data in response in the case the write command did not execute

x x 1 x x = clock fault, not enough clocks, or too many clocks per CS\_B cycle

x x x 1 x = parity fault from either p1 or p0

x x x x 1 = internal bus contention fault, SPI does not gain access to peripheral bus in the prescribed time, or attempt access illegal or security-blocked address

d7:0 = data being read or written

t = contents of next server transmission T#+1

m = server stuff bits, 0 or 1 by server choice, and included as part of parity calculation

r = contents of previous client response R#-1

#### Battery pressure monitor sensor

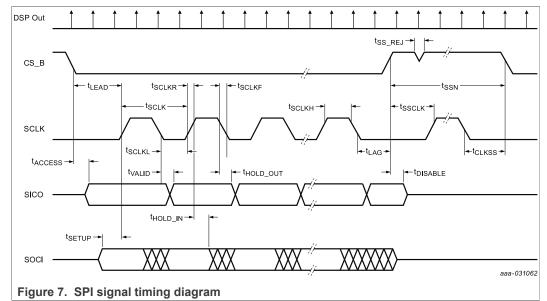

## 6.2.2 SPI signal timing definition

Enable SPI by either of the following methods:

- 1. CPU application software sets the SPIEN control bit at address \$1802 to logic 1

- 2. At power application, an external host holds the PTA0 pin low for greater than the time  $t_{\text{SPI}\ \text{EN}}$

Care must be taken by the user application to assure the SPI is not disabled by writing logic 0 to the SPIEN bit, or by entering a stop mode during an ongoing transmission. SPI can be disabled when CS\_B signal is in the inactive state, or high.

## 6.3 Main features

|--|

| Feature                    | Description                                                                                                                  | Event occurrence                          | User configuration                                                                                        |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Sensor Data<br>Measurement | The NBP8 takes compensated pressure<br>measurement and can notify the external<br>host that sensor data is available or that | Periodic                                  | Enable/disable pulse generation<br>when sensor data ready or when<br>acquisition status flag is not clear |  |  |

|                            | measurement completed with errors.<br>The last 12 pressure values are stored in<br>memory.                                   |                                           | Period selection (ODR)                                                                                    |  |  |

| Pressure<br>Change         | The NBP8 monitors the pressure change over time and notifies the external host if the                                        | Pressure value<br>is verified at the      | Pressure monitoring options selectable independently                                                      |  |  |

| Detection<br>(PCD)         | pressure change conditions set by the user are met.                                                                          | ODR rate                                  | Programmable warning thresholds                                                                           |  |  |

| (100)                      |                                                                                                                              |                                           | Programmable debounce counter                                                                             |  |  |

| Self-test                  | The NBP8 performs self-test for the ADC and                                                                                  | Periodic and/or                           | Enable/Disable periodic self-test                                                                         |  |  |

|                            | Pressure Measurement Cell (Pcell). In case of failed status, the NBP8 can notify the external                                | punctual (triggered<br>by the appropriate | If enabled, period selection                                                                              |  |  |

|                            | host.<br>The result of the last Self-test is stored in<br>memory.                                                            | command written<br>via SPI)               | Enable/disable pulse generation if an error is detected                                                   |  |  |

| Feature                               | Description                                                                                                                                                                                                                                                                               | Event occurrence                                              | User configuration                                      |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|

| Firmware<br>Integrity<br>Verification | The NBP8 calculates the 16-bit XOR<br>checksum of the entire FLASH memory<br>and compares it with the value stored at<br>production. If values are different, the NBP8<br>can notify the external host.<br>The result of the last firmware integrity<br>verification is stored in memory. | Triggered by<br>the appropriate<br>command written<br>via SPI | Enable/disable pulse generation if an error is detected |

#### Table 6. List of the main software-implemented features...continued

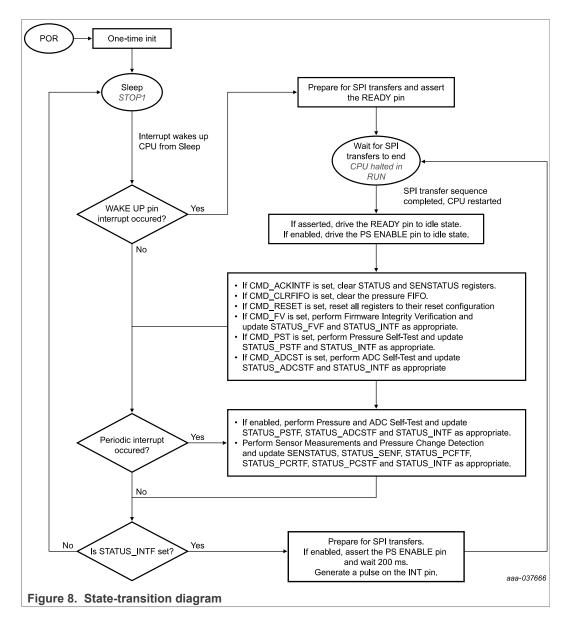

## 6.4 State-transition diagram

Periodically, the NBP8 takes pressure measurements and completes a compensation. The result is then used for the pressure change detection. Optionally, the host can configure NBP8 for the self-test.

In addition to the periodic events, the external host can request access to the NBP8 memory with the WAKE-UP pin. When the WAKE-UP pin is lowered, the NBP8 enables SPI and remains in RUN mode until the SPI transfers have completed. During the SPI transfers, the external host has read and write access to the NBP8 memory in order to perform operations such as reading status flags, reading sensor data or requesting specific actions to be taken after completion of the SPI transfers.

After completion of the periodic and internally triggered actions, the NBP8 checks whether a condition for pulse generation was met. If so, the bit STATUS\_INTF is set, the NBP8 enables SPI, optionally asserts the PS ENABLE pin, and triggers a pulse on the INT pin to notify the external host that an event requiring attention occurred. Then it remains in RUN mode while the SPI transfers have not completed.

Typically, the external host accesses the NBP8 memory and reads the STATUS register to identify the event requiring attention. Depending on the type of event, additional registers (such as SENSTATUS, the pressure FIFO, and so forth) may also be read. To acknowledge the event, the CMD\_ACKINTF bit must be set by the external host.

Figure 8 illustrates the state-transition diagram.

## Battery pressure monitor sensor

## 6.5 Pressure change detection description

## 6.5.1 Overview

Pressure measurements are taken at a period configured by the user. The last 12 measurements are stored in the pressure FIFO. The pressure FIFO acts like a rolling buffer and is described later in this section.

Several options with configurable settings are available to monitor pressure variation and determine when the external host should be notified that pressure change conditions have been met. The following three options are available and can be enabled independently. When more than one option is enabled, the program checks whether at least one option has met the condition, and if so, raises the appropriate flags and notifies the external host via the INT pin.

- Option to monitor the pressure vs. a fixed threshold: If pressure value has exceeded the fixed threshold set by the user, the flag STATUS\_PCFTF is raised.

- Option to monitor the pressure vs. a relative threshold: The NBP8 monitors when pressure is rising and raises the STATUS\_PCRTF flag when the pressure increase ΔPressure has exceeded the relative threshold set by the user.

- Option to monitor the pressure rate of change vs. a rate of change threshold: The NBP8 monitors when pressure is rising. When pressure has been rising for a certain time, configured by the user, the slope Δpressure/Δtime is calculated. If the slope is greater than the threshold configured by the user, the flag STATUS\_PCSTF is raised.

After each new sample taken, when the program has executed all algorithms of the enabled options, the STATUS\_INTF flag is raised if at least one of the pressure change STATUS flags (STATUS\_PCFTF, STATUS\_PCRTF or STATUS\_PCSTF) is raised. When STATUS\_INTF is set, the external host is notified that pressure change conditions have been met and is notified via the INT pin.

Each option is detailed in <u>Section 6.5.2</u> through <u>Section 6.5.5</u>.

## 6.5.2 Description of the fixed threshold option

This option is enabled when bit PCCFG\_FTEN is set. When a new pressure measurement is available, the pressure value is compared with the fixed threshold Pfix\_T configured by the user. If the pressure value exceeds the threshold, the debounce counter Deb\_FT\_cnt is incremented. Otherwise, Deb\_FT\_cnt is decremented. When the Deb\_FT\_cnt exceeds the Debounce\_T value configured by the user, the STATUS\_PCFTF flag is raised.

The purpose of Deb\_FT\_cnt is to make sure that the flag is raised only after the condition has been met for a minimum number of samples. This filtering avoids the possibility of a false-alarm occurring when a single-measurement meets the condition due to a coincidental event, such as noise, affecting the measurement.

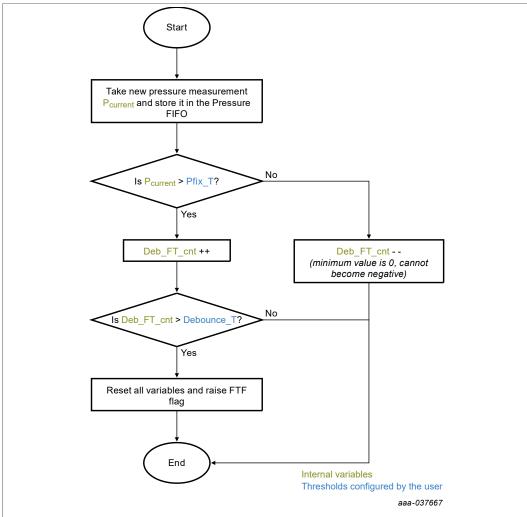

The algorithm flow is show in Figure 9.

Product data sheet

Figure 9. Fixed Threshold algorithm flow

The variables and thresholds used in the flow are described below:

- P<sub>current</sub>: variable internal to the NBP8 program that holds the latest pressure measurement.

- Pfix\_T: user-configurable threshold. The value is stored in PCFIXTH/L registers. No flag is raised as long as pressure does not consistently exceed this threshold.

- Deb\_FT\_cnt: counter internal to the NBP8 program updated every time a new pressure measurement is taken. The counter is incremented if the pressure exceeds the threshold Pfix\_T. It is decremented otherwise. When the counter reaches 0, it cannot be further decremented.

- Debounce\_T: user-configurable threshold. The value is stored in PCDEBT register. When the value in Deb\_FT\_cnt exceeds this threshold, pressure is considered to be consistently above Pfix\_T, so the FTF flag is raised and external host notified.

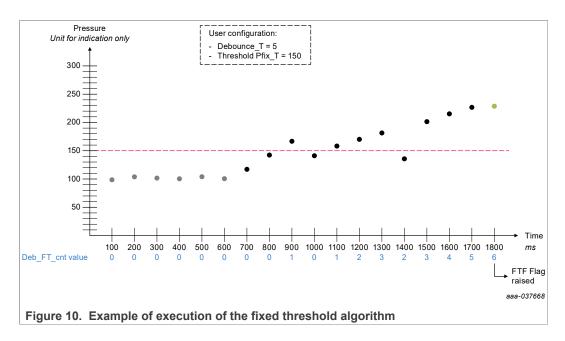

An example of algorithm execution is shown in <u>Figure 10</u>. In this example, the sample rate is set to 100 ms. The pressure FIFO depth is 12 measurements; the gray dots represent the pressure values not available in the FIFO anymore when the flag is raised; the black and green dots represent the pressure values available in the FIFO when the flag is raised; the green dot represents the latest pressure measurement added to the FIFO when the flag is raised.

### Battery pressure monitor sensor

## 6.5.3 Description of the relative threshold option

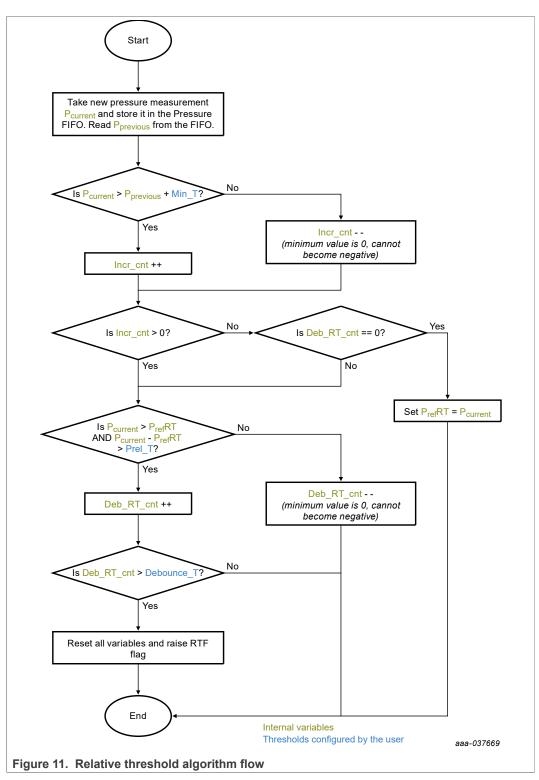

The relative threshold option is enabled when bit PCCFG\_RTEN is set. The algorithm monitors pressure rising, and whether the pressure increase has exceeded the threshold set by the user. To check for pressure rise, the current pressure measurement  $P_{current}$  is compared with the previous measurement  $P_{previous}$ : the current measurement must be greater than the previous one, by the number of counts Min\_T, configurable by the user. This check is to ensure that pressure is actually increasing, and that an increase of the pressure value is not due to sensor drift only. When pressure is increasing, that is, when  $P_{current} > P_{previous} + Min_T$ , a counter Incr\_cnt is incremented. It is decremented otherwise.

If pressure has been rising, the pressure increase  $\Delta P = P_{current} - P_{ref}$  is compared with the user threshold Prel\_T. If greater, the counter Deb\_RT\_cnt is incremented. Otherwise, Deb\_RT\_cnt is decremented. When Deb\_RT\_cnt is greater than the user threshold Debounce\_T, a flag is raised.

If both the Deb\_RT\_cnt and Incr\_cnt are equal to 0, the current pressure value  $P_{current}$  is set as the reference value  $P_{ref}$ .

The purpose of Deb\_RT\_cnt is to make sure that the flag is raised only after the condition has been met for a minimum number of samples. This filtering avoids the possibility of a false-alarm occurring when a single-measurement meets the condition due to a coincidental event, such as noise, affecting the measurement.

The algorithm flow is shown in Figure 11.

## Battery pressure monitor sensor

The variables and thresholds used in the flow are described below:

- P<sub>current</sub>: variable internal to the NBP8 program that holds the latest pressure measurement.

- P<sub>previous</sub>: variable internal to the NBP8 program that holds the previous pressure measurement.

- P<sub>ref</sub>RT: variable internal to the NBP8 program that stores the last pressure value before the pressure started to rise.

- Min\_T: user-configurable threshold that defines the minimum number of counts by which the current pressure value must exceed the previous pressure value, for the NBP8 program to consider that the pressure is rising. The value is stored in PCMINT register.

- Incr\_cnt: variable internal to the NBP8 incremented when pressure is rising, and decremented otherwise.

- Prel\_T: user-configurable threshold. When pressure is rising, the pressure increase ΔP = P<sub>current</sub> P<sub>ref</sub>RT is compared with Prel\_T. If the pressure increase exceeds Prel\_T, the debounce counter is incremented. It is decremented otherwise The value is stored in PCRELTH/L registers.

- Deb\_RT\_cnt: counter internal to the NBP8 program incremented when the pressure increase exceeds the Prel\_T. If pressure is still rising but the pressure increase remains below Prel\_T, Deb\_RT\_cnt is decremented. When the counter reaches 0, it cannot be further decremented.

- Debounce\_T: user-configurable threshold. When the value in Deb\_RT\_cnt exceeds this threshold, the pressure increase is considered to be consistently above Prel\_T, so the RTF flag is raised and external host notified. The value is stored in PCDEBT register.

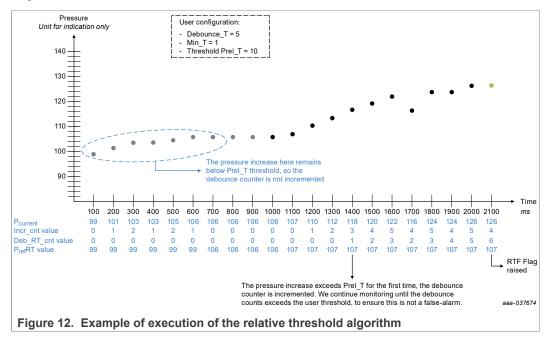

Figure 12 shows an example algorithm execution. In this example, the sample rate is set to 100 ms. The pressure FIFO depth is 12 measurements; the gray dots represent the pressure values not available in the FIFO anymore when the flag is raised; the black and green dots represent the pressure values available in the FIFO when the flag is raised; the green dot represents the latest pressure measurement added to the FIFO when the flag is raised.

## 6.5.4 Description of the rate of change threshold option

This option is enabled when PCCFG\_STEN is enabled. When a new measurement  $P_{current}$  is taken, it is compared with the previous value  $P_{previous}$ . The current measurement must be greater than the previous one, by the number of counts Min\_T,

configurable by the user, to consider that the pressure is rising. This check is to ensure that pressure is actually increasing, and that an increase of the pressure value is not due to sensor drift only. When pressure is increasing, that is, when  $P_{current} > P_{previous} + Min_T$ , the counter Deb\_ST\_cnt is incremented. It is decremented otherwise. When Deb\_ST\_cnt exceeds the threshold value Debounce\_T set by the user, the Slope =  $\Delta pressure/\Delta time$  is calculated and compared with the threshold Slope\_T configured by the user. If Slope > Slope T then a flag is raised.

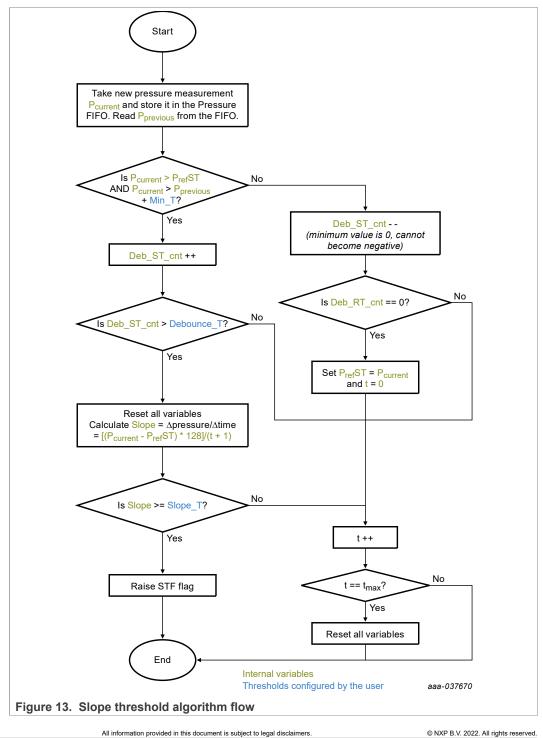

The algorithm flow is shown in Figure 13.

The different variables and thresholds correspond to the following:

- P<sub>current</sub>: variable internal to the NBP8 program that holds the latest pressure measurement. Pressure measurements are taken at a sample rate configured by the user.

- P<sub>previous</sub>: variable internal to the NBP8 program that holds the previous pressure measurement.

- P<sub>ref</sub>ST: variable internal to the NBP8 program that stores the last pressure value before the pressure started to rise.

- t: 16-bit variable internal to the NBP8 that is incremented periodically at the pressure sample rate when the pressure has been rising (that is, when Deb\_ST\_cnt is greater than 0) to keep track of the number of sampling periods during which pressure has been rising.

If t value reaches its maximum value 65535, the pressure has been increasing over the last 65535 sampling periods but the Debounce counter has not reached the Debounce threshold. Reaching a t value of 65535 only happens if the Debounce threshold is set to a very high value and pressure increases extremely slowly. When such a situation occurs, the process resets in order to avoid rollover and a potentially incorrect slope calculation.

- Min\_T: user-configurable threshold that defines the minimum number of counts by which the current pressure value must exceed the previous pressure value, for the NBP8 program to consider that the pressure is rising. The value is stored in PCMINT register.

- Deb\_ST\_cnt: counter internal to the NBP8 program updated every time a new pressure measurement is taken. The counter is incremented if the pressure is considered to be increasing, following the condition described above. It is decremented otherwise. When the counter reaches 0, it cannot be further decremented.

- Debounce\_T: user-configurable threshold. The value is stored in PCDEBT register. When the value in Deb\_ST\_cnt exceeds this threshold, the pressure increase is considered consistent and the slope of pressure versus time is calculated to check whether the pressure increase should be notified to the external host.

- Slope: variable internal to the NBP8 program that holds the value of the scaled slope  $(P_{current} P_{ref}) * 128 / (t+1)$ . The coefficient 128 provides improved precision in the slope calculation since all

- calculations are computed with integer values. Examples of slope calculation are provided in the description of the PCSLOPETH/L registers. Slope\_T: user-configurable threshold. The value is stored in PCSLOPETH/L registers. When the value in Slope exceeds this threshold, the pressure increase is considered

- When the value in Slope exceeds this threshold, the pressure increase is considered significant and the NBP8 raises the Pressure Change Detection flag before notifying to the external host that an event requiring attention occurred.

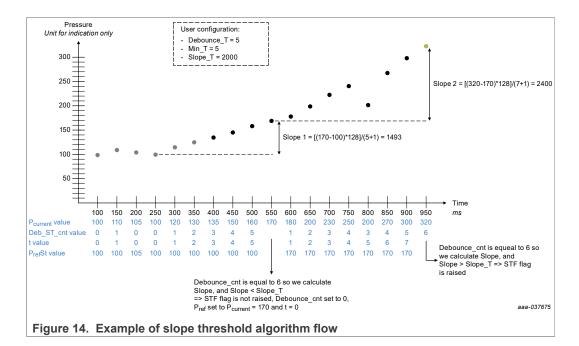

Figure 14 shows an example algorithm execution. In this example, the sample rate is set to 50 ms. The Pressure FIFO depth is 12 measurements; the gray dots represent the pressure values not available in the FIFO anymore when the flag is raised; the black and green dots represent the pressure values available in the FIFO when the flag is raised; the green dot represents the latest pressure measurement added to the FIFO when the flag is raised.

## Battery pressure monitor sensor

## 6.5.5 Description of the pressure FIFO

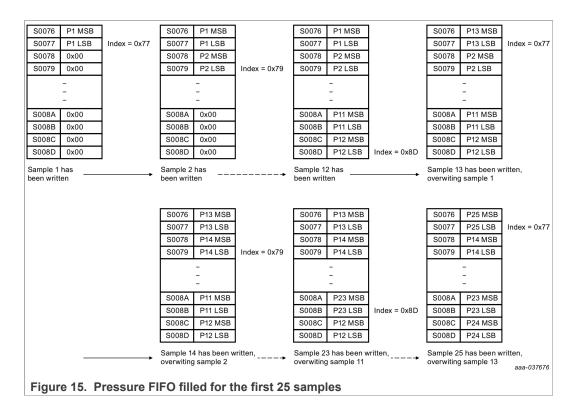

The last twelve pressure measurements are stored in the pressure FIFO. Pressure measurements are stored on two bytes, so the FIFO depth is 24 bytes. The FIFO is implemented as a rolling buffer: the most recent pressure measurement overwrites the oldest one. An 8-bit index INDFIFO holds the value of the last address written.

The FIFO starts at address \$0076 and ends at address \$008D. Addresses that have not yet been written contain the value 0x00. Measurements are written from the lower to the higher addresses, Most Significant Byte first. When the highest address has been written, the next sample is written at the lowest address.

Figure 15 shows how the program fills FIFO, for the first 25 samples. The index value after the sample Pn - the nth sample - has been written is also indicated.

## 6.6 SPI transfer sequence

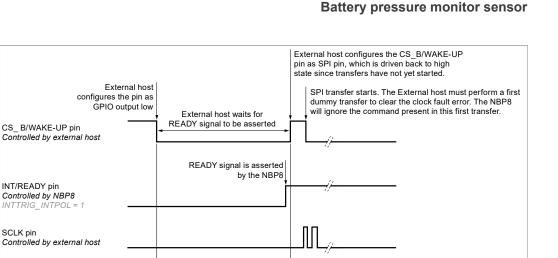

## 6.6.1 SPI transfer requested by the external host via the WAKE-UP pin

At any time, the external host can request SPI communication by lowering the WAKE-UP pin, which triggers an interrupt on the NBP8 side. When the NBP8 is ready for the transfers, it asserts the READY pin. The polarity of the READY/INT pin is configured with the bit INTTRIG\_INTPOL. After asserting the READY pin, the NBP8 writes in the SPIOPS register to halt itself, in order to avoid any memory access contention with the SPI server. Note that the NBP8 remains halted for a maximum of 2048 ms (SPI timeout), so the duration of the transfers should not exceed this time. The SPI server should poll the READY pin and start the SPI transfers only after this pin was asserted by the NBP8. During the SPI transfers, the SPI server can perform read and write access to the NBP8 memory. The list of addresses relevant for the application is given later in this document.

If the status of the SPI transfer corresponds to "internal bus contention fault", the external host must recognize that it has started the SPI transfers while the NBP8 was generating the pulse on the INT pin. If such event occurs, the External MCU should wait for the INT pin to come back to idle state before resuming the SPI transfers.

If the NBP8 wakes up from the CS\_B being driven low and then back to high state by the external host, the SPI status indicates the clock fault status due to the missing SCLK cycles. Therefore, the external host must treat the first command as a dummy to clear the SPI error status. Normal responses will remain after the first successful SPI command.

When the SPI server has completed all read and write accesses, it should perform a last write access to the NBP8 memory in order to clear the SPIOPS register. After the register has been cleared, the NBP8 resumes operation and drives the READY pin to inactive state before disabling the SPI block. If the SPI server does not clear the SPIOPS register, the NBP8 will automatically resume operations after the timeout duration.

Important note: Figure 16 shows that the CS\_B / WAKE-UP pin is held low by the external host from the moment the external host lowers the pin to request a transfer, until the end of the first SPI transfer. In reality, the actual sequence implemented by the external host may be different, taking into account the possible software implementation described below.

To trigger the transfer request, the external host application may configure the CS\_B / WAKE-UP pin as GPIO output low, and hold the pin in low state while polling the NBP8 READY pin. When the READY pin is asserted by the NBP8, the external host can start the SPI transfers. To start the transfers, the external host application must configure the CS\_B / WAKE-UP signal as an SPI CS\_B function. At that moment, the SPI transfers have not yet started and the CS\_B / WAKE-UP must be driven back to high state by the external host hardware SPI block, before being driven low again when the first transfer starts.

The sequence means there may be a duration during which the CS\_B / WAKE-UP pin is driven to low state and then back to high state again, before the SPI transfers start, as illustrated in Figure 17 below. The NBP8 logic considers this duration as a failed SPI transfer due to a clock fault error (CS\_B pin lowered but no SCLK signal). After generating a clock fault error, the NBP8 needs one 16-bit transfer to clear the error before continuing normal operations. Consequently, the command inside the first 16-bit transfer performed by the external host is ignored by the NBP8. The first transfer is used by the NBP8 to clear the clock fault error only. So, the external host has to consider the first transfer to be a dummy transfer, during which the command is not taken into account. It is only from the second transfer that the READ or WRITE commands are processed by the NBP8.

SCLK pin

## 6.6.2 SPI transfer requested by the NBP8, when an event requiring attention occurred

Figure 17. Sequence leading to a clock fault error on the NBP8 side

The NBP8 considers the time during which the CS\_B/WAKE-UP was low as a failed SPI transfer (clock fault error) since the CS B pin was held low but no SCLK signal was detected.

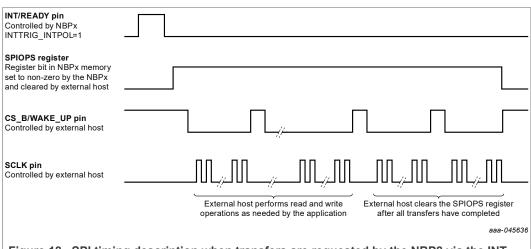

When an event requiring attention has occurred, the NBP8 notifies the external host in order to establish SPI communication. For that, the NBP8 first enables SPI and then generates a pulse on the INT pin. If PS ENABLE pin is enabled in the PINCFG register, the NBP8 asserts PS ENABLE pin and waits 200 ms before generating the pulse on the INT pin. The polarity and duration of the pulse are configured with INTTRIG INTPOL and INTTRIG INTDUR bits. Following the pulse, the NBP8 writes in the SPIOPS register to halt itself, in order to avoid any memory access contention with the SPI server. Note that the NBP8 remains halted for a maximum of 2048 ms (SPI timeout), so the duration of the transfers should not exceed this time. The SPI server should poll the INT pin and start the SPI transfers only after the pulse ended, so after this pin was driven back to idle state by the NBP8. During the SPI transfers, the SPI server can perform read and write access to the NBP8 memory. The list of addresses relevant for the application is given later in this document. Typically, the external host would start by reading the STATUS register in order to know the origin of the event. The external host must set the CMD ACKINTF bit to acknowledge the flags, which will be cleared by the NBP8 after completion of the SPI transfers.

When the SPI server has completed all read and write accesses, it should perform a last write access to the NBP8 memory in order to clear the SPIOPS register. After the register has been cleared, the NBP8 resumes operation. If the SPI server does not clear the SPIOPS register, the NBP8 will automatically resume operations after the timeout duration.

The timing is shown in Figure 18.

NBP8

NRP8

aaa-038553

## **NXP Semiconductors**

# NBP8

## Battery pressure monitor sensor

# Figure 18. SPI timing description when transfers are requested by the NBP8 via the INT pin, with INTTRIG\_INTPOL=1

#### Figure 19 shows the case where PS ENABLE pin is enabled.

| PS ENABLE pin<br>Optionally controlled by NBP8<br>PINCFG_PTB1CFG=5 -                                             |        |                                                   |                                             |                |        |

|------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|---------------------------------------------|----------------|--------|

| INT/READY pin<br>Controlled by NBP8<br>INTTRIG_INTPOL=1 -                                                        | 200 ms |                                                   |                                             |                |        |

| SPIOPS register<br>Register bit in NBP8 memory<br>set to non-zero by the<br>NBP8 and cleared by<br>external host |        |                                                   |                                             |                |        |

| CS_B/WAKE_UP pin<br>Controlled by external host                                                                  |        |                                                   |                                             |                |        |

| SCLK pin<br>Controlled by external host                                                                          |        |                                                   |                                             |                |        |

|                                                                                                                  |        | erforms read and write<br>eded by the application | External host clears<br>after all transfers | have completed |        |

|                                                                                                                  |        |                                                   |                                             | aaa-C          | 037678 |

| Figure 19. SPI timi<br>pin, with PINCFG_I                                                                        | · ·    | -                                                 | d by the NBP8                               | via the INT    |        |

## 6.7 Typical sequence timings

## 6.7.1 Periodic events

<u>Figure 20</u> illustrates a sequence of periodic events. The sampling period configured in the PSP register corresponds to the execution time of the sensor measurements, pressure change algorithm(s) execution, and sleep duration. The available sampling periods are achieved by adjusting the sleep time.

The execution time of the periodic ADC and Pcell Self-Test is not included in the sampling period. The duration of the Self-Test is indicated at the end of this section. The power consumption of sensor measurements is indicated in <u>Table 51</u>.

|        | Sensors<br>meas. | Pressure<br>Change<br>Algo | Sleep     | Periodic<br>Self-Test<br>(ADC and Pcell) | Sensors<br>meas. | Pressure<br>Change<br>Algo | Sleep | Sensors<br>meas. | Pressure<br>Change<br>Algo | Sleep |            |

|--------|------------------|----------------------------|-----------|------------------------------------------|------------------|----------------------------|-------|------------------|----------------------------|-------|------------|

| - 1/   | Low<br>power     | RUN                        | STOP1     | RUN                                      | Low<br>power     | RUN                        | STOP1 | Low<br>power     | RUN                        | STOP1 | -//        |

|        | SAM              | PLING PER                  | RIOD      | SELF-TEST EXE                            | SAMPLING PERIOD  |                            |       |                  |                            |       |            |

| Figure | e 20. Se         | quence                     | e of peri | odic events                              |                  |                            |       |                  |                            |       | aaa-037683 |

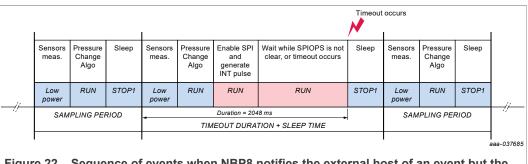

## 6.7.2 NBP8 notifying the external host

<u>Figure 21</u> and <u>Figure 22</u> illustrate a sequence of periodic events during which the NBP8 notifies the External host that an event requiring attention has occurred. When such an event occurs, the NBP8 generates a pulse on the INT pin and then waits until either the External host clears the SPIOPS register via SPI or the 2048 ms timeout period expires.

In the first example, the External host clears the SPIOPS during the last SPI transfer. The NBP8 then executes the commands that have been configured by the External host in the CMD register.

The duration of the INT pulse is configured by the user with the INTTRIG\_INTDUR bit. The time during which the NBP8 waits after generating the INT pulse depends on the time needed by the External host to start the SPI transfers and the duration of the SPI transfers, which itself depends on the SPI baud rate configured on the external host side and the number of transfers performed. The execution time of the commands performed by the NBP8 is indicated at the end of this section. The duration of the Self-Test is indicated at the end of this section. The power consumption of sensor measurements is indicated in Table 51.

|   | External host performs<br>SPI transfers. The last<br>transfers clears SPIOPS |                            |       |                  |                            |                                            |                                                               |                       |                 |                  | 1                          |       |            |

|---|------------------------------------------------------------------------------|----------------------------|-------|------------------|----------------------------|--------------------------------------------|---------------------------------------------------------------|-----------------------|-----------------|------------------|----------------------------|-------|------------|

| 4 | Sensors<br>meas.                                                             | Pressure<br>Change<br>Algo | Sleep | Sensors<br>meas. | Pressure<br>Change<br>Algo | Enable SPI<br>and<br>generate<br>INT pulse | Wait while<br>SPIOPS is<br>not clear, or<br>timeout<br>occurs | Commands<br>execution | Sleep           | Sensors<br>meas. | Pressure<br>Change<br>Algo | Sleep |            |

|   | Low<br>power                                                                 | RUN                        | STOP1 | Low<br>power     | RUN                        | RUN                                        | RUN                                                           | RUN                   | STOP1           | Low<br>power     | RUN                        | STOP1 |            |

|   | SAM                                                                          | IPLING PEI                 | RIOD  | <b>→</b> Th      |                            | annot exceed 20                            | 48 ms                                                         |                       | SAMPLING PERIOD |                  |                            |       |            |

|   | I                                                                            |                            |       | I                |                            |                                            |                                                               |                       |                 | I                |                            |       | aaa-037684 |

Figure 21. Sequence of events when NBP8 notifies the external host of an event and the external host clears the SPIOPS register

The second example illustrates the sequence of events when the external host does not clear the SPIOPS register via SPI. In that case, the NBP8 exits the waiting state on timeout before entering the sleep state. Note that in this situation, the NBP8 does not execute the potential commands that could have been written in the CMD register. This is because exiting on timeout is not the expected sequence of events, indicating that a problem occurred on the external host side.

Figure 22. Sequence of events when NBP8 notifies the external host of an event but the external host does not clear the SPIOPS register

## 6.7.3 External host requesting an SPI transfer

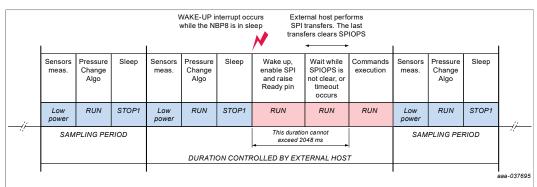

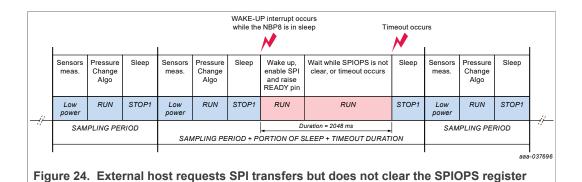

<u>Figure 23</u> and <u>Figure 24</u> illustrate a sequence of periodic events during which the external host triggers an interrupt on the NBP8 side via the WAKE-UP pin in order to request SPI transfers.

If the WAKE-UP interrupt is triggered while the NBP8 is in the sleep state (as in the example below), the NBP8 wakes up immediately, enables SPI, and raises the READY pin. That series of events (wake up, enable SPI, and raise the READY pin) takes 125 µs.

If the WAKE-UP interrupt is triggered while the NBP8 performs sensor measurements, self-test, or any of the actions triggered by the CMD register, the NBP8 first completes the ongoing action before enabling SPI, and raising the READY pin. Raising the READY pin can take up to 8 ms (or up to 132 ms, if the NBP8 if performing firmware verification).

In the first example, the external host clears the SPIOPS register during the last SPI transfer. After exiting the wait state, the NBP8 executes the commands configured by the external host in the CMD register before continuing the periodic sequence of events.

Figure 23. External host requests SPI transfers and then clears the SPIOPS register

In the second example, the external host does not clear the SPIOPS register during the SPI transfers, so the NBP8 exits the wait state on timeout before entering the sleep state. Note in this situation, the NBP8 does not execute the potential commands that could have been written in the CMD register due to exiting on timeout. The timeout indicates that a problem occurred on the external host side.

## 6.7.4 Summary of execution times

<u>Table 7</u> summarizes the execution times of the different actions. Sensor measurements include raw pressure, raw temperature, and raw voltage readings, followed by pressure, temperature, and voltage compensations.

| Action                    | Periodic/Triggered       | Duration |

|---------------------------|--------------------------|----------|

| Sensor measurements       | Periodic                 | 4.4 ms   |

| Pressure change algorithm | Periodic                 | 100 µs   |

| ADC and Pcell self-test   | Periodic                 | 3.47 ms  |

| ADC self-test             | Triggered by CMD_ADCST   | 455 μs   |

| Pcell self-test           | Triggered by CMD_PST     | 3.32 ms  |

| Firmware verification     | Triggered by CMD_FV      | 132 ms   |

| Reset registers           | Triggered by CMD_RESET   | 206 µs   |

| Clear FIFO                | Triggered by CMD_CLRFIFO | 185 µs   |

| Acknowledge INTF          | Triggered by CMD_ACKINTF | 18 µs    |

Table 7. Summary of execution times

## 6.8 Read/write targets accessible by the external host via SPI

This section details the addresses of the NBP8 accessible by the external host via SPI.

Table 8. Read and write addresses summary

| Address | Name      | Bit 7    | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2            | Bit 1       | Bit 0    |  |  |

|---------|-----------|----------|------------|----------|----------|----------|------------------|-------------|----------|--|--|

| \$0038  | SPIOPS    | reserved | reserved   | reserved | reserved | reserved | CORE_<br>TR_HOLD | reserved    | reserved |  |  |

| \$0050  | PSP       |          | PSP[7:0]   |          |          |          |                  |             |          |  |  |

| \$0051  | STPER     |          | STPER[7:0] |          |          |          |                  |             |          |  |  |

| \$0052  | PINCFG    | reserved | reserved   | reserved | reserved | reserved |                  | PINCFG[2:0] |          |  |  |

| \$0053  | INTTRIG   | reserved | reserved   | INTPOL   | INTDUR   | FVERR    | STERR            | SENSERR     | SENSRDY  |  |  |

| \$0054  | PCCFG     | reserved | reserved   | reserved | reserved | reserved | STEN             | RTEN        | FTEN     |  |  |

| \$0055  | STATUS    | INTF     | PCSTF      | PCRTF    | PCFTF    | FVF      | PSTF             | ADCSTF      | SENSF    |  |  |

| \$0056  | SENSTATUS | ADCERR   | LVW        | POVER    | PUNDER   | TOVER    | TUNDER           | VOVER       | VUNDER   |  |  |

| \$0057  | CMD       | ACKINTF  | reserved   | reserved | CLRFIFO  | RESET    | FV               | PST         | ADCST    |  |  |

© NXP B.V. 2022. All rights reserved.

## Battery pressure monitor sensor

| Address                | Name                                                                       | Bit 7 | Bit 6          | Bit 5                              | Bit 4  | Bit 3    | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|------------------------|----------------------------------------------------------------------------|-------|----------------|------------------------------------|--------|----------|-------|-------|-------|--|--|--|

| \$0058                 | PCDEBT                                                                     |       |                |                                    | PCDEI  | 3T[7:0]  |       |       |       |  |  |  |

| \$0059                 | PCFIXTH                                                                    |       |                |                                    | PCFIX  | T[15:8]  |       |       |       |  |  |  |

| \$005A                 | PCFIXTL                                                                    |       |                |                                    | PCFIX  | (T[7:0]  |       |       |       |  |  |  |

| \$005B                 | PCMINT                                                                     |       |                |                                    | PCMI   | NT[7:0]  |       |       |       |  |  |  |

| \$005C                 | PCRELTH                                                                    |       |                | PCRELT[15:8]                       |        |          |       |       |       |  |  |  |

| \$005D                 | PCRELTL                                                                    |       | PCRELT[7:0]    |                                    |        |          |       |       |       |  |  |  |

| \$005E                 | PCSLOPETH                                                                  |       | PCSLOPET[15:8] |                                    |        |          |       |       |       |  |  |  |

| \$005F                 | PCSLOPETL                                                                  |       |                |                                    | PCSLO  | PET[7:0] |       |       |       |  |  |  |

| \$0070:                | TCODE                                                                      |       |                |                                    | TCOD   | E[7:0]   |       |       |       |  |  |  |

| \$0071                 | VCODE                                                                      |       |                |                                    | VCOD   | E[7:0]   |       |       |       |  |  |  |

| \$0075                 | INDFIFO                                                                    |       |                |                                    | INDFIF | O[7:0]   |       |       |       |  |  |  |

| \$0076<br>to<br>\$008D | PFIFOH<br>1[15:8]<br>PFIFOL1[7:0]<br>to<br>PFIFOH12[15:8]<br>PFIFOL12[7:0] |       |                | PFIFO1[15:0] through PFIFO12[15:0] |        |          |       |       |       |  |  |  |

#### Table 8. Read and write addresses summary...continued

## The detail of the read/write targets is given below.

## Table 9. SPI Operations (SPIOPS) (address 0x0038)

| Bit                     | 7    | 6    | 5    | 4    | 3    | 2                    | 1    | 0    |

|-------------------------|------|------|------|------|------|----------------------|------|------|

| R/W                     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | CORE_<br>TR_<br>HOLD | Bit1 | Bit0 |

| POR or User Reset (\$0) | 0    | 0    | 0    | 0    | 0    | 0                    | 0    | 0    |

## Table 10. SPIOPS fields description

| Fields         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |