## Avocet HDR Image Sensors Datasheet

#### **Features and Benefits**

| 1024 x 512 pixels CMOS image sensor        |

|--------------------------------------------|

| 154dB Extended HDR                         |

| Lancarda a lancara anno dell'ara also de d |

- □ Low noise, low power rolling shutter□ 1/3" Optical format for 1024x512

- □ 1/4" Optical format with VGA subwindow

- Monochrome, RCCC, Standard Bayer (RGBG) or special Bayer (RGBi)

- □ Parallel data output

- 8/10/12 bits + CLK/HSYNC/VSYNC

- Operating Temperature Range: -40C to +85 ℃ full performance -40C to +115 ℃ reduced performance

- ☐ Storage Temperature Range: -40 °C to +125 °C

- □ Automotive Qualified AEC-Q100

## **Application Examples**

- □ Advanced Driver Assistance Systems (ADAS)

- ☐ Lane departure warning (LDW)

- ☐ Forward collision warning (FCW)

- Automatic high-beam assist

- ☐ Pedestrian Detection for Autonomous Emergency Braking (AEB)

- ☐ Cameras on trucks, trains, busses, emergency vehicles, agricultural vehicles, autonomous vehicles, heavy off-road vehicles

- Night vision cameras

- HDR surveillance cameras

- □ Traffic monitoring cameras

- □ Fleet Safety/ Black-box cameras

## **Additionally for MLX75412**

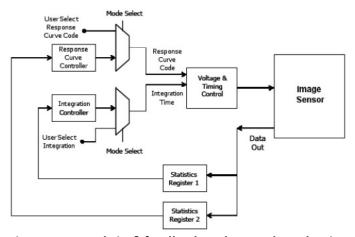

- On-chip Autobrite® auto-exposure (AE) and auto-HDR. This high performing function automatically sets the best exposure and HDR setting on a frame by frame basis.

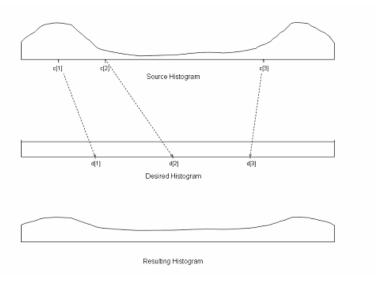

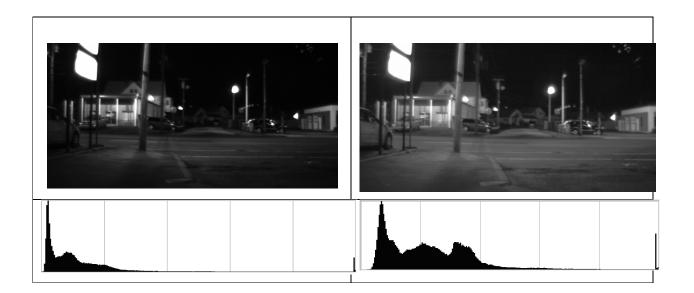

- □ On-chip Autoview<sup>TM</sup> histogram remapping. This function optimizes 8 bit performance, for display-based applications for example.

## **Ordering Information**

Ordering code: Part No. - Temperature Code & Package Code - Option code - Packaging code

☐ Package Code: TF (glass-BGA) or UC (wafer)

☐ Option Code: MAA-000 (monochrome version) or

RAA-000 (RCCC version) or

RAA-000 (RCCC version) or GAA-000 (RGBG version) or IAA-000 (RGBi version)

☐ Packaging Code: TR (for Glass-BGA parts) or WB (for wafers)

Example: MLX75412 - VTF-MAA-000-TR

## Avocet HDR Image Sensors Datasheet

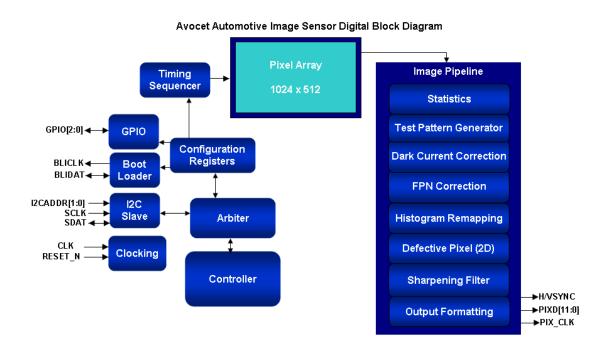

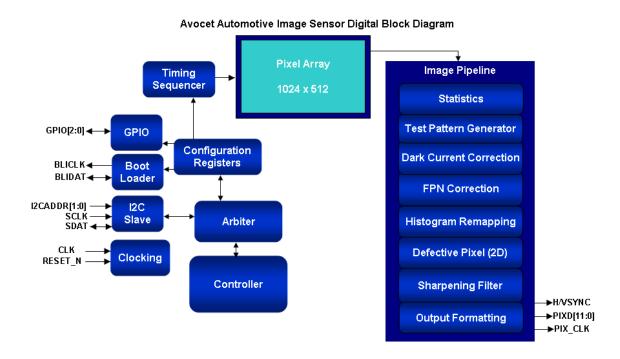

## 1 Functional Diagram

## 2 General Description

The Avocet image sensor integrates a high-sensitivity array, a feature-rich digital processor for monochrome images and camera control functions into a single chip.

In a monochrome system, image processing is performed on the Avocet as a single chip solution.

In a color system Avocet acts as a slave in a system controlled by a separate Image Signal Processor chip through one of the external interfaces delivering raw single images or video-like streams of color Bayer-patterned images. The sensor captures the images at the required speed, exposure, and gain, and the external device is responsible for all further image processing such as color demosaicing and white balance.

## Avocet HDR Image Sensors Datasheet

## Table of Contents

| 2 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ;                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

| 3 Glossary of Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      |

| 4 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| 5 Pin Definitions and Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

| 6 General Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      |

| 7 Sensor Specific Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

| 8 Device Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| 8.1 Avocet Sensor Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| 8.2 Sensor Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| 8.3 Pixel Array Description & Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | اا                                                                                                                   |

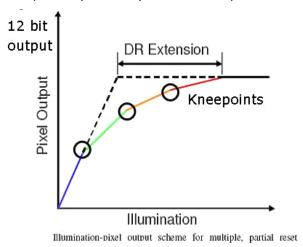

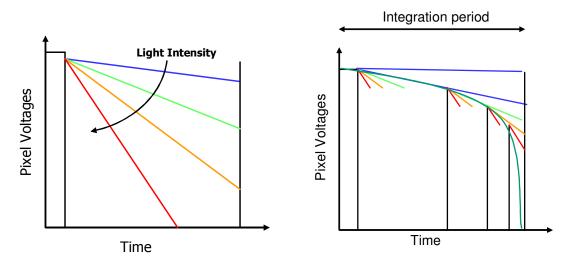

| 8.4 Avocet Extended High Dynamic Range Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

| 8.5 On-chip Algoritms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

| 8.5.1.1 Autobrite® Automatic Mode Feedback Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

| 8.5.1.2 Autobrite® Advantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |

| 8.5.2 Autoview™ Histogram Optimization (MLX75412 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                                                                   |

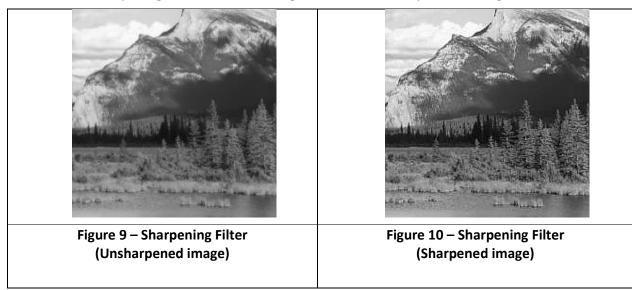

| 8.5.3 Spatial Filtering: Sharpening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                    |

| 8.6 Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                                                                   |

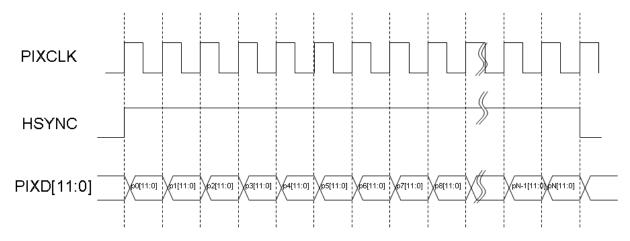

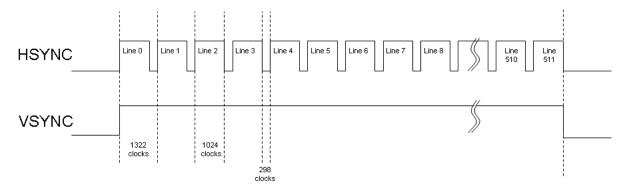

| 8.6.1 Pixel data output interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                                                                   |

| 8.6.1.1 12/10/8 bit digital video mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

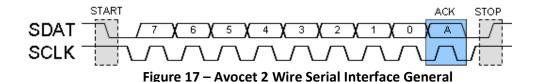

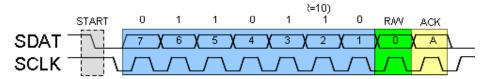

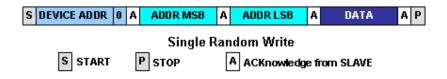

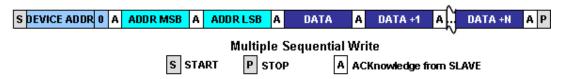

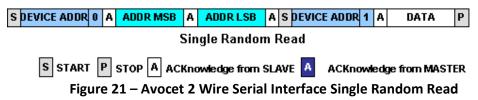

| 8.6.2 Two Wire Serial Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

| 8.6.3 Two Wire Boot Loader Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                                                                                                                   |

| 8.7 Device power up behavior and initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                                                                                   |

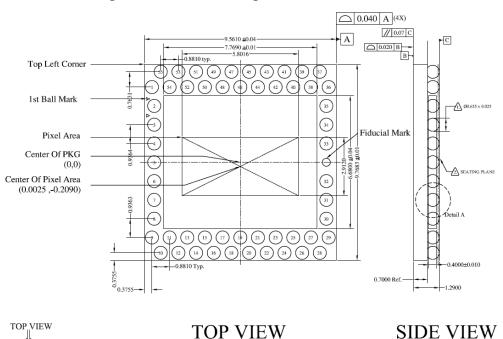

| 9 55-pin Glass-BGA package information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                    |

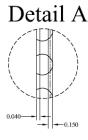

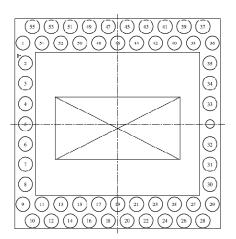

| 9.1 GBGA55 Mechanical Drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

| 9.1.1 Package mechanical drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                    |

| 9.1.2 Package ball coordinates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                                                                    |

| 9.2 Solder recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2:                                                                                                                   |

| 9.2.1 Recommended Solder materials & procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

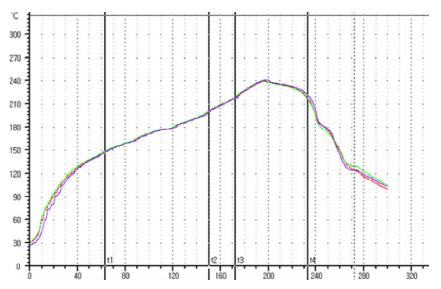

| 9.2.2 Solder profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                    |

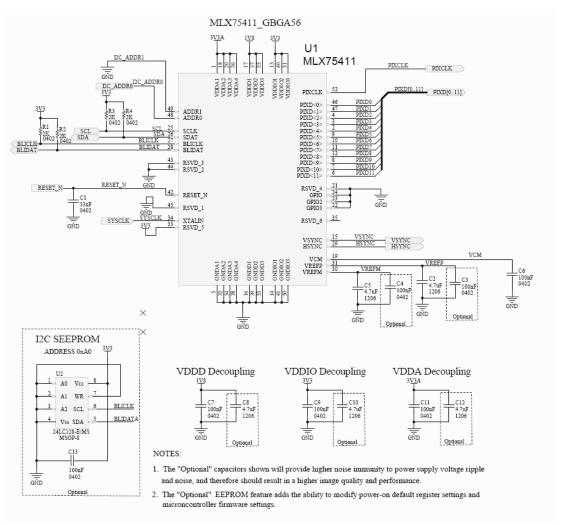

| 10 Board design guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                   |

| 10.1 Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| 10.1.1 Unused Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

| 10.1.2 External Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| 10.1.3 Series Termination Resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                    |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                    |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2!<br>20                                                                                                             |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>20                                                                                                             |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2!<br>                                                                                                               |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20                                                             |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>20<br>20<br>20<br>20<br>21<br>20<br>21<br>20<br>21                                                             |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20<br>20<br>21<br>22<br>22<br>21<br>22<br>23<br>24                                                                   |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>20<br>22<br>22<br>22<br>21<br>21<br>21<br>22<br>33                                                             |

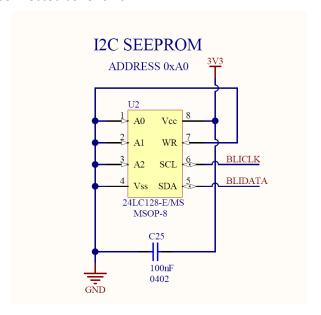

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.0 Slave I2C interface and Master Boot Loader Interface 10.2 Typical Application Circuit 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface PROM part specification PROM connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20<br>22<br>22<br>22<br>22<br>22<br>22<br>21<br>23<br>33<br>33<br>33                                                 |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 22 22 22 22 23 33 33 33 33 33 33                                                                                  |

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.0 Slave I2C interface and Master Boot Loader Interface. 10.2 Typical Application Circuit. 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface. PROM part specification PROM connections. 13 Appendix C: Control Registers 13.1 Common Tasks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20<br>22<br>22<br>22<br>22<br>22<br>24<br>22<br>23<br>33<br>33<br>33<br>33                                           |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20<br>22<br>22<br>22<br>22<br>22<br>24<br>33<br>33<br>33<br>33<br>33<br>33                                           |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20<br>22<br>22<br>22<br>22<br>22<br>23<br>33<br>33<br>33<br>33<br>33<br>33                                           |

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.0 Slave I2C interface and Master Boot Loader Interface 10.2 Typical Application Circuit 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface PROM part specification PROM connections 13 Appendix C: Control Registers 13.1 Common Tasks 13.1.1 How to determine the revision of the hardware and the firmware 13.1.2 How to disable/enable image processing functions 13.1.3 How to control Autobrite autoexposure and dynamic range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20<br>22<br>22<br>22<br>22<br>22<br>24<br>33<br>33<br>33<br>33<br>33<br>33<br>33                                     |

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.10 Slave I2C interface and Master Boot Loader Interface. 10.2 Typical Application Circuit 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface. PROM part specification PROM connections. 13 Appendix C: Control Registers 13.1 Common Tasks 13.1.1 How to determine the revision of the hardware and the firmware 13.1.2 How to disable/enable image processing functions 13.1.3 How to control Autobrite autoexposure and dynamic range 13.1.4 How to control Autobrite autoexposure and dynamic range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>33<br>33<br>33<br>33<br>33<br>33                                     |

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.0 Slave I2C interface and Master Boot Loader Interface. 10.2 Typical Application Circuit 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface. PROM part specification PROM connections. 13 Appendix C: Control Registers 13.1 Common Tasks 13.1.1 How to determine the revision of the hardware and the firmware 13.1.2 How to disable/enable image processing functions 13.1.3 How to control Autobrite autoexposure and dynamic range 13.1.4 How to disable the automatic exposure control (Autobrite)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 22 22 22 22 23 33 33 33 33 33 33 33 33                                                                            |

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.0 Slave I2C interface and Master Boot Loader Interface. 10.2 Typical Application Circuit 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface. PROM part specification PROM connections. 13 Appendix C: Control Registers 13.1 Common Tasks 13.1.1 How to determine the revision of the hardware and the firmware 13.1.2 How to disable/enable image processing functions 13.1.3 How to control Autobrite autoexposure and dynamic range 13.1.4 How to control Autobrite autoexposure and dynamic range 13.1.5 How to disable the automatic exposure control (Autobrite) 13.1.6 How to set a specific frame rate                                                                                                                                                                                                                                                                                                                                                                                                 | 20 22 22 22 22 23 33 33 33 33 33 33 33 33                                                                            |

| 10.1.4 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 22 22 22 22 23 33 33 33 33 33 33 33 33                                                                            |

| 10.1.4 Power Supplies 10.1.5 Grounds 10.1.6 Power Supply Decoupling 10.1.7 Power Supply Sequencing 10.1.8 Digital Signal Interconnect 10.1.9 Analog Signal Interconnect 10.1.10 Slave I2C interface and Master Boot Loader Interface 10.2 Typical Application Circuit 11 Appendix A: Control protocol 12 Appendix B: Use of the 2 wire boot loader interface PROM part specification PROM connections 13 Appendix C: Control Registers 13.1 Common Tasks 13.1.1 How to determine the revision of the hardware and the firmware 13.1.2 How to disable/enable image processing functions 13.1.3 How to control Autobrite autoexposure and dynamic range 13.1.4 How to control Autobrite autoexposure control (Autobrite) 13.1.5 How to disable the automatic exposure control (Autobrite) 13.1.6 How to set a specific frame rate 13.1.7 How to set up sub-windowing 13.1.8 How to control statistics collection (and Autobrite to expose) based on a sub-region of the image                                                                                                                                                                                                                                                     | 20 22 22 22 24 25 25 25 25 25 25 25 25 25 25 25 25 25                                                                |