# Bridge Signal Conditioning Interface with Analog or SENT Output

# **NCV7192**

The NCV7192 is a Signal Conditioning Interface with Analog or SENT output, capable for Automotive Safety Applications. The IC receives a differential signal from the external sensing element, conditions gain and offset with a configurable amplification stage, compensates for sensor nonlinearity and temperature dependency, and delivers the result as digital SENT or ratiometric analog output signal. A separate measurement channel linearizes and measures the resistance of an external NTC to capture a medium temperature and communicate it over the SENT interface. The integrated EEPROM is programmable over the output pin for storage of configuration settings and compensation coefficients, as well as free format customer payload data. The NCV7192 includes failure diagnostics and internal protections against shorts, overvoltage, and reverse voltage to support Safety Applications.

#### **Features**

- Resistive Bridge Impedance: 1 to 25 k $\Omega$

- Differential Input Range (S<sub>IN\_FSS</sub> + S<sub>IN\_PO</sub>): From 2 mVpk/Vbdr to 125 mVpk/Vbdr

- Integrated DSP to Compensate Bridge and Temperature Non-Linearity Using Polynomes

- Calibration Interface over OUTX Pin

- Low-noise Amplification Stage with Programmable Gain/Offset

- Temperature Measurement with Bridge Impedance or Internal Junction Diode

- Medium Temperature Measurement with External NTC

- SENT Output According to the Standard SAE J2716 (April 2016)

- Analog Output Buffer Driven by a 14-bit DAC with Programmable Clip Levels

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

# **Safety Mechanisms**

- Sensor Connectivity Error Detection

- Bridge Signal Measurement BIST

- Temperature Measurement BIST

- DSP BIST

- Analog Output Connectivity Error Detection

- SENT Connectivity Error Detection

#### **Typical Applications**

- Pressure Sensors With Piezo-resistive Bridge

- Force/torque Sensors With Resistive Strain-gauge

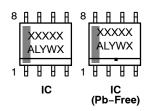

SOIC-8 NB CASE 751-07

#### **MARKING DIAGRAM**

A YYWW = Assembly Site

= Assembly Start Week

# **ORDERING INFORMATION**

See detailed ordering and shipping information on page 6 of this data sheet

# **Public Data Sheet**

**Interested in what you see?** If you would like more detailed information, please request the full version of our data sheet.

**Request Full Data Sheet**

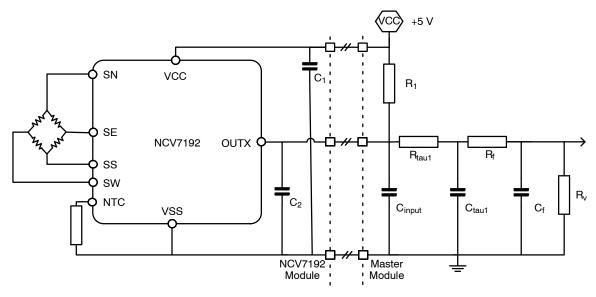

Figure 1. Application Diagram for SENT Application

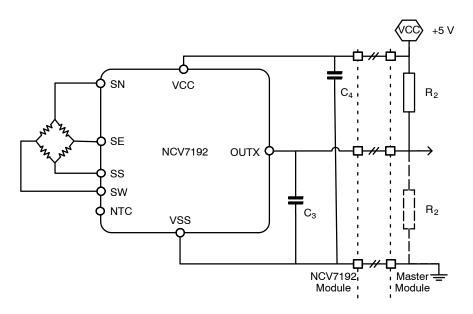

Figure 2. Application Diagram for Analog Output Application

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| Rating                                   | Symbol              | Min  | Max | Unit |

|------------------------------------------|---------------------|------|-----|------|

| VCC Supply Voltage Range                 |                     | -30  | 30  | V    |

| OUTX Pin Voltage Range                   |                     | -30  | 30  | V    |

| Sensor Pins SE, SW Voltage Range         | V <sub>SESWAM</sub> | -18  | 18  | V    |

| Sensor SN Abs Max Rating                 | V <sub>SNAM</sub>   | -18  | 18  | V    |

| Sensor in Pin SS Voltage Range           | V <sub>SSAM</sub>   | -3.6 | 3.6 | V    |

| Pin NTC Voltage Range                    | $V_{NTCAM}$         | -3.6 | 3.6 | V    |

| Storage Temperature for Packaged Devices | T <sub>st</sub>     | -55  | 150 | °C   |

| Junction Temperature under Bias          | T <sub>J</sub>      | -40  | 165 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>1.</sup> It is not implied that more than one of these ratings can be applied simultaneously

# NCV7192

# **RECOMMENDED OPERATING CONDITIONS** (Note 2)

| Rating                                                | Symbol              | Min  | Max  | Unit |

|-------------------------------------------------------|---------------------|------|------|------|

| VCC Operating Range                                   | VCC                 | 4.5  | 5.5  | V    |

| VCC Operating Range for SENT Parametrical Performance | VCC <sub>SENT</sub> | 4.85 | 5.15 | V    |

| Junction Temperature under Bias                       | $T_J$               | -40  | 165  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

2. It is not implied that more than one of these ratings can be applied simultaneously

# **APPLICATION CONDITIONS**

| Rating                                                                                              | Symbol               | Min  | Тур | Max    | Unit    |

|-----------------------------------------------------------------------------------------------------|----------------------|------|-----|--------|---------|

| Bridge Impedance                                                                                    | R <sub>BR</sub>      | 1    | -   | 25     | kΩ      |

| Ratio of Zero Signal Offset (S <sub>IN_PO</sub> ) and Sensor Full Scale Span (S <sub>IN_FSS</sub> ) | S <sub>OSFS</sub>    | -2   | -   | 2      | -       |

| Maximum Differential Input Range (S <sub>IN FSS</sub> + S <sub>IN PO</sub> )                        | S <sub>IN</sub>      | -125 | -   | 125    | mV/Vbdr |

| NTC Impedance Range for Pull-up Resistor 1                                                          | RNTC <sub>RPU1</sub> | 57   | -   | 20900  | Ω       |

| NTC Impedance Range for Pull-up Resistor 2                                                          | RNTC <sub>RPU2</sub> | 570  | -   | 209000 | Ω       |

# ELECTRICAL CHARACTERISTICS (Valid only under recommended operating conditions; unless otherwise specified)

| Parameter                                                                                                                  | Condition                                                                                           | Symbol               | Min  | Тур | Max | Unit   |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|------|-----|-----|--------|

| VCC Current Consumption (No Output Load,<br>No Sensing or NTC Element Attached, 10 ms<br>after Start-up, Gain Stage 1 ≥ 1) |                                                                                                     | l <sub>VCC</sub>     | -    | 5   | 7   | mA     |

| SUPPLY VOLTAGE MONITOR                                                                                                     |                                                                                                     |                      |      |     |     |        |

| VCC Reset Release Threshold, Supply Rising                                                                                 | (Note 3)                                                                                            | VCC <sub>PORH</sub>  | -    | -   | 4.4 | V      |

| VCC Reset Enable Threshold, Supply Falling                                                                                 | (Note 3)                                                                                            | VCC <sub>PORL</sub>  | -    | -   | 3.6 | V      |

| VCC Overvoltage Programmable Threshold Range                                                                               |                                                                                                     | VCC <sub>OV</sub>    | 5    | -   | 6   | V      |

| VCC Undervoltage Programmable Threshold Range                                                                              |                                                                                                     | VCC <sub>UV</sub>    | 4    | -   | 5   | V      |

| BRIDGE SIGNAL                                                                                                              |                                                                                                     |                      | •    |     |     |        |

| Bridge Drive Voltage V(SN) – V(SS) for a Typical 3 kΩ Bridge                                                               |                                                                                                     | $V_{	ext{bdr}}$      | -    | 3   | -   | ٧      |

| Bridge Signal Differential Input Voltage Range<br>Corresponding to Maximum ADC Input with Analog<br>Signal Gain 1          |                                                                                                     | PM <sub>ADCIN</sub>  | -200 | -   | 200 | mV     |

| Programmable Range of Typical Analog Signal<br>Gain                                                                        |                                                                                                     | $PM_GA$              | 1/2  | -   | 30  | V/V    |

| Maximum Programmable Full Signal Path Gain<br>Towards the Analog Output Channel, Digital<br>Coefficient Gain 1             | (Note 3)<br>Full Scale Output<br>Range Min = 0.5<br>Max = 4.5 V                                     | PM <sub>FPA</sub>    | -    | 600 | -   | V/V    |

| Maximum Programmable Full Signal Path Gain<br>Towards the SENT Bridge Signal Channel, Digital<br>Coefficient Gain 1        | (Note 3)                                                                                            | PM <sub>FPS</sub>    | -    | 613 | -   | kLSB/V |

| TEMPERATURE MEASUREMENT                                                                                                    | •                                                                                                   |                      |      | •   | •   |        |

| Junction Temperature Measurement (tint) Residual Error                                                                     | Temperature Range $-40~^{\circ}\text{C}$ to $+135~^{\circ}\text{C}$ , $R_{BR} > 2.5~\text{k}\Omega$ | TM <sub>ACC_A</sub>  | -3.5 | _   | 3.5 | К      |

| Junction Temperature Measurement (tint) Residual Error                                                                     | Temperature Range $-40$ °C to $+150$ °C, $R_{BR} > 2.5$ k $\Omega$                                  | TM <sub>ACC_AH</sub> | -5   | -   | 5   | К      |

| Bridge Temperature Measurement Residual Error<br>After Trim and Calibration                                                | (Notes 3, 4)                                                                                        | TM <sub>ACC_BR</sub> | -3   | _   | 3   | К      |

ELECTRICAL CHARACTERISTICS (Valid only under recommended operating conditions; unless otherwise specified) (continued)

| Parameter                                                                               | Condition                                     | Symbol                         | Min  | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------|------|-----|------|------|

| TEMPERATURE MEASUREMENT                                                                 | •                                             | •                              |      |     |      |      |

| Allowed Bridge Resistance for Temperature Measurement                                   | (Notes 3, 4)                                  | TM <sub>R_BR</sub>             | 1.2  | _   | 9.5  | kΩ   |

| SENT OUTPUT DRIVER                                                                      | •                                             |                                |      |     |      |      |

| SENT Low State Voltage                                                                  |                                               | V <sub>SENT_VOL</sub>          | -    | -   | 0.5  | V    |

| SENT High State Voltage                                                                 |                                               | V <sub>SENT_VOH</sub>          | 4.1  | -   | -    | V    |

| SENT Fall Time                                                                          | (Notes 7, 8)                                  | T <sub>SFALL</sub>             | _    | -   | 6.5  | μs   |

| SENT Rise Time                                                                          | (Notes 7, 8)                                  | T <sub>SRISE</sub>             | 1    | -   | 18   | μs   |

| SENT Edge to Edge Jitter                                                                | (Note 8)                                      | DT <sub>SJIT</sub>             | 1    | 0.1 | -    | μs   |

| First Falling Edge of the First SENT Frame after Power-up                               |                                               | OUTX <sub>S_PUP</sub>          | -    | -   | 1.1  | ms   |

| SENT Clock Variation Versus Nominal Tick Time                                           |                                               | T <sub>SCLK</sub>              | -20  | 0   | +20  | %    |

| ANALOG OUTPUT DRIVER                                                                    | •                                             |                                |      |     |      |      |

| Analog Output Voltage Range                                                             | $R_2$ Typ = 4.7 kΩ<br>VCC Typ = 5 V           | OUTX <sub>A_RNG_4p7</sub><br>K | 0.2  | _   | 4.8  | V    |

| Failure Band Low                                                                        | $R_2$ Typ = 4.7 kΩ<br>VCC Typ = 5 V           | OUTX <sub>A_FBL_4p7K</sub>     | -    | _   | 0.15 | V    |

| Failure Band High                                                                       | $R_2$ Typ = 4.7 kΩ<br>VCC Typ = 5 V           | OUTX <sub>A_FBH_4p7K</sub>     | 4.85 | -   | -    | V    |

| Output Ratio-metricity Error                                                            | (Notes 3, 5)                                  | OUTX <sub>A_RME</sub>          | -0.5 | -   | 0.5  | %    |

| OUTX leakage in high-impedance state at 125 $^{\circ}\text{C}$ T <sub>J</sub>           | (Note 3)                                      | OUTX <sub>A_LC125</sub>        | -0.5 |     | 0.5  | μΑ   |

| Time from Power-up till Start of the Analog Output Driver                               | (Note 3)                                      | OUTX <sub>A_PUP</sub>          | -    | -   | 1.2  | ms   |

| Analog Output Step Response Time (Digital Filter Disabled, Input Step to 90% of Output) | (Note 3)<br>Total cap on OUTX<br>Max = 240 nF | OUTX <sub>A_STR</sub>          | -    | -   | 0.5  | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 3. Designed to be met in stated voltage and temperature operating ranges, and characterized, though not parametrically tested in production.

- 4. For typical sensors application specific and over limited temperature range.

- 5. After the device is fully calibrated in the intended application.

OUTX<sub>RME</sub> =

$$\frac{\frac{\text{OUTX}_{VCC}}{\text{VCC}}}{\frac{\text{OUTX}_{VCC=5V}}{5 \text{ V}}} - 1$$

(eq. 1)

- Specified from VTH = 3.8 V to VTL = 1.1 V on SENT output wire, ISUP ≤ 20 mA.

For 3 μs nominal clock tick including clock accuracy. For higher clock tick times these values can be increased proportionally.

# NCV7192

#### **DETAILED OPERATING DESCRIPTION**

# **Basic Operation**

The NCV7192 provides an excitation voltage to the resistive bridge and measures the differential output. Each individual bridge sensor presents its own errors and non-idealities that need to be compensated through a calibration process. Sensor offset, sensitivity and non-linearity, as well as the temperature dependency of each of these parameters can be compensated.

After device start-up, configuration settings and compensation coefficients are loaded from the EEPROM into shadow registers. Bridge output voltage and temperature measurements are periodically captured and processed in the DSP to compensate the sensor output with a high degree of accuracy. The amplified and compensated signal is made available at the selected output.

In calibration mode, bidirectional communication with the IC is possible to allow configuring the device and its measurement channels with appropriate gain and offset settings. Raw bridge signal and temperature measurement data are made available for calculation of compensation coefficients. The chosen settings and coefficients can be stored in the EEPROM.

The nominal supply voltage for the NCV7192 is 5 V, but the IC is protected against overvoltage and reverse battery connection, and the analog and digital outputs are protected against shorts to the battery or to ground.

One of two output stages can be selected to communicate the acquired measurements: a 5 V analog output proportional to bridge signal and ratiometric to the supply voltage or a digital output according to the SENT protocol (SAE J2716 Apr 2016).

# **Supply Voltage Monitor**

The NCV7192 monitors the VCC supply to detect when it goes outside of the specified normal operating conditions. Both the undervoltage (VCC $_{\rm UV}$ ) as well as the overvoltage (VCC $_{\rm OV}$ ) thresholds have a programmable range that can be set in the associated EEPROM configuration bits. When the VCC goes outside of these programmed thresholds, the analog output driver will be either switched off or drive the OUTX voltage to one of the failure bands. The SENT driver will continue to operate but communicate this condition with a diagnostic fail flag.

Parametric performance of the device is not guaranteed outside of the nominal operating range.

# **Bridge Signal Measurement**

The bridge is driven with a nominal 3 V excitation voltage. The analog front end measures the differential signal from the bridge. The input signal is applied to a low-noise amplification stage with typical gain settings indicated in the associated table. Once amplified, the signal must remain within the input range of the ADC (PM<sub>ADCIN</sub>). To center the amplified input signal on the ADC input range,

an offset of maximum  $\pm 2xPM_{ADCIN}$  can be added to the amplified signal in  $4xPM_{ADCIN}/PM_{TRBIT}$  increments.

Table 1.

| Gain Setting | Max Sensitivity (mV/V) |

|--------------|------------------------|

| 0            | 125                    |

| 1            | 114                    |

| 2            | 105                    |

|              |                        |

| 23           | 17                     |

| 24           | 16                     |

|              |                        |

| 47           | 2.1                    |

After coarse offset and gain are applied to the differential input signal, the remaining offset and nonlinearity of the bridge signal as well as it's temperature behavior can be compensated for in the digital DSP.

The DSP uses the raw signal values (DP) and temperature (DT) measurements from their respective ADC's (see Temperature Measurement section on different temperature sources) and executes the following compensation:

$$\begin{aligned} P_{a} &= A_{a} + B_{a} \left( DP - P_{0}T_{0} \right) + C_{a} \left( DP - P_{0}T_{0} \right) \left( DP - P_{1}T_{0} \right) \\ &+ D_{a} \left( DP - P_{0}T_{0} \right) \left( DP - P_{1}T_{0} \right) \left( DP - P_{2}T_{0} \right) \end{aligned}$$

$$\begin{split} P_b = A_b + B_b \left( DP - P_0 T_1 \right) + C_b \left( DP - P_0 T_1 \right) \left( DP - P_1 T_1 \right) \\ + D_b \left( DP - P_0 T_1 \right) \left( DP - P_1 T_1 \right) \left( DP - P_2 T_1 \right) \end{split}$$

$$\begin{aligned} P_c &= A_c + B_c \left( DP - P_0 T_2 \right) + C_c \left( DP - P_0 T_2 \right) \left( DP - P_1 T_2 \right) \\ &+ D_c \left( DP - P_0 T_2 \right) \left( DP - P_1 T_2 \right) \left( DP - P_2 T_2 \right) \end{aligned}$$

$$D_{OUT} = P_a + P_b (DT - DT_0) + P_c (DT - DT_0) (DT - DT_1)$$

In which:

- P<sub>0...2</sub>T<sub>0...2</sub> are ADC readings at the different test points

- A<sub>a..c</sub> D<sub>a..c</sub> are coefficients that can be calculated during end-of-line calibration

- DT<sub>0...2</sub> are the digital readings at temperatures T0, T1 and T2 respectively

- D<sub>OUT</sub> is the digital output word for bridge signal P and temperature T

The bridge signal and temperature measurements and coefficients can be programmed over the calibration interface and stored in the EEPROM.

The sensor pins are monitored to detect connectivity failures between the NCV7192 and the bridge sensor element. For SN, SE, SS and SW, short to VSS, short to SN and disconnection of the pin will result in a diagnostic error, as well as a short to an adjacent SN/SE/SS/SW pin.

# **Temperature Measurement**

The NCV7192 can measure either the internal junction temperature or the bridge resistance for compensation of

temperature dependency of the bridge signal measurement. Selection of the appropriate temperature source is stored in the EEPROM during EOL calibration.

Readings from the selected temperature sensor are digitized and stored in a register where it is periodically updated.

The NCV7192 can measure medium temperature through an external NTC thermistor of choice. The thermistor is measured in a ratio with a factory trimmed, temperature-corrected reference resistor. After conversion to the digital domain, the ratio can be linearized with an in EEPROM programmable look-up table.

The SENT scale offset and SENT scale gain parameter allows to match the temperature values to the SENT temperature characteristic and calibrate out NTC unit-specific variation in the production line.

The NTC pin is monitored when it's measurement is enabled. An open or short to ground is detected and reported as a diagnostic error on the SENT driver.

The NTC temperature processing flags a failure if the measured ratio of the NTC and pull-up resistor goes outside of the range covered by the programmed LUT.

# **SENT Output Driver**

The SENT output serializes bridge signal, temperature and diagnostic information in a digital waveform using the SENT protocol. The waveform is buffered by a driver and presented to the OUTX pin that is loaded with an external pull up.

The SENT output transmits according to the standard SAE J2716 (April 2016) protocol. The tick time for the SENT protocol is programmable with settings between 3  $\mu$ s and 16  $\mu$ s. The available tick time settings are 3, 4, 6, 10, 12 and 16  $\mu$ s.

A pause pulse can be activated to achieve a full transmission frame length of 198 ticks for the high-speed option, 282 ticks for all other options.

The selectable options for fast channel data frames are P (high speed), P/P<sub>inv</sub>, P/–. P/T, P/S. The checksum is a 4-bit CRC of the Data nibbles, implemented according to J2716 Section 5.4.2.2.

The slow channel data can transmit diagnostics, SENT revision, sensor type and configuration/ manufacturer codes as well as each of the temperature sources through an 8-bit message ID and 12 bit data field.

# **Analog Output Driver**

The analog output consists of a 14-bit ratiometric D/A converter, a low-pass filter and a 5 V rail-to-rail output amplifier. Either a pull-up or a pull-down resistor is connected to the output. In analog output mode, only the bridge data is available.

The analog output driver is protected against shorts to VCC or VSS. Even a short of the VCC or OUTX pin to a high-voltage battery terminal (within the defined absolute maximum ratings) will not lead to immediate destruction and the device will return to normal operation after removal of the short. In absence of VCC, VSS or OUTX connection or when a reverse polarity is applied to the supply terminals, the driver is switched off and the output pin is high impedance. The voltage level at the OUTX terminal is in this case determined by the connected pull-up or pull-down resistor. Upon removal of the associated malfunction, the driver will resume normal operation.

If any of the internal diagnostic errors fail, the analog output driver is either driven to the high or low fail band. Internal diagnostics can be disabled in EEPROM configuration bits, though their disabling may affect the safety metrics.

#### **Calibration Mode**

The calibration interface enables read and write commands to the memory and allows to read back digitized measurement results to allow configuring the device for the intended application and calibrating the compensation coefficients for the particular bridge instance. The interface works as UART half duplex mode over the OUTX pin after the device is configured to Calibration Mode.

The NCV7192 can be brought in Calibration Mode by elevating the VCC supply voltage above the threshold VCC<sub>CM</sub> and sending Key-code CCM over the OUTX pin after T<sub>CMWAIT</sub> and before T<sub>CM</sub> period after POR.

# **ORDERING INFORMATION**

| Device       | Package  | Shipping <sup>†</sup> |

|--------------|----------|-----------------------|

| NCV7192D0R2G | SOIC8    | 3000 / Tape & Reel    |

| NCV7192C1    | Bare Die | Wafer Sale            |

<sup>†</sup> For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

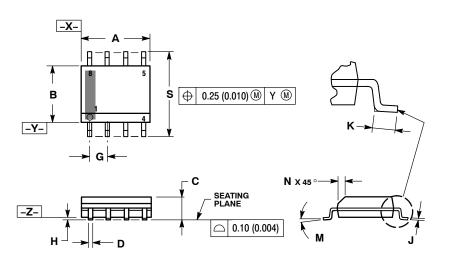

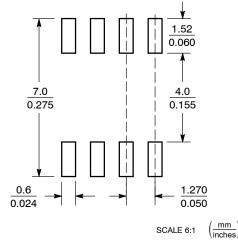

# SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

XS

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |          | INC   | HES   |

|-----|-------------|----------|-------|-------|

| DIM | MIN         | MAX      | MIN   | MAX   |

| Α   | 4.80        | 5.00     | 0.189 | 0.197 |

| В   | 3.80        | 4.00     | 0.150 | 0.157 |

| С   | 1.35        | 1.75     | 0.053 | 0.069 |

| D   | 0.33        | 0.51     | 0.013 | 0.020 |

| G   | 1.27        | 1.27 BSC |       | 0 BSC |

| Н   | 0.10        | 0.25     | 0.004 | 0.010 |

| J   | 0.19        | 0.25     | 0.007 | 0.010 |

| K   | 0.40        | 1.27     | 0.016 | 0.050 |

| М   | 0 °         | 8 °      | 0 °   | 8 °   |

| N   | 0.25        | 0.50     | 0.010 | 0.020 |

| S   | 5.80        | 6.20     | 0.228 | 0.244 |

# **SOLDERING FOOTPRINT\***

0.25 (0.010) M Z Y S

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week W = Pb-Free Package

XXXXXX XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α ww

= Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

# **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                | PAGE 1 OF 2 |  |  |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

# SOIC-8 NB CASE 751-07 ISSUE AK

# **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | 7. BASE, #1 8. EMITTER, #1  STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                        | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8:<br>PIN 1. COLLECTOR, DIE #1<br>2. BASE, #1<br>3. BASE, #2                                                                                                       |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                  |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15:  PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON              | STYLE 16:  PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                    |

| 5. RXE 6. VEE 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6            | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V MON 6. VBULK 7. VBULK 8. VIN                                                                         |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                          |

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                  | PAGE 2 OF 2 |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales