# STWLC68

Datasheet

# Qi-compliant inductive wireless power receiver for 5W applications

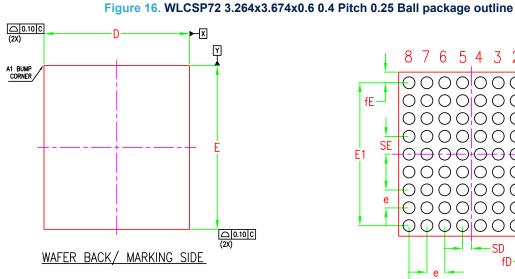

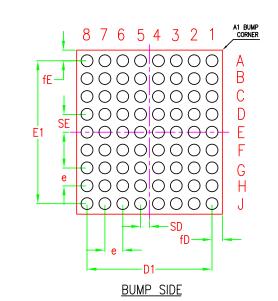

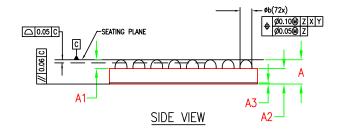

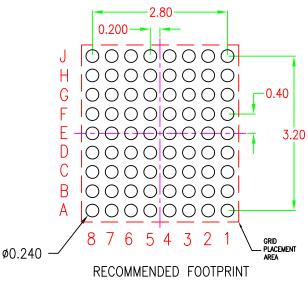

Flip Chip (3.29 x 3.70 mm)

| Product status link |               |  |  |  |  |  |  |  |

|---------------------|---------------|--|--|--|--|--|--|--|

| STWLC68             |               |  |  |  |  |  |  |  |

| Product summary     |               |  |  |  |  |  |  |  |

| Order code          | STWLC68JRH    |  |  |  |  |  |  |  |

| Package             | WLCSP72       |  |  |  |  |  |  |  |

| Packing             | Tape and reel |  |  |  |  |  |  |  |

### **Features**

- Up to 5 W output power

- Qi 1.2.4 inductive wireless standard communication protocol compliant

- Integrated 27 V synchronous rectifier with 98% (typ.) efficiency

- Low drop-out linear regulator with output current and input voltage control loops

- 3.6 V to 20 V programmable output voltage with 25 mV resolution

- Up to 80% overall system efficiency

- 32-bit, 64 MHz ARM Cortex microcontroller core

- OTP memory for configuration data

- 8-channels, 10-bit A/D Converter

- 6 configurable GPIOs

- Accurate voltage/current measurement for Foreign Object Detection (FOD)

- Output Over-Voltage clamping protection

- 400 kHz I<sup>2</sup>C interface

- On-chip thermal management and protections (Over-voltage, Over-current)

- Enhanced power dissipation capability Chip-Scale Package (CSP)

### **Application**

- Smartphones and PDAs

- Power banks

- GPS navigators

- Medical and healthcare equipment

- Wearable devices

### **Description**

The STWLC68 is an integrated Wireless Power Receiver suitable for portable applications and capable of managing up to 5 W of output power. The chip has been designed to support Qi 1.2.4 specifications for inductive communication protocol and Base Power Profile (BPP).

The STWLC68 shows excellent efficiency performance thanks to the integrated lowloss synchronous rectifier and the low drop-out linear regulator: both elements are dynamically managed by the digital core to minimize the overall power dissipation over a wide range of output load conditions.

Through the I<sup>2</sup>C interface the user can access and modify different configuration parameters, tailoring the operation of the device to the needs of custom applications. The configuration parameters can be saved in the embedded OTP memory and automatically retrieved at power-up, allowing the STWLC68 to operate as standalone device.

The STWLC68 is housed in a Chip-Scale Package to fit real-estate solutions in wearable devices.

## **1** Introduction

STWLC68 is a Wireless Power Receiver that rectifies the AC voltage developed across the receiving coil and provides a regulated DC voltage at the output.

The 32-bit core MCU is the supervisor of the whole device and manages all the functional blocks to

- establish and maintain communication with the transmitter,

- ensure adherence to Qi standard specifications (wherever required),

- optimize the efficiency by properly adjusting the operating point

- guarantee reliability by monitoring and protecting both the load and the device itself.

In order to execute the above mentioned (and many others) task, the MCU core relies on a resident firmware stored in ROM memory. In addition, some configuration parameters (e.g. output voltage, FOD tuning parameters, etc.) can be saved in the internal One-Time Programmable (OTP) memory and retrieved at power-up, allowing the STWLC68 to operate as a fully autonomuous stand-alone chip.

Applications in which the host system directly monitors or controls the power transfer, the I2C interface provides full access to the internal registers of the STWLC68.

The device is also equipped with six programmable general-purpose I/O pins (GPIOs) to implement specific functions (e.g. driving status LEDs, enabling the output on request, informing the host system about faulty conditions, etc.).

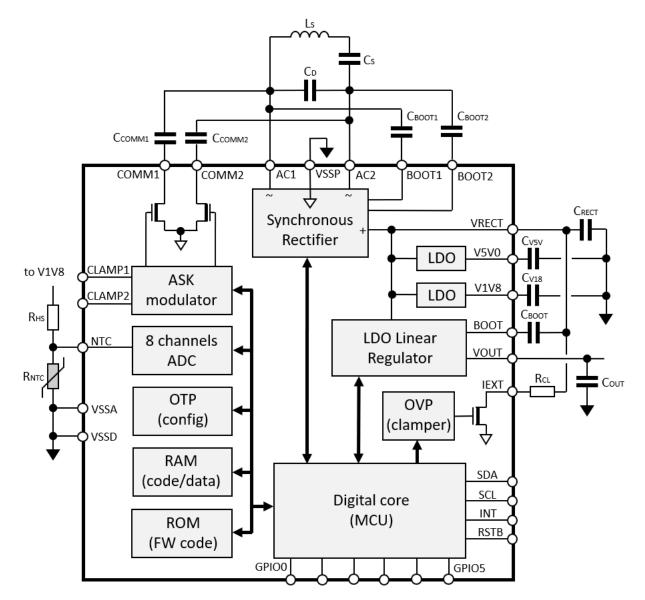

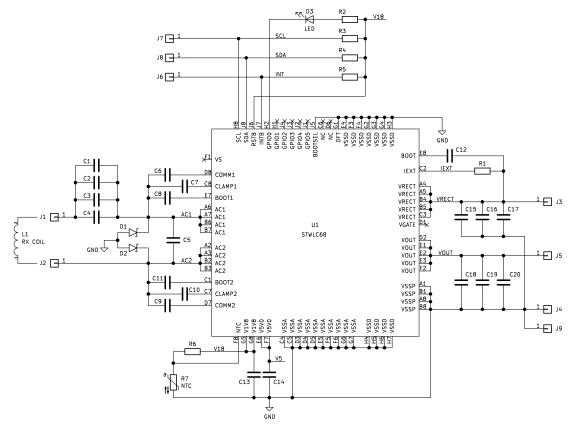

Block diagram shows the block diagram of the device with simplified interconnections among the functional blocks. The synchronous rectifier converts the AC voltage from the receiving coil into a DC voltage at the VRECT pin. The four switches of the rectifier (that is basically an H-bridge) are controlled by the digital core in order to minimize both conduction and switching losses as a function of the output voltage and current, both monitored by two channels of the ADC. Two bootstrap capacitors are externally connected to the BOOT1-BOOT2 pins to correctly drive the high-side switches of the rectifier.

The output of the rectifier, filtered by an external capacitor, is also the input rail for the main LDO linear regulator and for the auxiliary linear regulators in charge of deriving the 5 V and 1.8 V supply voltages.

The digital core has full control of the main LDO linear regulator in order to manage the output voltage, the output current and the drop-out voltage: since the most relevant contribution to the total chip power dissipation is due to the main linear regulator, minimizing its drop-out voltage is a key factor.

Of course the minimization of the drop-out voltage requires a closed loop regulation of the voltage at the VRECT pin, i.e. a feedback information that is sent to the transmitter (via ASK modulation) which, in turn, adjusts the delivered power by acting on the supply voltage, the switching frequency or the switching duty-cycle (or a combination of the three) of its own power stage, depending on the adopted technique.

This regulation loop involving the transmitter is an essential part of the wireless power transmission and is extensively described in Qi specifications.

# 2 Block diagram

57

### Figure 1. Simplified block diagram

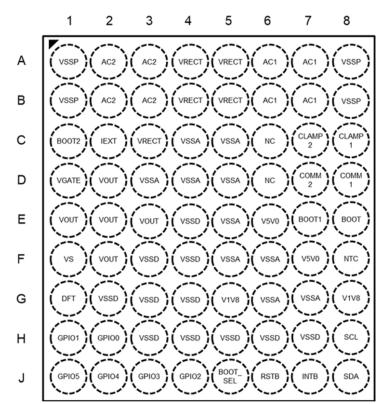

# 3 Device pinout

### Table 1. Pin description

| Pin name | Pin location                                     | Pin function                                                                                                                  |

|----------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|          | C4,C5,D3,D4,                                     |                                                                                                                               |

| VSSA     | D5,E5,F5,F6,                                     | Analog ground. Power return for the main LDO and the analog circuitry.                                                        |

|          | G6,G7                                            |                                                                                                                               |

| VSSD     | E4, F3, F4, G2, G3,<br>G4, H3, H4, H5, H6,<br>H7 | Digital ground. Reference for digital input and output signals.                                                               |

| VSSP     | A1, A8, B1, B8                                   | Power ground. Power return for the synchronous rectifier.                                                                     |

| AC1      | A6, A7, B6, B7                                   | AC power input: input of the synchronous rectifier. Connect to RX series resonant circuit.                                    |

| AC2      | A2, A3, B2, B3                                   | AC power input: input of the synchronous rectifier. Connect to RX series resonant circuit.                                    |

| BOOT1    | E7                                               | Synchronous rectifier bootstrap capacitor connection: a 47 nF (typ.) ceramic capacitor is connected between this pin and AC1. |

| BOOT2    | C1                                               | Synchronous rectifier bootstrap capacitor connection: a 47 nF (typ.) ceramic capacitor is connected between this pin and AC2. |

| BOOT     | E8                                               | Main LDO power transistor bootstrap capacitor. Connect a 4.7 nF (typ.) ceramic capacitor between this pin and VRECT.          |

### Figure 2. Pin assignment (through top view)

| Pin name | Pin location | Pin function                                                                                                                                                                                                                                                                                      |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP1   | C8           | Auxiliary modulation switches connection: capacitors between CLAMP1 and AC1 and between CLAMP2 and AC2 are used to implement additional ASK modulation. These pins are optionally used, in conjunction with COMM1 and COMM2 pins, to modify the                                                   |

| CLAMP2   | C7           | ASK modulation index in specific operating conditions.                                                                                                                                                                                                                                            |

| VRECT    | A4, A5, B4,  | Synchronous rectifier output and input for the main LDO linear regulator. A suitable<br>capacitor between these pins and VSSP ensures residual AC ripple filtering and                                                                                                                            |

|          | B5, C3       | energy storage for proper load transient response.                                                                                                                                                                                                                                                |

| VS       | F1           | Reserved: this pin must be left floating.                                                                                                                                                                                                                                                         |

| DFT      | G1           | Reserved: this pin must be connected to ground.                                                                                                                                                                                                                                                   |

| BOOT_SEL | J5           | Reserved: this pin must be connected to ground.                                                                                                                                                                                                                                                   |

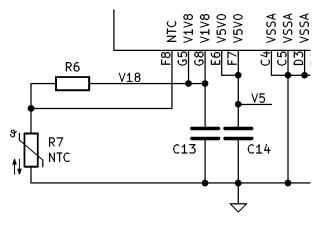

| NTC      | F8           | Coil temperature sensing input: this pin is connected to the center tap of a resistor divider having an NTC in the low-side position. If this function is not used, the pin must be pulled-up to V18 through a 10 k $\Omega$ resistor to prevent triggering the coil over-temperature protection. |

| COMM1    | D8           | Modulation switches connection: capacitors between COMM1 and AC1 pin and                                                                                                                                                                                                                          |

| COMM2    | D7           | between COMM2 and AC2 pin are used to implement ASK modulation.                                                                                                                                                                                                                                   |

|          | D2, E1, E2,  | Main LDO linear regulator output voltage. Connect a suitable filtering capacitor                                                                                                                                                                                                                  |

| VOUT     | E3, F2       | between these pins and VSSA to ensure stable operation and proper load transient response in all operating conditions.                                                                                                                                                                            |

| V1V8     | G5, G8       | 1.8V LDO output and supply rail for the digital core, the ADC and the analog circuitry. Connect a 1 $\mu F$ filtering capacitor between this pin and ground.                                                                                                                                      |

| V5V0     | F7, E6       | 5V LDO output and supply rail for the auxiliary circuitry. Connect a 1 $\mu F$ filtering capacitor between this pin and ground.                                                                                                                                                                   |

| RSTB     | J6           | Chip-reset input. If set low, the internal digital core is reset. This pin is eventually used by the host controller to control the power transfer process. Connect to V1V8 pin if not used.                                                                                                      |

| IEXT     | C2           | Internal pull-down switch for resisitive (dissipative) over-voltage protection: a resistor with adequate power dissipation capability must be connected between this pin and VRECT to damp excessive voltage developing at the output of the rectifier.                                           |

| VGATE    | D1           | Gate driver output for the optional VRECT discharging transistor. This pin goes high when the voltage drop across the main LDO (VVRECT – VVOUT) exceeds the programmed threshold.                                                                                                                 |

| SCL      | H8           | I2C bus, clock line input. A pull-up resistor to the supply rail of the host controller is required to ensure correct digital levels.                                                                                                                                                             |

| SDA      | J8           | I2C bus, data line I/O. A pull-up resistor to the supply rail of the host controller is required to ensure correct digital levels.                                                                                                                                                                |

| NC       | C6, D6       | Reserved: this pin must be connected to ground or left floating.                                                                                                                                                                                                                                  |

| GPIO0    | H2           |                                                                                                                                                                                                                                                                                                   |

| GPIO1    | H1           |                                                                                                                                                                                                                                                                                                   |

| GPIO2    | J4           | Programmable general-purpose I/Os: the function of these pins depends on the                                                                                                                                                                                                                      |

| GPIO3    | J3           | configuration of the device.                                                                                                                                                                                                                                                                      |

| GPIO4    | J2           |                                                                                                                                                                                                                                                                                                   |

| GPIO5    | J1           |                                                                                                                                                                                                                                                                                                   |

| INTB     | J7           | Interrupt output (active low). Programmable open-drain output used to generate an interrupt on specific events for the host controller. Also used as auxiliary control signa during OTP flash.                                                                                                    |

# 4 Electrical and thermal specifications

### 4.1 Absolute maximum ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other condition above those indicated in Table 2 is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| Parameter              | Pin(s)                                                                                                                 | Min. | Max. | Unit |

|------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|

|                        | AC1, AC2, COMM1, COMM2, CLAMP1 and CLAMP2<br>respect to ground (VSSA, VSSD and VSSP pins)                              | -0.9 | 27   |      |

|                        | BOOT1 to AC1                                                                                                           | -0.3 | 5.5  |      |

|                        | BOOT2 to AC2                                                                                                           | -0.3 | 5.5  |      |

|                        | BOOT1 and BOOT2 respect to ground (VSSA, VSSD and VSSP pins)                                                           | -0.3 | 27   |      |

|                        | BOOT respect to VRECT                                                                                                  | -0.3 | 5.5  |      |

| Pin voltage range      | VRECT, VOUT and IEXT respect to ground (VSSA,<br>VSSD and VSSP pins)                                                   | -0.7 | 27   | V    |

|                        | V1V8, NTC, VS and DFT respect to ground (VSSA,<br>VSSD and VSSP pins)                                                  | -0.3 | 2    |      |

|                        | V5V0, VGATE, GPIO0 through GPIO5, INTB, RSTB,<br>SDA, SCL and BOOT_SEL respect to ground (VSSA,<br>VSSD and VSSP pins) | -0.7 | 5.5  |      |

|                        | Relative voltage between any ground pin (VSSA, VSSD, VSSP)                                                             | -0.3 | 0.3  |      |

| HBM ESD susceptibility |                                                                                                                        |      | 2000 |      |

| JEDEC JS001-2012       |                                                                                                                        |      | 2000 | V    |

| CDM ESD susceptibility | All pins                                                                                                               |      | 500  | v    |

| JEDEC JS002-2012       |                                                                                                                        |      | 500  |      |

| Latch-Up EIA/JESD78E   |                                                                                                                        | -200 | 200  | mA   |

### Table 2. Absolute maximum ratings

### 4.2 Thermal characteristics

#### Table 3. Thermal characteristics

| Symbol                           | Parameter                              | Conditions | Min. | Тур. | Max. | Unit |

|----------------------------------|----------------------------------------|------------|------|------|------|------|

| T <sub>A,OP</sub> <sup>(1)</sup> | Operating ambient temperature          |            | -40  |      | 85   | °C   |

| T <sub>J,OP</sub>                | Operating junction temperature         |            | 0    |      | 125  |      |

| R <sub>OJA</sub> <sup>(2)</sup>  | Junction to ambient thermal resistance | 2s2p       |      | 40   |      | °C/W |

| T <sub>SHDN</sub>                | Thermal shutdown threshold             |            |      | 125  |      | °C   |

| T <sub>SHDN,HYST</sub>           | Thermal shutdown hysteresis            |            |      | 10   |      | C    |

1. T<sub>A,OP</sub> -40°C to +85°C, limits over the operating range guaranteed by design and characterization, if not otherwise specified.

2. Device mounted on a standard JESD51-5 test board

57

# 4.3 Electrical characteristics

0 °C < T<sub>A</sub> < 85 °C; V<sub>VRECT</sub> = 5 V to 10 V. Typical values are at T<sub>J</sub> = 25 °C, if not otherwise specified.

| Symbol                   | Parameter                                                            | Test Conditions                                                                            | Min. | Тур. | Max. | Unit   |

|--------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|--------|

| Supply section           |                                                                      |                                                                                            |      |      |      |        |

| V                        | VRECT Under-Voltage Lock-Out upper<br>(turn-on) threshold            | VRECT pin voltage, rising edge                                                             |      | 3.0  | 3.3  | V      |

| Vvrect,uvlo              | VRECT Under-Voltage Lock-Out lower<br>(turn-off) threshold           | VRECT pin voltage, falling edge                                                            |      | 2.5  |      | V      |

| V <sub>VRECT,MAX</sub>   | VRECT maximum operating supply voltage                               | Voltage on VRECT pin                                                                       |      | 16   |      | V      |

| I <sub>VOUT,Q</sub>      | VOUT current consumption in shut-<br>down mode                       | RSTB low for more than 1 ms, supply voltage (5 V) applied to VOUT                          |      | 400  | 750  | μA     |

| I <sub>VRECT,OP</sub>    | Operating current consumption (not considering the programmed dummy- | RSTB high, supply voltage applied to<br>VRECT                                              |      | 9.7  | 13   | mA     |

| I <sub>VOUT,OP</sub>     | load current)                                                        | RSTB high, supply voltage applied to VOUT                                                  |      | 9.7  | 13   | mA     |

| 1.8V supply volta        | ge LDO linear regulator                                              | · ·                                                                                        |      |      |      |        |

| V                        | LDO1 output voltage I <sub>V1V8</sub> = 5 mA 1.79 1.8                |                                                                                            | 1.8  | 1.81 | V    |        |

| V <sub>V1V8</sub>        | LDO1 load regulation                                                 | 0 mA < I <sub>V1V8</sub> < 10 mA                                                           |      | 5    | 20   | mV     |

| 5V supply voltage        | LDO linear regulator                                                 |                                                                                            |      |      |      | 1      |

|                          | LDO2 output voltage                                                  | I <sub>V5V0</sub> = 5 mA, V <sub>VRECT</sub> = 5.1 V                                       | 4.8  | 5    | 5.2  | V      |

| V <sub>V5V0</sub>        | LDO2 load regulation                                                 | 0 mA <i<sub>V5V0 = 0 mA &lt;10 mA</i<sub>                                                  |      | 2    | 20   | mV     |

|                          | LDO2 under-voltage lock-out upper<br>threshold                       |                                                                                            | 2.8  | 3    | 3.2  | V      |

| I <sub>V5V0,EXT</sub>    | Maximum current allowed for external load                            |                                                                                            |      |      | 10   | mA     |

| Synchronous rec          | tifier                                                               | · · · · · · · · · · · · · · · · · · ·                                                      |      |      |      |        |

| Efficiency               | Torget restifier officiency                                          | $I_{VRECT}$ = 1 A, $V_{VRECT}$ = 5.2 V, $f_{AC}$ = 100 kHz to 250 kHz                      |      | 97   |      | %      |

| Efficiency               | Target rectifier efficiency                                          | I <sub>VRECT</sub> = 1 A, V <sub>VRECT</sub> = 9.2 V, f <sub>AC</sub> = 100 kHz to 250 kHz |      | 97   |      | 70     |

| Processo                 | Synchronous rectifier switches on-                                   | low resistance mode (dynamically selected)                                                 | 60   | 70   | 80   | mΩ     |

| R <sub>DSON,ACx</sub>    | resistance                                                           | high resistance mode (dynamically selected)                                                | 150  | 250  | 350  | 111 52 |

| ASK modulator            |                                                                      | · · · · · · · · · · · · · · · · · · ·                                                      |      |      |      |        |

| R <sub>DSON,COMMx</sub>  | COMM1-COMM2 modulation switches<br>on-resistance                     | V <sub>VRECT</sub> = 5 V                                                                   |      | 1    | 2    | Ω      |

| R <sub>DSON,CLAMPx</sub> | CLAMP1-CLAMP2 modulation<br>switches on-resistance                   | V <sub>VRECT</sub> = 5 V                                                                   |      | 1    |      | Ω      |

| I <sub>DMYL,MAX</sub>    | Dummy load current (internally drawn<br>from VRECT when enabled)     | $V_{VRECT}$ = 5 V to 12 V, $I_{VRECT}$ = 0 A,<br>IDMYL_SET = 0x1F                          |      | 310  |      | mA     |

| I <sub>DMYL,STEP</sub>   |                                                                      |                                                                                            |      | 10   |      |        |

| Main LDO linear r        | egulator                                                             |                                                                                            |      |      |      |        |

| V <sub>OUT</sub>         | Output voltage range                                                 | VOUT_SET = 0x00C8                                                                          | 4.95 | 5.0  | 5.05 | V      |

### Table 4. Electrical characteristics

| Symbol                  | Parameter                                           | Test Conditions                                                                         | Min.  | Тур. | Max.  | Unit |

|-------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|-------|------|

|                         | Output voltage range                                | VOUT_SET = 0x0320                                                                       | 19.92 | 20   | 20.08 | V    |

| V <sub>OUT</sub>        | Vout Line regulation                                | I <sub>VOUT</sub> = 0.1 A, V <sub>OUT</sub> = 5 V,<br>6 V < V <sub>VRECT</sub> < 15 V   |       | 3    | 15    | mV   |

| Vout Load regulation    |                                                     | V <sub>VRECT</sub> = 5.5 V, V <sub>OUT</sub> = 5 V,<br>1 mA < I <sub>VOUT</sub> < 800mA |       | 30   | 70    | mV   |

| V <sub>OUT_STEP</sub>   | Programmable step size                              |                                                                                         |       | 25   |       | mV   |

| V <sub>DROP</sub>       | Linear regulator drop-out voltage                   | I <sub>OUT</sub> = 1 A                                                                  |       | 100  | 200   | mV   |

| IOUT_CL                 | Linear regulator overcurrent protection             |                                                                                         | 1.4   | 1.5  | 1.6   | А    |

| Thermal protection      | on (external NTC)                                   |                                                                                         |       |      |       |      |

|                         | External over-temperature NTC pin upper threshold   |                                                                                         | 0.55  | 0.59 | 0.65  | V    |

| V <sub>NTC,OTP</sub>    | External over-temperature NTC pin hysteresis        |                                                                                         | 50    | 125  | 150   | mV   |

| I <sub>NTC,BIAS</sub>   | NTC pin bias current                                | V <sub>NTC</sub> = 1.5 V                                                                |       | 1    | 2     | μA   |

| Over-Voltage Pro        | tection                                             |                                                                                         | -     |      |       |      |

| V <sub>VRECT,OVPH</sub> | Hard OVP (AC1-AC2 short to VSSP)<br>upper threshold |                                                                                         | 24.2  | 24.7 | 25.2  | V    |

|                         | Hard-OVP hysteresis                                 |                                                                                         | 0.5   | 1.0  | 1.5   |      |

|                         | Adjustable Soft OVP (IEXT clamping)                 | VRECT_OVP = 0x2EE0                                                                      | 11.5  | 12   | 12.5  |      |

| V <sub>VRECT,OVPS</sub> | upper threshold                                     | VRECT_OVP = 0x4650                                                                      | 17.5  | 18   | 18.5  | v    |

|                         | Fixed Soft OVP (IEXT clamping) upper threshold      |                                                                                         | 22.5  | 23   | 23.5  |      |

| I <sub>IEXT,MAX</sub>   | IEXT clamping switch current capability             | Non-repetitive 100 ms rectangular<br>pulse                                              |       |      | 0.3   | А    |

| R <sub>IEXT,ON</sub>    | IEXT switch on-resistance                           | I <sub>IEXT</sub> = 250 mA                                                              |       | 1.8  | 3     | Ω    |

| Digital signals         | · · · · · · · · · · · · · · · · · · ·               |                                                                                         |       |      |       |      |

| V <sub>IL</sub>         | Low level input voltage                             |                                                                                         |       |      | 0.55  |      |

| V <sub>IH</sub>         | High level input voltage                            |                                                                                         | 1.14  |      |       | V    |

| V <sub>OH</sub>         | GPIOx high level output voltage                     | Output high, I <sub>SOURCE</sub> = 3mA                                                  | 1.25  |      |       |      |

| I <sub>OH</sub>         | GPIOx pin current capability                        | Output high                                                                             | 3     |      |       | mA   |

| V <sub>OL</sub>         | Low level output voltage                            | Output low, I <sub>SINK</sub> =3mA                                                      |       | 360  |       | mV   |

|                         |                                                     | GPIOx, INTB, SCL, SDA pins                                                              | 10    | 16   | 22    |      |

| I <sub>IPU</sub>        | Internal pull-up current                            | RSTB pin                                                                                | 4     | 8    | 13    |      |

| hee                     | Internal null down ourrest                          | GPIOx, INTB, SCL, SDA pins                                                              | 10    | 16   | 22    | μA   |

| I <sub>IPD</sub>        | Internal pull-down current                          | RSTB pin                                                                                | 4     | 8    | 13    |      |

# 4.4 Recommended operating conditions

| Symbol                 | Parameter                                                 | Conditions                                         | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------|----------------------------------------------------|------|------|------|------|

| DC characteris         | tics                                                      |                                                    |      |      |      |      |

| V <sub>VRECT,OP</sub>  | Operating VRECT supply voltage range                      |                                                    | 4.5  |      | 16   | V    |

| V <sub>VRECT,BPP</sub> | Operating VRECT supply voltage range in BPP mode          | V <sub>VOUT</sub> = 5 V, I <sub>VOUT</sub> = 0.5 A | 5.1  | 5.2  | 8    | V    |

| AC characteris         | tics                                                      |                                                    |      |      |      |      |

| V <sub>ACIN</sub>      | AC peak-to-peak voltage between<br>AC1 and AC2 input pins |                                                    |      |      | 24   | V    |

| I <sub>AC,MAX</sub>    | AC1 and AC2 pins maximum RMS current capability           | Sinusoidal waveform at AC1-AC2                     |      |      | 2    | А    |

| f <sub>AC</sub>        | AC synchronous rectifier input<br>frequency range         | terminals                                          | 50   |      | 500  | kHz  |

# 5 Device description

### 5.1 Chip reset pin

The RSTB pin, active low, can block the operation of the device by forcing the digital core in reset state. After releasing the RSTB pin, the STWLC68 re-starts and retrieves the default configuration data from the OTP. If not used, the RSTB pin should be connected to the V1V8 or to the V1V8 rail.

### 5.2 Synchronous rectifier

The synchronous rectifier of the STWLC68 is a key block in charge of converting the AC input power from the receiving coil into a DC supply rail for the following linear regulator. In principle it consists of four N-channel MOSFETs arranged in a H-bridge, conveniently driven by a control block that monitors the voltage at the AC1 and AC2 pins to optimize the commutations and to charge the external bootstrap capacitors for the high-side switches. Different driving schemes are possible for the switches of the rectifier and the MCU core dynamically selects the optimal one to maximize the overall efficiency as a function of the operating point. When designing the filtering capacitor at the output of the synchronous rectifier, it must be taken into account that it has to minimize the AC residual ripple and to provide energy storage to sustain load transients, without impacting on the ASK communication with the transmitter.

### 5.3 Main linear regulator

The main linear regulator of the STWLC68 ensures a constant output voltage with minimum power loss. Excellent line and load regulation are demanded to the analog circuitry of this block, while the optimal operating point is managed by the MCU core. The minimization of the power loss is achieved by adjusting the drop-out voltage according to a programmed target curve: to do so, the MCU core handles the communication with the transmitter to get the desired VRECT rail voltage. Key voltages and currents in the block are constantly monitored to optimize the performance of the linear regulator and to to provide multiple proctection levels (see related section).

The main linear regulator has three independent control loops acting on the power pass element:

- Output voltage regulation loop: this loop regulates the output voltage at the nominal value set in the dedicated register;

- Input current regulation loop: in order to prevent a collapse at the output of the synchronous rectifier, the current through the linear regulator is limited to a fixed 1.5 A limit. This loop overdrives the previous one, reducing the output voltage as a consequence.

- Input voltage regulation loop: this loop works in conjunction with the input current one and avoids that the VRECT rail drops below a programmable value.

Both input current and input voltage regulation loops play an important role: since the output of the rectifier is a highly variable voltage source (especially because of unpredictable changes in coupling of the coils), extra care is needed to avoid voltage drops that could lead to an undesirable MCU core reset. The pass transistor is an N-channel MOSFET and the BOOT pin is dedicated to its bootstrap capacitor, ensuring correct driving and lower on-resistance also in case of drop-out condition. A filtering capacitance higher than 20 µF has to be connected to the output rail (VOUT) in order to ensure stable operation of the linear regulator.

### 5.4 ASK communication

Robust and reliable in-band ASK modulation is critical to the operation of any Qi compliant devices. STWLC68 has dedicated hardware on top of the firmware algorithm to improve the performance of the in-band communication. Parameters controlling the ASK modulation used during communication (e.g. modulation index as a function of the load) are programmable via OTP. At ping-up and in light-load or no-load conditions the modulation index may result critical, especially in case of poor magnetic coupling of the coils: an internal, programmable dummy load at VRECT can be enabled to enhance the ASK modulation, resulting is a quicker transaction with the transmitter. The dummy current is automatically drawn from VRECT at power-up and it is gradually reduced as the output current increases: this operation ensures a constant load baseline that exits the game once the external load prevails.

### 5.5 Protections

#### **Over-voltage protection**

The STWLC68 integrates different Over-Voltage Protection circuits to protect itself, the load connected to its output rail and the external components from damage due to overheating and/or exceeding AMR condition. Under normal operating conditions the voltage at the output of the synchronous rectifier is slightly higher than the output one thanks to the communication with the transmitter. A sudden change in the coupling factor between transmitting and receiving coils, for example due to abrupt reciprocal repositioning of the coils, easily leads to unpredicatable voltage peaks at the AC input terminals: the TX-RX regulation loop is not fast enough to prevent such an event and additional precautions must be taken.

Both the VRECT and VOUT outputs are constantly monitored. The VRECT rail has three concurrent OVP mechanism: two fixed, analog ones based on a HW comparator (OVPH and Fixed-OVPS) and a digital ones (Adj-OVPS), implemented in the FW and relying on the ADC readings (OVPS). In case the  $V_{VRECT} > V_{VRECT,OVPH}$  condition occurs, the protection circuit immediately shorts both AC1 and AC2 pins to ground. This clamping action is released as soon as the voltage at the V5V0 pin falls down below its power-good level (4V typ.). Normally (it actually depends on the output load) the transmitter reacts to this protection by cutting-off the power transfer.

Both OVPS (Fixed and Adjustable) protections activate a different mechanism compared to OVPH: the IEXT pin goes low and an external resistor starts drawing current from VRECT (see block diagram). The digital OVP protection (Adj-OVPS) has an adjustable threshold and can be taylored for the application. In most of cases both soft OVP protections do not interrupt the ongoing power transfer, but a significant energy could be dissipated in the external resistor and a careful design is required. Optionally, the STWLC68 can be programmed to issue an End-of-Power-Transfer (EPT) packet to the transmitter on any OVP event.

#### **Over-temperature protection**

The STWLC68 is equipped with three over-temperature detection circuits based on different sources:

- 1) Synchronous rectifier temperature sensor

- 2) Main linear regulator temperature sensor

- 3) Coil (external NTC) temperature sensor

The signals coming from the two internal temperature sensors and the NTC pin (analog input) are conditioned and routed to the multi-channel ADC. The temperature of both the rectifier and the linear regulator can be directly read via dedicated registers. The external sensor, typically placed very close to the coil to prevent over-heating, is often a low-sided NTC of a resistor divider whose center tap is connected to the NTC pin, while the high-side resistor is connected to the V1V8 pin.

Reading the temperature of the external sensor requires some calculation from the host, since it depends on the NTC characterisitcs (beta, nominal value), the high-side resistor and the input range of the NTC pin (0 V - 1.5 V). The internal sensors are also monitored and compared to a fixed 125°C threshold (10°C hysteresis) to trigger a HOVP event (AC1 and AC2 shorted to ground).

In addition, the STWLC68 allows the user to define for each source a threshold with associated set of actions.

The selectable actions are any combination of:

- EPT packet generation

- Output disconnection

- INT pin status change

For example, a chip over-temperature alert could be sent to the host system by setting two temperature thresholds (e.g. 100°C for the rectifier and 90°C for the linear regulator) and linking the INT pin to the related interrupts.

#### **Over-current protection**

As mentioned in the description of the main linear regulator, the current through the pass transitor is sensed and limited to a fixed 1.5 A threshold. An internal interrupt is generated in such a case and specific actions could be linked to it. In any case, a severe over-load condition quikly leads to an output voltage drop: if VOUT drops below a fixed 1.25 V threshold (e.g. in case of output short-circuit), the linear regulator is disabled an an interrupt is generated. A programmable threshold allows the user to define an early over-load alert interrupt and a set of associated actions.

### 5.6 GPIOx and INTB pins

The GPIO0 through GPIO5 pins are programmable general-purpose I/O pins whose functions can be assigned in OTP memory. These pins can be configured both as inputs and outputs (either push-pull or open-drain) according to the selected function.

The INTB pin is an interrupt output line that can be associated to any internal interrupt condition and used to inform the host system about specific events. The INTB pin can be programmed to be push-pull or open-drain type as well.

The following table reports the available functions that can be assigned by writing the corresponding GPIOx-FS register.

| GPIO function and | type | GPIOx-FS register | Description                                                                              |

|-------------------|------|-------------------|------------------------------------------------------------------------------------------|

| GPIOF_NONE        | I    | 0x00              | No function                                                                              |

| GPIOF_XINT_OD     | 0    | 0x03              | Interrupt signal status (inverted), open-drain                                           |

| GPIOF_XINT_PP     | 0    | 0x04              | Interrupt signal status (inverted), push-pull                                            |

| GPIOF_OUT_INH     | I    | 0x05              | Output voltage inhibit control (input):<br>low = enable VOUT, high = inhibit VOUT        |

| GPIOF_OUT_MON     | 0    | 0x06              | Output status monitor<br>low = VOUT disabled, high = VOUT enabled                        |

| GPIOF_OUT_XMON    | 0    | 0x07              | Output status monitor (inverted)<br>low = VOUT enabled, high = VOUT disabled             |

| GPIOF_OUT_XMON_OD | 0    | 0x08              | Output status monitor (inverted, open-drain)<br>low = VOUT enabled, high = VOUT disabled |

| GPIOF_ADC_TICK    | 0    | 0x0F              | ADC sampling toggling ticker (debug)                                                     |

| GPIOF_CORE_XRDY   | 0    | 0x1D              | Digital core ready (inverted). If low, core and I2C interface are ready.                 |

#### Table 5. List of selectable functions for GPIOx pins

Note:

the INTB pin is also used as auxiliary control signal by the Graphical User Interface (GUI) during OTP flashing. This signal must be conveniently routed to the programming connector in the application (see evaluation boards as a reference)

### 5.7 Wireless power interface

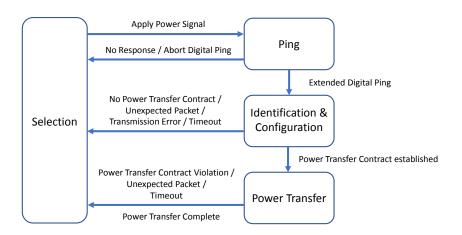

The blocks that refer to the wireless power interface are the synchronous rectifier, the main LDO linear regulator and the ASK modulator, as well as the digital core as supervisor. As previously mentioned, the power transfer from the transmitter to the receiver is actually the result of a procedure that involves different phases. In brief, a power transfer begins after the transmitter has properly detected a valid receiver and a specific communication has been established between the two parts. Without entering the details of the different phases, the basic sequence of events taking place when a receiver is properly placed on the transmitting coil are summarized as:

- Analog ping: this is the initial step of the so-called "selection phase". A brief AC burst is periodically

generated by the transmitter in order to detect the presence of a potential receiver on its transmitting

surface. Through analog ping the transmitter could eventually be able to discriminate foreign objects.

- Digital ping: this step is an interrogation session based on a more energetic AC burst during which the potential receiver is expected to reply through amplitude shift-keying (ASK) modulation.

- Identification & configuration: this is the following step aiming to identify the receiver and to gather information about its power transfer capability. The transmitter generates a so-called "Power Transfer Contract" tailoring some parameters that will characterize the following power transfer phase.

- Power transfer: this is the final step, where the transmitter initially increases and subsequently modulates the transmitted power in response to the control (feedback) data from the receiver.

#### **Power Receiver Interface**

The flow-chart visible in Figure 3 reports the whole process leading to a power transfer in Base Power Profile (BPP), the only power profile supported by STWLC68 due to a maximum output power of 5 W (1.0 A @ 5 V).

#### Figure 3. Power transfer phases for Baseline Power Profile

In case of Qi-mode the STWLC68 goes autonomously through Selection, Ping, Identification & Configuration phases, entering Power Transfer phase if no error occurs. During the Power Transfer phase, the device sends Received-Power and Control-Error packets periodically as feedback information for the transmitter. If a critical event like over-voltage, over-current or over-temperature occurs, the STWLC68 automatically sends the End-Power-Transfer packet.

When the Power Transfer is up and running, the End-Power-Transfer packet (with any response value) or any custom packet (e.g. Proprietary packet or Charge-Status packet) can be sent to the transmitter simply through commands via I<sup>2</sup>C interface. Sending a custom packet may result in a reply (either a data packet or a pattern response from the transmitter) or no reply at all: if a response is received, the content is captured and stored in specific I<sup>2</sup>C registers.

Important notes:

- Changing the output voltage must respect the overall system design (selected coil, transmitter type, etc.).

- Output load transient response strongly depends on correct design of the output capacitors. Severe load transients may lead to temporary output voltage collapse due to the overall TX-RX response time.

- A minimum output load significantly helps in increasing the signal-to-noise ratio during digital pin and it is advisable to ensure interoperability with all transmitters. For this purpose, the STWLC68 allows the user to set a dummy load (reservoir current) that is dynamically managed to fade-out when an output load is applied.

- The initial load at power-up should not exceed 2.5 W, smoothly ramping-up to full power subsequently.

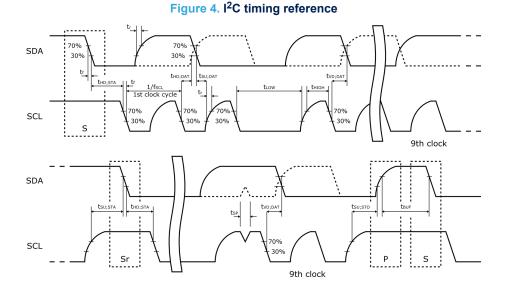

### 5.8 I2C interface

The STWLC68 can operate fully independently, i.e. without being interfaced with any host controller. In applications in which the STWLC68 has to be part of the peripherals managed by the host system, the two SDA and SCL pins could be connected to the existing I<sup>2</sup>C bus.

Thedevice works as an I<sup>2</sup>C slave and supports both standard (100 kbit/s) and fast (400 kbit/s) data transfer modes.

Through the I<sup>2</sup>C interface, maximum device flexibility is obtained and full access to the internal resources is possible. The host controller typically polls for device status and power transfer operation, demands for custom commands execution or reconfigures the default parameters.

The STWLC68 has been assigned 0x61 as 7-bit hardware address, resulting in 0xC2 and 0xC3 8-bit addresses for write and read operations respectively. Since both SDA and SCL pins of the STWLC68 have an open-drain output stage, the high level is determined by external pull-up resistors at system level. The pins are tolerant up to 5 V and the pull-up resistors should be selected as a trade-off between communication speed (lower resistors lead to faster edges) and data integrity (the input logic levels have to be guaranteed to preserve communication reliability).

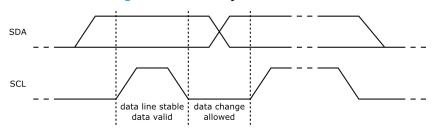

#### Data Validity

57/

As shown in Figure 5, the data on the SDA line must be stable during the high period of the clock. The high and low states of the SDA line can only change when the SCL clock signal is low.

#### Figure 5. Data validity on the I<sup>2</sup>C bus

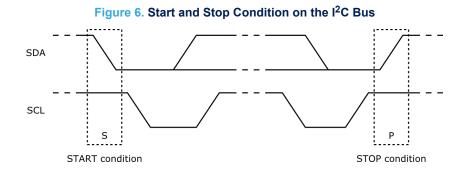

#### **Start and Stop Conditions**

Both SDA and SCL lines remain high when the I<sup>2</sup>C bus is not busy. As shown in Figure 6, a start condition is a high-to-low transition of the SDA line when SCL is high, while the stop condition is a low-to-high transition of the SDA line when SCL is high. A STOP condition must be sent before each START condition.

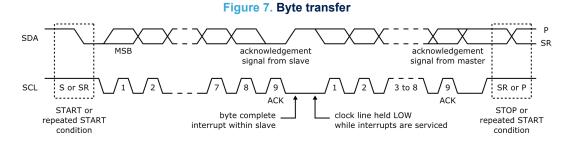

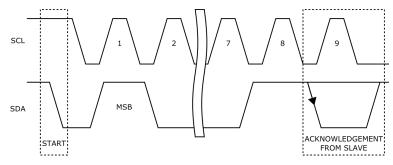

#### Byte format

Every byte transferred to the SDA line must contain 8 bits. Each byte sent to the STWLC68 is generally followed by an acknowledge (ACK) bit. The MSB is transferred first. One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high state of each SCL clock pulse.

#### Acknowledge

The I<sup>2</sup>C master releases the SDA line during the 9<sup>th</sup> SCL clock pulse in order to detect the ACK pulse eventually generated by the slave (Figure 8). The STWLC68 generates the ACK pulse (by pulling-down the SDA line during the acknowledge clock pulse) to confirm the correct device address or the received data bytes: the missing ACK pulse is a so-called not-acknowledge condition (NACK) and, apart specific cases, the master aborts the ongoing operation in such an event. If the supply voltage of the STWLC68 is too low, the I<sup>2</sup>C interface is disabled and no ACK pulses are genarated (see Under-Voltage Lockout thresholds in the Electrical Characteristics).

#### Interface protocol

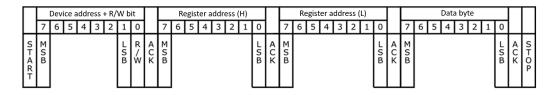

The interface protocol consists of (see Figure 9):

- start condition (START)

- 7-bit device address (0x61) + R/W bit (read =1 / write =0)

- Register pointer, high-byte

- Register pointer, low-byte

- Data sequence: N x (data byte + ACK)

- Stop condition (STOP)

The register pointer (or address) byte defines the destination register to which the read or write operation applies. When the read or write operation is finished, the register pointer is automatically incremented.

#### Figure 9. Interface protocol

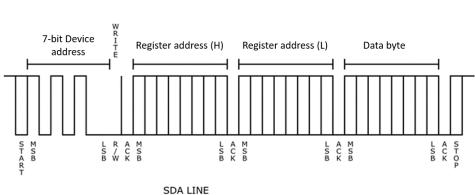

#### Writing to a single register

Writing to a single register begins with a START condition followed by device address 0xC2 (7-bit device address plus R/W bit cleared), two bytes of the register pointer and data byte to be written in the destination register. Each transmitted byte is acknowledged by the STWLC68 through an ACK pulse (Figure 10)

### Figure 10. Writing to a single register

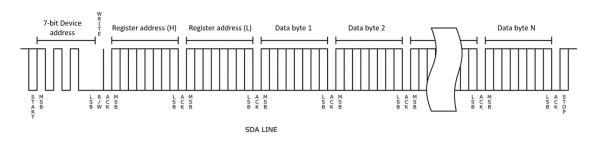

#### Writing to multiple registers (page write)

The STWLC68 supports writing to multiple registers with auto-incremental addressing. When data is written into a register, the register pointer is automatically incremented, therfore transferring data to a set of subsequent registers (also know as page write) is a straightforward operation.

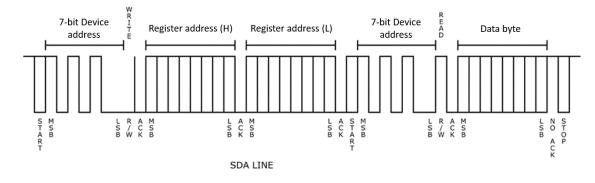

#### Reading from a single register

Reading from a single register begins with a START condition followed by device address byte 0xC2 (7-bit device address plus R/W bit cleared) and two bytes of register pointer, then a re-START condition is generated and the device address 0xC3 (7-bit device address plus R/W bit asserted) is sent, followed by data reading. As shown in Figure 12, an ACK pulse is generated by the STWLC68 at the end of each byte, but not for data bytes retrieved from the register. A STOP condition is finally generated to terminate the operation.

### Figure 12. Reading from a single register

#### Reading from multiple registers (page reading)

Similarly to multiple (page) writing, reading from subsequent registers relies on auto-increment of the register: the master can extend data reading to the following registers by generating and ACK pulse at the end of each byte. Data reading starts immediately and the stream is terminated by a NACK pulse at the end of the last data byte, followed by a STOP condition (Figure 13).

### Figure 13. Reading from multiple registers

### 5.9 Register map

The STWLC68 can be monitored and controlled by accessing the internal registers via I2C interface. The following registers map reports the accessible addresses. Registers marked with † are read-only and should not be altered by the user. Addresses not shown in the map and blank bits have to be considered reserved and not altered as well.

#### Table 6. Registers map

| Register<br>Address | Register name         | Bit 7 | Bit 6                          | Bit 5 | Bit 4          | Bit 3          | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|---------------------|-----------------------|-------|--------------------------------|-------|----------------|----------------|-------|-------|-------|--|--|--|

| 0x0000              | CHIP_ID <sup>†</sup>  |       | Chip ID                        |       |                |                |       |       |       |  |  |  |

| 0x0001              |                       |       | Cilip                          |       |                |                |       |       |       |  |  |  |

| 0x0002              | CHIP_REV <sup>†</sup> |       |                                |       | Chip R         | evision        |       |       |       |  |  |  |

| 0x0006              | DOM ID!               |       |                                |       | RO             |                |       |       |       |  |  |  |

| 0x0007              | ROM_ID <sup>†</sup>   |       |                                |       | RUI            |                |       |       |       |  |  |  |

| 0x0008              | CFG_ID <sup>†</sup>   |       |                                | C     | )TP memory c   | onfiguration I | П     |       |       |  |  |  |

| 0x0009              | CFG_ID'               |       |                                | C     |                | onnguration i  | D     |       |       |  |  |  |

| 0x000A              | TRIM_ID <sup>†</sup>  |       |                                | D     | roduction trim |                | חו    |       |       |  |  |  |

| 0x000B              |                       |       | Production trimming version ID |       |                |                |       |       |       |  |  |  |

| 0x000C              | PATCH_ID <sup>†</sup> |       |                                |       | OTP patch      | version ID     |       |       |       |  |  |  |

| Register<br>Address | Register name          | Bit 7                 | Bit 6                | Bit 5                | Bit 4               | Bit 3                   | Bit 2                  | Bit 1                  | Bit 0                      |

|---------------------|------------------------|-----------------------|----------------------|----------------------|---------------------|-------------------------|------------------------|------------------------|----------------------------|

| 0x000D              | PATCH_ID <sup>†</sup>  |                       |                      |                      | OTP patch           | version ID              |                        |                        |                            |

| 0x0010              | INT_EN                 | Out_Off_Int<br>_En    | Out_On_Int<br>_En    |                      |                     |                         | OVP_Int_E<br>n         | OCP_Int_E<br>n         | OTP_Int_E<br>n             |

| 0x0011              |                        |                       |                      |                      |                     | Vrect_Rdy_<br>Int_En    | Sig_Str_Int<br>_En     |                        |                            |

| 0x0012              | INT_CLR                | Out_Off_Int<br>_Clr   | Out_On_Int<br>_CIr   |                      |                     |                         | OVP_Int_C<br>Ir        | OCP_Int_C<br>Ir        | OTP_Int_CI<br>r            |

| 0x0013              |                        |                       |                      |                      |                     | Vrect_Rdy_<br>Int_Clr   | Sig_Str_Int<br>_Clr    |                        |                            |

| 0x0014              | INT_LATCH <sup>†</sup> | Out_Off_Int<br>_Latch | Out_On_Int<br>_Latch |                      |                     |                         | OVP_Int_L<br>atch      | OCP_Int_L<br>atch      | OTP_Int_L<br>atch          |

| 0x0015              |                        |                       |                      |                      |                     | Vrect_Rdy_<br>Int_Latch | Sig_Str_Int<br>_Latch  |                        |                            |

| 0x0016              |                        | Out_Off_Int<br>_Flag  | Out_On_Int<br>_ Flag |                      |                     |                         | OVP_Int_<br>Flag       | OCP_Int_<br>Flag       | OTP_Int_<br>Flag           |

| 0x0017              | - INT_STA <sup>†</sup> |                       |                      |                      |                     | Vrect_Rdy_<br>Int_ Flag | Sig_Str_Int<br>_ Flag  |                        |                            |

| 0x0018              | OTP_LATCH <sup>†</sup> |                       |                      |                      |                     |                         | NTC_OTP_<br>Latch      | Rect_OTP_<br>Latch     | Lin_Reg_O<br>TP_Latch      |

| 0x0019              | OVP_LATCH <sup>†</sup> |                       |                      |                      |                     |                         |                        | Fxd_OVPS<br>_Latch     | Adj_OVPS<br>_Latch         |

| 0x001A              | OCP_LATCH <sup>†</sup> |                       |                      |                      |                     |                         |                        |                        | OCP_Latch                  |

| 0x001C              | SYS_ERR0 <sup>†</sup>  |                       |                      |                      |                     |                         | ECC_Doub<br>le_Bit_Err | Header_Se<br>ction_Err | M0_Hard_<br>Fault_Err      |

| 0x001D              | SYS_ERR1 <sup>†</sup>  |                       | Sector_Error<br>:0]  | Patch_Secto          | or_Error [1:0]      | Configuratio<br>ror     | n_Sector_Er<br>[1:0]   |                        | Sector_Error<br>:0]        |

| 0x001E              | SYS_ERR2 <sup>†</sup>  |                       |                      |                      |                     |                         |                        |                        | ry_Trimming<br>Error [1:0] |

| 0x0020              |                        |                       |                      |                      |                     |                         | Send_EPT               |                        | Send_Msg                   |

| 0x0021              | DIR_CMD                |                       |                      |                      |                     |                         |                        | Out_Off                | Out_On                     |

| 0x0038              | A C EDEOt              |                       |                      | Deetil               |                     |                         |                        |                        |                            |

| 0x0039              | AC_FREQ <sup>†</sup>   |                       |                      | Rectil               | ier Operating       | Frequency (ir           | 1 KHZ)                 |                        |                            |

| 0x003A              | S_STR_TX <sup>†</sup>  |                       |                      | Signal               | Strength Lev        | el sent to tran         | smitter                |                        |                            |

| 0x003C              |                        |                       |                      |                      |                     |                         |                        |                        |                            |

| 0x003D              | VOUT_SET               |                       |                      | Output Volta         | ige setting: 25     | 5 mV to 22 V (          | 25 mV/step)            |                        |                            |

| 0x0040              | VTH_AOE                |                       | Voltage thres        | hold for Auton       | natic Output E      | Enable: 240 m           | V to 1049 mV           | ' (16 mV/step)         |                            |

| 0x0041              | LCR_THR                |                       |                      | Normal-Cu            | rrent Range (       | ,                       | Current Rang           | e (LCR) thres          | hold (4 mA/                |

| 0x0042              | LCR_HYST               |                       |                      | Low-Currer           | it Range (LCF       |                         | Current Range          | e (NCR) hyster         | resis (4 mA/               |

| 0x0043              | MOD_CFG                |                       |                      | LCR_Clam<br>p_Mod_En | LCR_Com<br>m_Mod_En |                         |                        | NCR_Clam<br>p_Mod_En   | NCR_Com<br>m_Mod_En        |

| 0x0044              | IDMYL_SET              |                       |                      |                      | Dumr                | my Load curre           | ent: 0 mA to 3         | 10 mA (10 mA           | /step)                     |

| 0x0045              | VRECT_MIN              | Vrect_Min_<br>Ctrl_En |                      |                      | Minimum \           | RECT voltag             | e (3.5V to 11V<br>VOUT | /, 0,5 V/step) f       | or constant                |

| 0x0049              | VDROP_V0               |                       |                      | Linear regu          | lator target dr     | op-out voltage          | e, setpoint 0          |                        |                            |

| 0x004A              | VDROP_V1               |                       |                      | Linear requ          | lator target dr     | op-out voltage          | e, setpoint 1          |                        |                            |

| Register<br>Address | Register name         | Bit 7      | Bit 6                                                                                                                          | Bit 5         | Bit 4           | Bit 3            | Bit 2           | Bit 1          | Bit 0           |  |  |  |

|---------------------|-----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|------------------|-----------------|----------------|-----------------|--|--|--|

| 0x004B              | VDROP_V2              |            |                                                                                                                                | Linear reg    | ulator target d | rop-out voltage  | e, setpoint 2   |                |                 |  |  |  |

| 0x004C              | VDROP_V3              |            |                                                                                                                                | Linear reg    | ulator target d | rop-out voltage  | e, setpoint 3   |                |                 |  |  |  |

| 0x004D              | VDROP_C1              |            | Li                                                                                                                             | near regulato | r target drop-o | out voltage, cu  | rrent threshol  | d 1            |                 |  |  |  |

| 0x004E              | VDROP_C2              |            | Linear regulator target drop-out voltage, current threshold 2<br>Linear regulator target drop-out voltage, current threshold 3 |               |                 |                  |                 |                |                 |  |  |  |

| 0x004F              | VDROP_C3              |            | Li                                                                                                                             | near regulato | r target drop-o | out voltage, cu  | rrent threshol  | d 3            |                 |  |  |  |

| 0x0050              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0051              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0052              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0053              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0054              | MSG_TX                | Messa      | essage packet content to be sent to transmitter via ASK modulation (see DIR_CMG register)                                      |               |                 |                  |                 |                |                 |  |  |  |

| 0x0055              | -                     |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0056              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0057              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0058              | -                     |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x0062              | EPT_MSG               |            | EPT Messag                                                                                                                     | ge (root caus | e event) adde   | d to EPT pack    | et (see DIR_C   | CMD register)  |                 |  |  |  |

| 0x0080              | FOD_CTC               |            |                                                                                                                                | FC            | D Current Thr   | eshold Calibra   | ation           |                |                 |  |  |  |

| 0x0083              | FOD_GSC               |            |                                                                                                                                |               | FOD Gain Sc     | aler Calibratio  | n               |                |                 |  |  |  |

| 0x0087              | FOD_OLC               |            |                                                                                                                                |               | FOD Offset L    | evel Calibratio  | n               |                |                 |  |  |  |

| 0x008B              | FOD_DCR               |            |                                                                                                                                | Coil I        | DC-Resistance   | e for FOD calc   | ulation         |                |                 |  |  |  |

| 0x0090              |                       | Voltage Re | gulation Error                                                                                                                 | difference in | n mV) betweer   | n actual and ta  | arget VRECT,    | used to calcul | ate CEP for     |  |  |  |

| 0x0091              | VRECT_RE <sup>†</sup> |            | 0                                                                                                                              | · ·           |                 | nsmitter         | 0               |                |                 |  |  |  |

| 0x0092              |                       |            |                                                                                                                                | <b>_</b> (    |                 |                  |                 |                |                 |  |  |  |

| 0x0093              | RPP_TX <sup>†</sup>   |            | Received                                                                                                                       | Power (comp   | prehensive of I | osses) level P   | acket sent to   | transmitter    |                 |  |  |  |

| 0x0096              | SS_MIN_TX             |            | Mir                                                                                                                            | nimum Signal  | -Strength leve  | l for proceedi   | ng to PING ph   | ase            |                 |  |  |  |

| 0x0097              | CS_OFFS <sup>†</sup>  |            |                                                                                                                                | Curre         | nt sensor offse | et adjustment    | (in mA)         |                |                 |  |  |  |

| 0x0098              | IDLE_CC               |            |                                                                                                                                | Chip          | idle current c  | onsumption (i    | n mA)           |                |                 |  |  |  |

| 0x00A1              | PMAX_PTC              |            |                                                                                                                                | Maxim         | um power cap    | ability establis | hed during Po   | ower Transfer  | Contract        |  |  |  |

| 0x00A6              | TREAT OTR             |            | Over Temp                                                                                                                      |               | tion Throphold  | related to De    | otifics Tompor  | atura concor   |                 |  |  |  |

| 0x00A7              | TRECT_OTP             |            | Over-remp                                                                                                                      |               | tion Threshold  |                  | culler remper   | alure sensor   |                 |  |  |  |

| 0x00A8              |                       | 0          | Teneresture                                                                                                                    | data atian Th |                 | d to uppin Line  | an Danulatan T  |                |                 |  |  |  |

| 0x00A9              | TLR_OTP               | Over-      | - Temperature                                                                                                                  | detection In  | reshold related | d to main Line   | ar Regulator    | remperature s  | ensor           |  |  |  |

| 0x00AA              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x00AB              | VNTC_OTP              |            | Over-                                                                                                                          | Iemperature   | detection Thr   | eshold related   | to external N   | I C pin        |                 |  |  |  |

| 0x00AC              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |

| 0x00AD              | VRECT_OVP             |            | VREC                                                                                                                           | Over-Voltag   | e detection Th  | iresnoid (Adju   | Istable OVP-C   | lamper)        |                 |  |  |  |

| 0x00AE              |                       |            |                                                                                                                                |               |                 |                  |                 |                |                 |  |  |  |