# SAA8200HL

# **Ensation™ Base integrated wireless audio baseband**

Rev. 01 — 17 December 2004

**Objective data sheet**

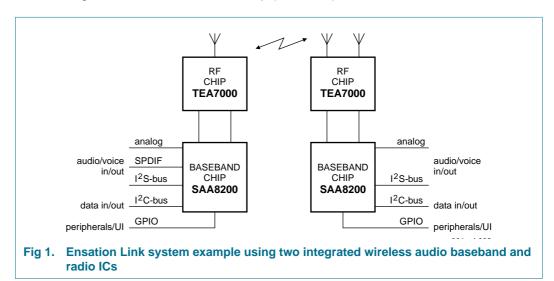

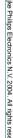

The Ensation™ Base, SAA8200HL, is part of the integrated wireless audio system chip set offered by Philips. This chip set enables the development of low cost wireless digital audio systems. The chip set contains:

- An integrated wireless audio baseband chip (SAA8200HL)

- An integrated wireless audio radio chip (TEA7000).

Integrating a wireless audio link in a home theatre system to remove part of the wiring is a logical application of wireless audio transmission. A very important property of this wireless audio system is the low end-to-end (audio-in at transmit side to audio-out at receive side) system latency, which is below 20 ms.

A second important property is the robustness and reliability of the wireless audio link, the SAA8200HL which is handling the signal processing and the system control enables this.

Furthermore, the SAA8200HL provides the flexibility to allow designers to make trade-offs between air bit-rate, number of transported audio channels, audio formats, audio coding bit-rates, range, number of receiving-slaves and more.

Due to its low power consuming design, the SAA8200HL enables battery powered applications. The SAA8200HL does this all with a minimum of external components due to its high level of integration.

### Ensation™ Base integrated wireless audio baseband

Together with the TEA7000, the SAA8200HL can be used to implement an indoor wireless link for audio applications (system specific). Together with an AV-compliant Bluetooth radio module, the SAA8200HL can be used to implement a Bluetooth wireless audio functionality.

The SAA8200HL enables a low power, low cost two-chip solution with a maximum amount of functions integrated on the SAA8200HL, taking into account strict time-to-market constraints.

## 2. Features

#### 2.1 General

- Programmable baseband processor and system controller for cable replacement wireless audio

- Supports various audio compression formats

- Wireless audio protocol can make trade-off between quality, number of channels, bandwidth and range

- Supports various transmission frequencies

- High integration allows for two-chip applications

- Embedded ROM with wireless audio software library.

### 2.2 Hardware

- Audio PLL and system PLL

- Read-Solomon encoder and decoder

- SPDIF interface

- Low cost low power EPICS7B DSP core with hardware debugger and JTAG interface

- Integrated memories:

- ◆ 24/6 kWords program ROM/RAM (bit width: 32 bits)

- ◆ 12 kWords X data RAM (bit width: 24 bits)

- ◆ 12/2 kWords Y data ROM/RAM (bit width: 12 bits).

- Interrupt controller

- DMA controller

- Oscillator and time base unit with programmable clocks

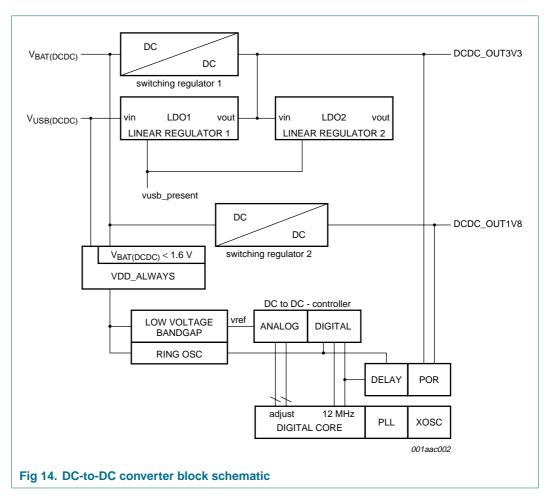

- Embedded LDO regulators and DC-to-DC converters for on-chip and off-chip supply voltage needs

- Power control unit

- Power on and power off switching with battery supply

- Reed-Solomon codec unit

- Serial radio interface unit

- High speed UART

- General purpose digital I/O block with 14 inputs, all of which generate interrupts

- I<sup>2</sup>C-bus master/slave

- I<sup>2</sup>C-bus for radio chip control

- Control 10-bit ADC with four inputs

### Ensation™ Base integrated wireless audio baseband

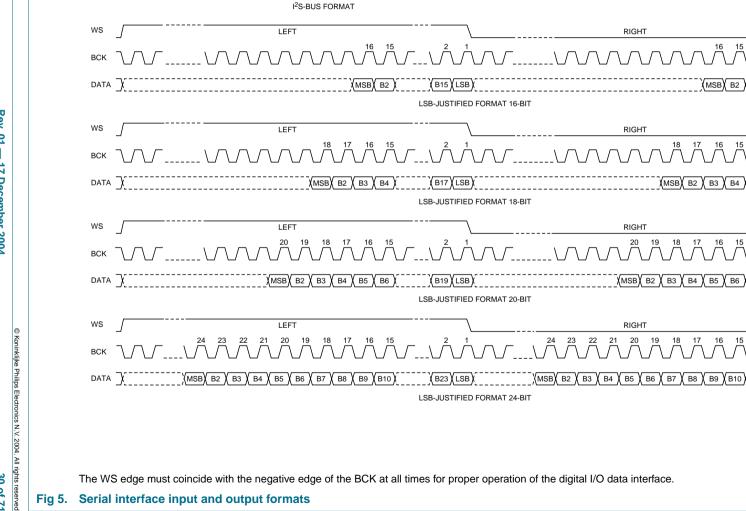

- Two serial (I<sup>2</sup>S-bus/Japanese) digital audio inputs with independent clocks and word-select

- Two serial (I<sup>2</sup>S-bus/Japanese) digital audio outputs with shared clock and word-select

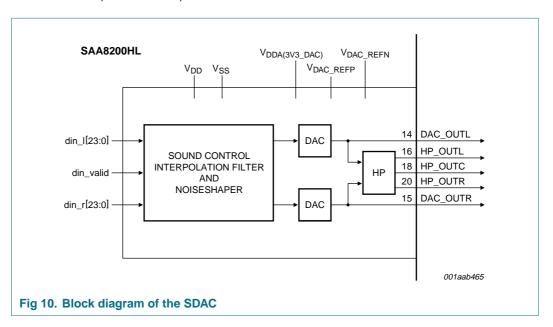

- Integrated 16-bit stereo DAC (line output)

- Integrated stereo headphone amplifier

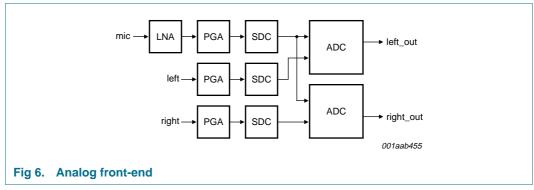

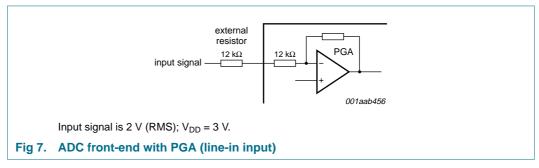

- Programmable Gain Amplifier (PGA) (line input)

- Low noise microphone amplifier (microphone input)

- Integrated 16-bit stereo ADC

- Watchdog timer.

### 2.3 Software

- Stereo Sub Band Coding (SBC) encoder/decoder

- Stereo MPEG layer 3 (MP3) decoder

- Reed-Solomon encoder/decoder driver

- Sample rate converter

- I<sup>2</sup>C-bus master/slave driver

- Serial radio interface driver

- RF radio chip driver

- UART driver

- Control 10-bit ADC driver

- Power consumption management

- ADC, DAC and headphone driver

- Wireless audio protocol library.

# 3. Applications

- Wireless front speakers or wireless surround speakers for home theatre

- Wireless indoor headphones

- Wireless second room audio sets

- Wireless headsets.

# 4. Ordering information

Table 1: Ordering information

| Type number | Package |                                                                                     |          |  |  |

|-------------|---------|-------------------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                                         | Version  |  |  |

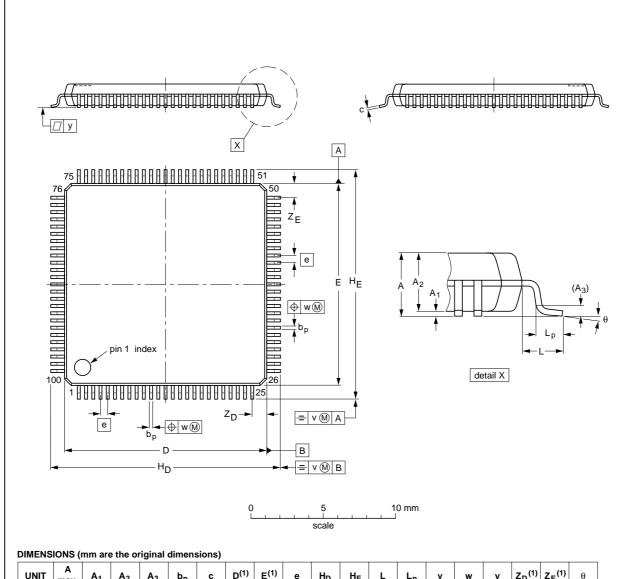

| SAA8200HL   | LQFP100 | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm | SOT407-1 |  |  |

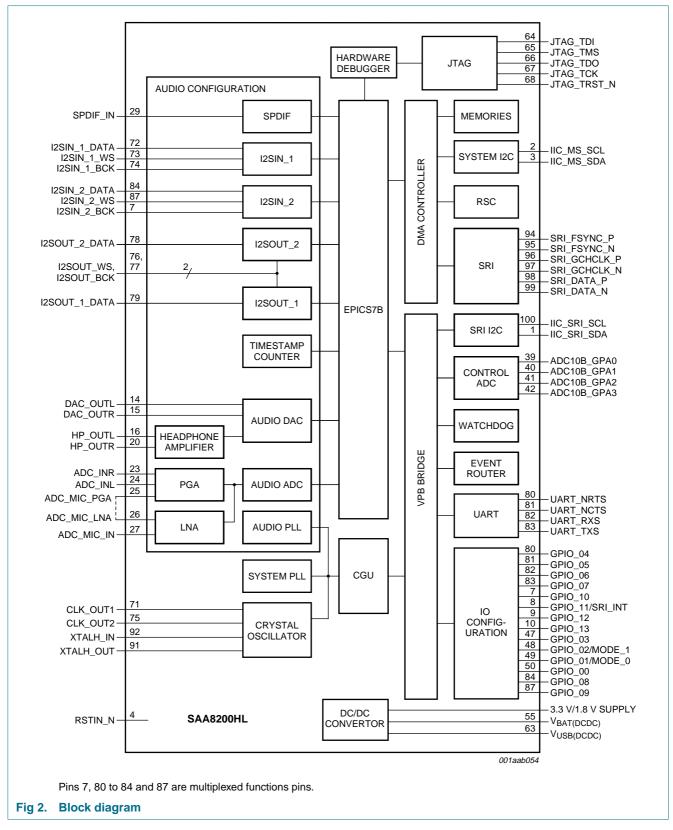

# 5. Block diagram

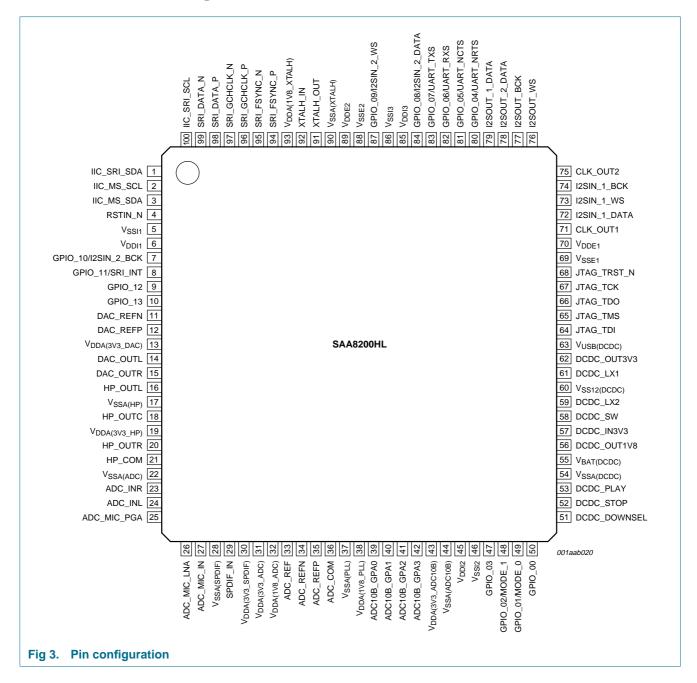

# 6. Pinning information

# 6.1 Pinning

# 6.2 Pin description

Table 2: Pin description

| Symbol                           | Pin | Special 11 | Туре    | Description                                   |

|----------------------------------|-----|------------|---------|-----------------------------------------------|

| Digital supply voltage p         | ins |            |         |                                               |

| V <sub>SSI1</sub>                | 5   |            | vssi    | core ground                                   |

| V <sub>DDI1</sub>                | 6   |            | vddi    | core supply voltage                           |

| V <sub>SSE1</sub>                | 69  |            | vsse3v3 | core ground                                   |

| $V_{DDE1}$                       | 70  |            | vdde3v3 | core supply voltage                           |

| V <sub>SSE2</sub>                | 88  |            | vsse3v3 | core ground                                   |

| $V_{DDE2}$                       | 89  |            | vdde3v3 | core supply voltage                           |

| $V_{DDI2}$                       | 45  |            | vddco   | core supply voltage                           |

| V <sub>SSI2</sub>                | 46  |            | VSSCO   | core ground                                   |

| $V_{DDI3}$                       | 85  |            | vddco   | core supply voltage                           |

| V <sub>SSI3</sub>                | 86  |            | VSSCO   | core ground                                   |

| DC-to-DC converter               |     |            |         |                                               |

| V <sub>USB(DCDC)</sub>           | 63  | Α          | vddco   | USB supply voltage (linear regulator)         |

| DCDC_OUT3V3                      | 62  | Α          | vddco   | 3.3 V output voltage                          |

| DCDC_LX1                         | 61  | Α          | vddco   | coil connection for 3.3 V converter           |

| V <sub>SSI2(DCDC)</sub>          | 60  | Α          | VSSCO   | ground for switches 1.8 V and 3.3 V converter |

| DCDC_LX2                         | 59  | A          | vddco   | coil connection for 1.8 V converter           |

| DCDC_SW                          | 58  | Α          | vddco   | switch node                                   |

| DCDC_IN3V3                       | 57  | Α          | vddco   | 3.3 V input voltage                           |

| DCDC_OUT1V8                      | 56  | A          | vddco   | 1.8 V output voltage                          |

| V <sub>BAT(DCDC)</sub>           | 55  | A          | vddco   | battery supply voltage                        |

| V <sub>SSA(DCDC)</sub>           | 54  | Α          | VSSCO   | ground double bonded clean and substrate      |

| DCDC_PLAY                        | 53  | Α          | apio    | play button signal                            |

| DCDC_STOP                        | 52  | Α          | apio    | stop button signal                            |

| DCDC_DOWNSEL  Crystal oscillator | 51  | Α          | apio    | one ore two battery selection                 |

| V <sub>SSA(XTALH)</sub>          | 90  |            | VSSCO   | analog ground                                 |

| XTALH_OUT                        | 91  |            | apio    | 11.025 MHz clock output                       |

| XTALH_IN                         | 92  |            | apio    | 11.025 MHz clock input                        |

| V <sub>DDA(1V8</sub> XTALH)      | 93  |            | vddco   | analog supply voltage                         |

| PLL                              |     |            |         |                                               |

| V <sub>DDA(1V8_PLL)</sub>        | 38  |            | vddco   | analog supply voltage                         |

| V <sub>SSA(PLL)</sub>            | 37  |            | VSSCO   | analog ground                                 |

| Serial radio interface           |     |            |         | 5 5                                           |

| SRI_FSYNC_P                      | 94  | A          | apio    | frame sync positive                           |

| SRI_FSYNC_N                      | 95  | A          | apio    | frame sync negative                           |

| SRI_GCHCLK_P                     | 96  | A          | apio    | gated channel clock positive                  |

| SRI_GCHCLK_N                     | 97  | Α          | apio    | gated channel clock negative                  |

# Ensation™ Base integrated wireless audio baseband

Table 2:

Pin description ...continued

| Symbol                                  | Pin  | Special [1] | Туре        | Description                                                       |

|-----------------------------------------|------|-------------|-------------|-------------------------------------------------------------------|

| SRI_DATA_P                              | 98   | A           | apio        | data positive                                                     |

| SRI_DATA_N                              | 99   | Α           | apio        | data negative                                                     |

| Serial radio interface I <sup>2</sup> C | -bus |             |             |                                                                   |

| IIC_SRI_SCL                             | 100  |             | iic400kt5v  | clock input                                                       |

| IIC_SRI_SDA                             | 1    |             | iic400kt5v  | data input or output                                              |

| Audio ADC                               |      |             |             |                                                                   |

| ADC_COM                                 | 36   | Α           | apio        | common mode reference voltage                                     |

| ADC_REFP                                | 35   | Α           | apio        | positive reference voltage                                        |

| ADC_REFN                                | 34   | А           | apio        | negative reference voltage                                        |

| ADC_REF                                 | 33   | A           | apio        | reference voltage                                                 |

| V <sub>DDA(3V3_ADC)</sub>               | 31   | А           | vddco       | analog supply voltage (3.3 V)                                     |

| V <sub>DDA(1V8_ADC)</sub>               | 32   | Α           | vddco       | analog supply voltage (1.8 V)                                     |

| V <sub>SSA(ADC)</sub>                   | 22   | Α           | VSSCO       | analog ground                                                     |

| ADC_INR                                 | 23   | A           | apio        | right input voltage                                               |

| ADC_INL                                 | 24   | Α           | apio        | left input voltage                                                |

| ADC_MIC_PGA                             | 25   | А           | apio        | PGA input for AC coupling                                         |

| ADC_MIC_LNA                             | 26   | А           | apio        | LNA output for AC coupling                                        |

| ADC_MIC_IN                              | 27   | Α           | apio        | microphone input                                                  |

| Audio DAC                               |      |             |             |                                                                   |

| DAC_REFN                                | 11   | Α           | apio        | negative reference voltage                                        |

| DAC_REFP                                | 12   | Α           | apio        | positive reference voltage                                        |

| V <sub>DDA(3V3_DAC)</sub>               | 13   | Α           | vddco       | analog supply voltage                                             |

| DAC_OUTL                                | 14   | Α           | apio        | left line output voltage                                          |

| DAC_OUTR                                | 15   | Α           | apio        | right line output voltage                                         |

| Headphone                               |      |             |             |                                                                   |

| HP_COM                                  | 21   | Α           | apio        | common mode reference voltage                                     |

| HP_OUTR                                 | 20   | Α           | apio        | right output voltage                                              |

| V <sub>DDA(3V3_HP)</sub>                | 19   | Α           | vddco       | analog supply voltage                                             |

| HP_OUTC                                 | 18   | Α           | apio        | common output voltage                                             |

| V <sub>SSA(HP)</sub>                    | 17   | Α           | VSSCO       | analog ground                                                     |

| HP_OUTL                                 | 16   | Α           | apio        | left output voltage                                               |

| SPDIF                                   |      |             |             |                                                                   |

| V <sub>DDA(3V3_SPDIF)</sub>             | 30   | Α           | vddco       | analog supply voltage                                             |

| SPDIF_IN                                | 29   | Α           | apio        | input voltage                                                     |

| V <sub>SSA(SPDIF)</sub>                 | 28   | Α           | VSSCO       | analog ground                                                     |

| I <sup>2</sup> S-bus input              |      |             |             |                                                                   |

| I2SIN_1_DATA                            | 72   | I           | iptht5v     | serial data channel 1                                             |

| I2SIN_1_WS                              | 73   | I/O         | bpts10tht5v | word select channel 1                                             |

| I2SIN_1_BCK                             | 74   | I/O         | bpts10tht5v | bit clock channel 1                                               |

| GPIO_10/I2SIN_2_BCK                     | 7    | I/O         | bpts10tht5v | general purpose IO/I <sup>2</sup> S-bus input bit clock channel 2 |

# Ensation™ Base integrated wireless audio baseband

Table 2:

Pin description ...continued

| Symbol                       | Pin | Special [1] | Туре        | Description                                                         |

|------------------------------|-----|-------------|-------------|---------------------------------------------------------------------|

| GPIO_09/I2SIN_2_WS           | 87  | I/O         | bpts10tht5v | general purpose IO/I <sup>2</sup> S-bus input word select channel 1 |

| GPIO_08/I2SIN_2_DATA         | 84  | I/O         | bpts10tht5v | general purpose IO/I <sup>2</sup> S-bus input serial data channel 2 |

| I <sup>2</sup> S-bus output  |     |             |             |                                                                     |

| I2SOUT_WS                    | 76  | I/O         | bpts10tht5v | word select                                                         |

| I2SOUT_BCK                   | 77  | I/O         | bpts10tht5v | bit clock                                                           |

| I2SOUT_2_DATA                | 78  | 0           | ots10ct5v   | serial data channel 2                                               |

| I2SOUT_1_DATA                | 79  | 0           | ots10ct5v   | serial data channel 1                                               |

| Control ADC                  |     |             |             |                                                                     |

| V <sub>SSA(ADC10B)</sub>     | 44  | Α           | VSSCO       | analog ground                                                       |

| V <sub>DDA(3V3_ADC10B)</sub> | 43  | Α           | vddco       | analog supply voltage                                               |

| ADC10B_GPA3                  | 42  | Α           | apio        | analog general purpose input 3                                      |

| ADC10B_GPA2                  | 41  | Α           | apio        | analog general purpose input 2                                      |

| ADC10B_GPA1                  | 40  | A           | apio        | analog general purpose input 1                                      |

| ADC10B_GPA0                  | 39  | A           | apio        | analog general purpose input 0                                      |

| GPIO                         |     |             |             |                                                                     |

| GPIO_13                      | 10  | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_12                      | 9   | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_11/SRI_INT              | 8   | I/O         | <tbd></tbd> | general purpose IO                                                  |

| GPIO_10/I2SIN_2_BCK          | 7   | I/O         | bpts10tht5v | general purpose IO/I <sup>2</sup> S-bus input bit clock channel 2   |

| GPIO_09/I2SIN_2_WS           | 87  | I/O         | bpts10tht5v | general purpose IO/I <sup>2</sup> S-bus input word select channel 1 |

| GPIO_08/I2SIN_2_DATA         | 84  | I/O         | bpts10tht5v | general purpose IO/I <sup>2</sup> S-bus input serial data channel 2 |

| GPIO_07/UART_TXS             | 83  | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_06/UART_RXS             | 82  | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_05/UART_NCTS            | 81  | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_04/UART_NRTS            | 80  | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_03                      | 47  | I/O         | bpts10tht5v | general purpose IO                                                  |

| GPIO_02/MODE_1               | 48  | I/O         | bpts10tht5v | general purpose IO/boot-up mode selection pin 1                     |

| GPIO_01/MODE_0               | 49  | I/O         | bpts10tht5v | general purpose IO/boot-up mode selection pin 0                     |

| GPIO_00                      | 50  | I/O         | bpts10tht5v | general purpose IO                                                  |

| System I <sup>2</sup> C-bus  |     |             |             |                                                                     |

| IIC_MS_SCL                   | 2   |             | iic400kt5v  | clock input or output                                               |

| IIC_MS_SDA                   | 3   |             | iic400kt5v  | data input or output                                                |

| Other                        |     |             |             |                                                                     |

| CLK_OUT2                     | 75  | 0           | ots10ct5v   | clock output 2                                                      |

| CLK_OUT1                     | 71  | 0           | ots10ct5v   | clock output 1                                                      |

| RSTIN_N                      | 4   | I           | ipthu5v     | system reset input                                                  |

| Symbol      | Pin | Special [1] | Туре      | Description       |

|-------------|-----|-------------|-----------|-------------------|

| JTAG        |     |             |           |                   |

| JTAG_TRST_N | 68  | I           | ipthdt5v  | reset input       |

| JTAG_TCK    | 67  | I           | ipthdt5v  | clock input       |

| JTAG_TDI    | 64  | I           | ipthdt5v  | data input        |

| JTAG_TMS    | 65  | I           | ipthdt5v  | mode select input |

| JTAG_TDO    | 66  | 0           | ots10ct5v | data output       |

<sup>[1]</sup> A = analog. I = input. O = output.

Table 3: Cell types description

| Cell name   | Definition                                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------|

| iptht5v     | input pad; push pull; TTL with hysteresis; 5 V tolerant                                                                   |

| ipthu5v     | input pad; push pull; TTL with hysteresis; pull-up; 5 V tolerant                                                          |

| ipthdt5v    | input pad; push pull; TTL with hysteresis; pull-down; 5 V tolerant                                                        |

| ots10ct5v   | output pad; 3-state; 10 ns slew rate control; 5 V tolerant                                                                |

| bpts10tht5v | bi-directional pad; plain input; 3-state output; 10 ns slew rate control; TTL with hysteresis; 5 V tolerant               |

| iic400kt5v  | I <sup>2</sup> C-bus pad; 400 kHz I <sup>2</sup> C-bus specification; 5 V tolerant                                        |

| apio        | analog pad; analog input/output                                                                                           |

| vddi        | $\rm V_{DD}$ pad connected to core $\rm V_{DD}$ and internal $\rm V_{DD}$ supply voltage rail in I/O ring                 |

| vddco       | V <sub>DD</sub> pad connected to core V <sub>DD</sub>                                                                     |

| vdde3v3     | $V_{DD}$ pad connected to external 3.3 V $V_{DD}$ supply voltage rail                                                     |

| VSSCO       | V <sub>SS</sub> pad connected to core V <sub>SS</sub>                                                                     |

| vsse3v3     | V <sub>SS</sub> pad connected to external 3.3 V V <sub>SS</sub> supply voltage rail                                       |

| vssi        | $V_{SS}$ pad connected to core $V_{SS};$ internal $V_{SS}$ supply voltage rail in I/O ring and substrate rail in I/O ring |

# 7. Functional description

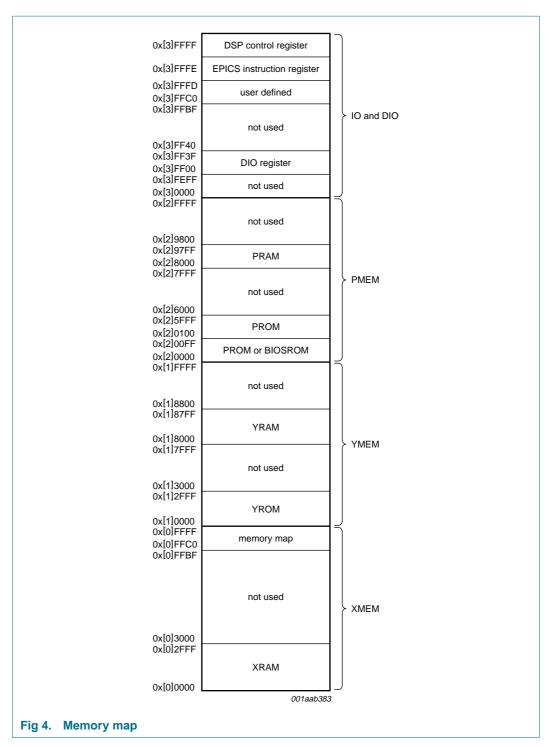

### 7.1 EPICS7B

The EPICS7B core has only access to four of the five memory spaces, PMEM, XMEM, YMEM and DIO. Memory space IO is only accessible via the DMA. To distinguish between the memory spaces, 18-bit addressing is used, of which the two Most Significant (MS) bits determine which space the address is in, see <a href="Table 4">Table 4</a>. The EPICS7B only knows about the 16 least significant bits and uses special instructions to access DIO space.

### EPICS7B access:

XMEM is accessed by EPICS7B when using X in its instructions YMEM is accessed by EPICS7B when using Y in its instructions PMEM is accessed by EPICS7B when it is fetching instructions DIO is accessed by EPICS7B when using D in its instructions.

All 18 bits are used when accessing memory via DMA.

Table 4: Memory spaces

| Two MS bits | Memory space |

|-------------|--------------|

| 00          | XMEM         |

| 01          | YMEM         |

| 10          | PMEM         |

| 11          | DIO or IO    |

The memory map of the system is described in Table 5 and Figure 4.

Table 5: Memory map

| Address                | Туре                         | Words | Bits |

|------------------------|------------------------------|-------|------|

| Ю                      |                              |       |      |

| 0x[3]FFFF              | DSP control register         | 64    | 32   |

| 0x[3]FFFE              | EPICS7B instruction register |       | 32   |

| 0x[3]FFC0 to 0x[3]FFFD | user defined                 | 64    | 32   |

| DIO                    |                              |       |      |

| 0x[3]FF00 to 0x[3]FF3F | DIO registers                |       | 24   |

| PMEM                   |                              |       |      |

| 0x[2]8000 to 0x[2]97FF | PRAM                         | 6144  |      |

| 0x[2]0000 to 0x[2]5FFF | PROM[1]                      | 24576 |      |

| 0x[2]0000 to 0x[2]00FF | BIOSROM [1]                  |       |      |

| YMEM                   |                              |       |      |

| 0x[1]8000 to 0x[1]87FF | YRAM                         | 2048  |      |

| 0x[1]0000 to 0x[1]2FFF | YROM                         | 12288 |      |

| XMEM                   |                              |       |      |

| 0x[0]FFC0 to 0x[0]FFFF | memory mapped registers      |       |      |

| 0x[0]0000 to 0x[0]2FFF | XRAM                         | 12288 |      |

<sup>[1]</sup> DSP control register bit 0 is selecting PROM or BIOSROM.

### Ensation™ Base integrated wireless audio baseband

The control registers are split in two different spaces. One space is accessible only via DMA while the other space is accessible both via DMA and the DSP core. This space is therefore X-memory mapped.

The location and definition of the control registers is described in Table 6.

| Register name     | Address  | R/W | Description                  | Reset     |

|-------------------|----------|-----|------------------------------|-----------|

| DSP               |          |     |                              |           |

| PC                | 0x0 FFFF | W   | program counter register     | undefined |

| SR1               | 0x0 FFFE | W   | status register 1            | undefined |

| SR2               | 0x0 FFFD | W   | status register 2            | undefined |

| RTI_STACK         | 0x0 FFFC | W   | interrupt stack register     | undefined |

| IO_DIR            | 0x0 FFFB | W   | configuration register 1     | 0x00 0000 |

| IO_MODE           | 0x0 FFFA | W   | configuration register 2     | 0x00 0FFD |

| CR                | 0x3 FFFF | W   | control register I/O mapped  | 0x00 0000 |

| EIR               | 0x3 FFFE | W   | EPICS7B instruction register | 0x00 0000 |

| Interrupt control | ler      |     |                              |           |

| INTC_POL          | 0x0 FFF9 | W   | polarity select              | 0x03 FFFF |

| INTC_MODE         | 0x0 FFF8 | W   | mode select                  | 0x03 FFFF |

| INTC_MASK         | 0x0 FFF7 | W   | mask                         | 0x03 FFFF |

| INTC_STATUS       | 0x0 FFF6 | R   | status                       | undefined |

| INTC_TEST         | 0x0 FFF5 | W   | test                         | 0x00 0001 |

| INTC_SWCLR        | 0x0 FFF4 | W   | software clear               | 0x00 0000 |

| INTC_SLCT         | 0x0 FFF3 | W   | user flag                    | 0x00 0000 |

| DMA controller    |          |     |                              |           |

| DMAC_IC           | 0x0 FFF2 | R   | IRQ counter value            | 0x00 0000 |

The interrupts and connection order are described in <a>Table 7</a>.

Table 7: Interrupt flags

| Interrupt flag | Symbol            | Description                                           |

|----------------|-------------------|-------------------------------------------------------|

| 0              | fi_dmac           | DMAC interrupt                                        |

| 1              | fi_sri_dma_rx_rdy | SRI RX DMA block transfer interrupt                   |

| 2              | fi_flstart        | FSL start interrupt                                   |

| 3              | fi_eventrouter    | event router interrupt                                |

| 4              | fi_sri_dma_tx_rdy | SRI TX DMA block transfer interrupt                   |

| 5              | fi_i2sin_1        | I <sup>2</sup> S-bus input 1 interrupt                |

| 6              | fi_i2sin_2        | I <sup>2</sup> S-bus input 2 interrupt                |

| 7              | fi_spdif          | SPDIF input interrupt                                 |

| 8              | fi_adc            | ADC input interrupt                                   |

| 9              | fi_dacall         | I <sup>2</sup> S-bus and DAC outputs interrupt        |

| 10             | fi_rsc_encrdy     | RSC encoder ready interrupt                           |

| 11             | fi_rsc_decrdy     | RSC decoder ready interrupt                           |

| 12             | fi_rsc_dmardy     | RSC DMA block transfer ready interrupt                |

| 13             | fi_vpb0           | VPB0 interrupt                                        |

| 14             | fi_vbp1           | VPB1 interrupt                                        |

| 15             | fi_uart           | UART interrupt                                        |

| 16             | fi_i2c_dmardy     | I <sup>2</sup> C-bus M/S DMA block transfer interrupt |

| 17             | fi_fslfast        | FSL fast interrupt                                    |

|                |                   |                                                       |

The outputs of the ADC,  $I^2S$ -bus inputs, SPDIF inputs and VPB buses are mapped to the inputs of the EPICS7B.

Table 8: DIO input registers

| DIO input register | Register name | Description                                |

|--------------------|---------------|--------------------------------------------|

| 0                  | I2SIN_1L      | I <sup>2</sup> S-bus input 1 left channel  |

| 1                  | I2SIN_1R      | I <sup>2</sup> S-bus input 1 right channel |

| 2                  | I2SIN_2L      | I <sup>2</sup> S-bus input 2 left channel  |

| 3                  | I2SIN_2R      | I <sup>2</sup> S-bus input 2 right channel |

| 4                  | SPDIF L       | SPDIF input left channel                   |

| 5                  | SPDIF R       | SPDIF input right channel                  |

| 6                  | ADC_L         | ADC input left channel                     |

| 7                  | ADC_R         | ADC input right channel                    |

| 8                  | VPB0_DI1      | VPB0 data input 1 (bit 0 to bit 15)        |

| 9                  | VPB0_DI2      | VPB0 data input 2 (bit 16 to bit 31)       |

| 10                 | VPB1_DI       | VPB1 data input (UART)                     |

| 11                 | TS_COUNTER    |                                            |

| 12                 | I2SIN_1TS     | time stamp counter i2sin1                  |

| 13                 | I2SIN_2TS     | time stamp counter i2sin2                  |

| 14                 | SPDIF_TS      | time stamp counter spdif                   |

| 15                 | ADC_TS        | time stamp counter adc                     |

| 16                 | I2SOUT_TS     | time stamp counter i2sout                  |

| 17                 | TS_COUNTER    |                                            |

The control of the DAC, I<sup>2</sup>S-bus outputs and VPB buses are mapped to the outputs of the EPICS7B.

Table 9: DIO output registers

| DIO output register | Register name | Description                                 |

|---------------------|---------------|---------------------------------------------|

| 0                   | I2SOUT_1L     | I <sup>2</sup> S-bus output 1 left channel  |

| 1                   | I2SOUT_1R     | I <sup>2</sup> S-bus output 1 right channel |

| 2                   | I2SOUT_2L     | I <sup>2</sup> S-bus output 2 left channel  |

| 3                   | I2SOUT_2R     | I <sup>2</sup> S-bus output 2 right channel |

| 4                   | DAC_L         | DAC output left channel                     |

| 5                   | DAC_R         | DAC output right channel                    |

| 6                   | not connected |                                             |

| 7                   | not connected |                                             |

| 8                   | VPB0_DO1      | VPB0 data output 1 (bit 0 to bit 15)        |

| 9                   | VPB0_DO2      | VPB0 data output 2 (bit 16 to bit 31)       |

| 10                  | VPB0_ADDR     | VPB0 address                                |

| 11                  | VPB1_DO       | VPB1 data output (UART)                     |

| 12                  | VPB1_ADDR     | VPB1 address                                |

| 13                  | not connected |                                             |

| 14                  | not connected |                                             |

# **Ensation™ Base integrated wireless audio baseband**

Table 9: DIO output registers ...continued

| DIO output register | Register name | Description |

|---------------------|---------------|-------------|

| 15                  | not connected |             |

| 16                  | not connected |             |

| 17                  | not connected |             |

# 7.1.1 User registers

The user registers are memory mapped control signals used to control integrated wireless audio baseband functionality.

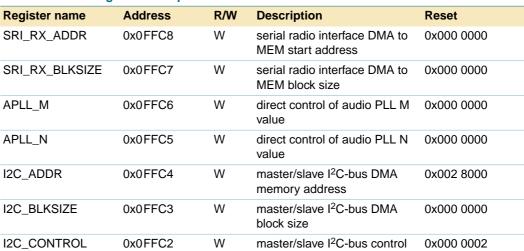

Table 10: User register description

| Register name  | Address  | R/W | Description                                              | Reset      |

|----------------|----------|-----|----------------------------------------------------------|------------|

| SRI_TX_ADDR    | 0x0 FFDE | W   | serial radio interface DMA from MEM start address        | 0x000 0000 |

| SRI_TX_BLKSIZE | 0x0 FFDD | W   | serial radio interface DMA from MEM block size           | 0x000 0000 |

| SRI_MODE       | 0x0 FFDC | W   | serial radio interface mode control                      | 0x000 0000 |

| SRIM_TSTART    | 0x0FFDB  | W   | serial radio interface master mode start time            | 0x000 0000 |

| SRIM_TLINK     | 0x0 FFDA | W   | serial radio interface master mode sync-link time        | 0x000 0000 |

| SRIM_TIDLE     | 0x0 FFD9 | W   | serial radio interface master mode idle time             | 0x000 0000 |

| SRIM_DLLEN     | 0x0 FFD8 | W   | serial radio interface master mode number downlink words | 0x000 0000 |

| SRIM_ULLEN     | 0x0 FFD7 | W   | serial radio interface master mode number uplink words   | 0x000 0000 |

| FSL_MODE       | 0x0 FFD6 | W   | frame sync lock mode control                             | 0x000 0000 |

| APLL_CONTROL   | 0x0 FFD5 | W   | audio PLL direct control                                 | 0x000 0000 |

| APLL_SELECT    | 0x0 FFD4 | W   | audio PLL direct control select                          | 0x000 0000 |

| SPDIF_STATUS   | 0x0 FFD3 | R   | SPDIF status                                             | 0x000 0000 |

| FSY_INPERIOD   | 0x0 FFD2 | R   | frame sync measured period                               | 0x000 0000 |

| FSY_REFPERIOD  | 0x0 FFD1 | R   | frame sync reference measured period                     | 0x000 0000 |

| FSY_PHASEDIF   | 0x0 FFD0 | R   | frame sync phase difference                              | 0x000 0000 |

| IWAB_BOOTCFG   | 0x0 FFCF | W   | SAA8200HL boot mode configuration                        | 0x000 0000 |

| SRI_STATUS     | 0x0 FFCE | R   | serial radio interface status                            | 0x000 0000 |

| APLL_ACK       | 0x0 FFCD | R   | audio PLL direct control acknowledge                     | 0x000 0000 |

| RSC_STATUS     | 0x0 FFCC | R   | Reed-Solomon status                                      | 0x000 0000 |

| RSC_CONTROL    | 0x0 FFCB | W   | Reed-Solomon control                                     | 0x000 0000 |

| RSC_ADDR       | 0x0 FFCA | W   | Reed-Solomon DMA start address                           | 0x000 0000 |

| RSC_BLKSIZE    | 0x0 FFC9 | W   | Reed-Solomon DMA block size                              | 0x000 0000 |

0x000 0048

Table 10: User register description ... continued

0x0FFC1

### 7.2 VPB0 bridge

MPI\_DEVADDR

Section 7.2 specifies the interfaces and function of the VPB0 bridge. The VPB0 bridge acts as a bridge between a range of RTG IP blocks using the VPB bus and the EPICS7B DIO interface. Two bridges are used one to connect to several slow blocks and an additional one specifically for the UART.

MPI device address

W

The VPB0 bridge forms the bridge between the EPICS7B and the clock generation unit, SRI I<sup>2</sup>C-bus, watchdog timer, event router, I/O configuration and the audio configuration respectively.

# 7.2.1 VPB0 bridge address definitions

Table 11: VPB0 bridge interface description

| Base address | Offset | Key             | Description                                             |

|--------------|--------|-----------------|---------------------------------------------------------|

| 0×0000       |        |                 | clock generation unit                                   |

|              | 0x0000 | SCR_LP0         | switch control register for system PLL clock            |

|              | 0x0004 | SCR_HP0         | switch control register for audio PLL clock             |

|              | 8000x0 | SCR_DCDC        | switch control register for DC-to-DC converter clock    |

|              | 0x000C | SCR_SPDIF       | switch control register for SPDIF clock                 |

|              | 0x0010 | SCR_I2SIN_1     | switch control register for I2SIN_1 bit clock           |

|              | 0x0014 | SCR_I2SIN_2     | switch control register for I2SIN_2 bit clock           |

|              | 0x0018 | SCR_I2SOUT      | switch control register for I2SOUT bit clock            |

|              | 0x001C | SCR_SRI_GCHCLK  | switch control register for SRI gated channel clock     |

|              | 0x0020 | SCR_CR_CLK_OUT1 | switch control register for CR output 1 clock           |

|              | 0x0024 | SCR_CR_CLK_OUT2 | switch control register for CR output 2 clock           |

|              | 0x0028 | SCR_SRI_CHCLK   | switch control register for SRI reference channel clock |

|              | 0x002C | FS1_LP0         | frequency select side 1 for system PLL clock            |

|              | 0x0030 | FS1_ HP0        | frequency select side 1 for audio PLL clock             |

|              | 0x0034 | FS1_DCDC        | frequency select side 1 for DC-to-DC converter clock    |

|              | 0x0038 | FS1_SPDIF       | frequency select side 1 for SPDIF clock                 |

9397 750 13236

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key                   | Description                                               |

|--------------|--------|-----------------------|-----------------------------------------------------------|

|              | 0x003C | FS1_ I2SIN_1          | frequency select side 1 for I2SIN_1 bit clock             |

|              | 0x0040 | FS1_ I2SIN_2          | frequency select side 1 for I2SIN_2 bit clock             |

|              | 0x0044 | FS1_I2SOUT            | frequency select side 1 for I2SOUT bit clock              |

|              | 0x0048 | FS1_ SRI_GCHCLK       | frequency select side 1 for SRI gated channel clock       |

|              | 0x004C | FS1_ CR_CLK_OUT1      | frequency select side 1 for CR output 1 clock             |

|              | 0x0050 | FS1_ CR_CLK_OUT2      | frequency select side 1 for CR output 2 clock             |

|              | 0x0054 | FS1_ SRI_CHCLK        | frequency select side 1 for SRI reference channel clock   |

|              | 0x0058 | FS2_LP0               | frequency select side 2 for system PLL clock              |

|              | 0x005C | FS2_HP0               | frequency select side 2 for audio PLL clock               |

|              | 0x0060 | FS2_DCDC              | frequency select side 2 for DC-to-DC converter clock      |

|              | 0x0064 | FS2_SPDIF             | frequency select side 2 for SPDIF clock                   |

|              | 0x0068 | FS2_ I2SIN_1          | frequency select side 2 for I2SIN_1 bit clock             |

|              | 0x006C | FS2_ I2SIN_2          | frequency select side 2 for I2SIN_2 bit clock             |

|              | 0x0070 | FS2_I2SOUT            | frequency select side 2 for I2SOUT bit clock              |

|              | 0x0074 | FS2_SRI_GCHCLK        | frequency select side 2 for SRI gated channel clock       |

|              | 0x0078 | FS2_CR_CLK_OUT1       | frequency select side 2 for CR output 1 clock             |

|              | 0x007C | FS2_CR_CLK_OUT2       | frequency select side 2 for CR output 2 clock             |

|              | 0x0080 | FS2_SRI_CHCLK         | frequency select side 2 for SRI reference channel clock   |

|              | 0x0084 | SSR_LP0               | frequency select status for system PLL clock              |

|              | 0x0088 | SSR_HP0               | frequency select status for audio PLL clock               |

|              | 0x008C | SSR_DCDC              | frequency select status for DC-to-DC converter clock      |

|              | 0x0090 | SSR_ SPDIF            | frequency select status for SPDIF clock                   |

|              | 0x0094 | SSR_ I2SIN_1          | frequency select status for I2SIN_1 bit clock             |

|              | 0x0098 | SSR_ I2SIN_2          | frequency select status for I2SIN_2 bit clock             |

|              | 0x009C | SSR_ I2SOUT           | frequency select status for I2SOUT bit clock              |

|              | 0x00A0 | SSR_ SRI_GCHCLK       | frequency select status for SRI gated channel clock       |

|              | 0x00A4 | SSR_ CR_CLK_OUT1      | frequency select status for CR output 1 clock             |

|              | 0x00A8 | SSR_ CR_CLK_OUT2      | frequency select status for CR output 2 clock             |

|              | 0x00AC | SSR_ SRI_CHCLK        | frequency select status for SRI reference channel clock   |

|              | 0x00B0 | PCR_SPD_SYSCLK        | power control register for system clock                   |

|              | 0x00B4 | PCR_SYSCLK_DIV4       | power control register for $0.25 \times f_s$ system clock |

|              | 0x00B8 | PCR_UART_UCLK         | power control register for UART clock                     |

|              | 0x00BC | PCR_VPB1_PCLK         | power control register for VPB1 bus clock                 |

|              | 0x00C0 | PCR_UART_PCLK         | power control register for UART bus clock                 |

|              | 0x00C4 | PCR_DEBOUNCE_PCLK     | power control register for DEBOUNCE bus clock             |

|              | 0x00C8 | PCR_CGU_PCLK          | power control register for CGU bus clock                  |

|              | 0x00CC | PCR_WDOG_PCLK         | power control register for WDOG bus clock                 |

|              | 0x00D0 | PCR_ADC_PCLK          | power control register for control ADC bus clock          |

|              | 0x00D4 | PCR_IOCONF_PCLK       | power control register for IO configuration bus clock     |

|              | 0x00D8 | PCR_EVENT_ROUTER_PCLK | power control register for event router bus clock         |

|              | 0x00DC | PCR_SRI_I2C_PCLK      | power control register for SRI I <sup>2</sup> C-bus clock |

# Ensation™ Base integrated wireless audio baseband

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key                    | Description                                                  |

|--------------|--------|------------------------|--------------------------------------------------------------|

|              | 0x00E0 | PCR_ADC_CLK            | power control register for control ADC system clock          |

|              | 0x00E4 | PCR_I2C_MS_PCLK        | power control register for M/S I <sup>2</sup> C-bus clock    |

|              | 0x00E8 | PCR_RSC_PCLK           | power control register for RSC bus clock                     |

|              | 0x00EC | PCR_EXTDMACNTR_PCLK    | power control register for external DMA controller clock     |

|              | 0x00F0 | PCR_DIO2VPB0 _PCLK     | power control register for DIO2VPB0 bus clock                |

|              | 0x00F4 | PCR_DIO2VPB1_PCLK      | power control register for DIO2VPB1 bus clock                |

|              | 0x00F8 | PCR_I2SIN_1 _PCLK      | power control register for I2SIN_1 bus clock                 |

|              | 0x00FC | PCR_I2SIN_2 _PCLK      | power control register for I2SIN_2 bus clock                 |

|              | 0x0100 | PCR_I2SOUT_1 _PCLK     | power control register for I2SOUT_1 bus clock                |

|              | 0x0104 | PCR_I2SOUT_2_PCLK      | power control register for I2SOUT_2 bus clock                |

|              | 0x0108 | PCR_ADSS _PCLK         | power control register for ADSS bus clock                    |

|              | 0x010C | PCR_AUDIO_CONFIG _PCLK | power control register for audio configuration bus clock     |

|              | 0x0110 | PCR_SPDIF _PCLK        | power control register for SPDIF bus clock                   |

|              | 0x0114 | PCR_SRI_PCLK           | power control register for SRI bus clock                     |

|              | 0x0118 | PCR_FRAMESYNCREF       | power control register for SRI frame sync reference          |

|              | 0x011C | PCR_CR_I2SIN_2_BCK     | power control register for I2SIN_2 bit clock                 |

|              | 0x0120 | PCR_CR_I2SIN_1_BCK     | power control register for I2SIN_1 bit clock                 |

|              | 0x0124 | PCR_CR_I2SOUT_BCK      | power control register for I2SOUT bit clock                  |

|              | 0x0128 | PCR_CR_I2SIN_2_WS      | power control register for I2SIN_2 word select               |

|              | 0x012C | PCR_CR_I2SIN_1_WS      | power control register for I2SIN_1 word select               |

|              | 0x030  | PCR_CR_I2SOUT_WS       | power control register for I2SOUT word select                |

|              | 0x0134 | PCR_SDAC_NS_CLK        | power control register for SDAC new sample                   |

|              | 0x0138 | PCR_SDAC_DSPCLK        | power control register for SDAC DSP clock                    |

|              | 0x013C | PCR_SADC_DECCLK        | power control register for SADC decimation filter clock      |

|              | 0x0140 | PCR_SADC_SYSCLK        | power control register for SADC system clock                 |

|              | 0x0144 | PCR_DCDC_CONVERTER_CLK | power control register for DC-to-DC converter clock          |

|              | 0x0148 | PCR_SPDIF_BCK          | power control register for SPDIF bit clock from pad          |

|              | 0x014C | PCR_I2SIN_1_BCK        | power control register for I2SIN_1 bit clock from pad        |

|              | 0x0150 | PCR_I2SIN_2_BCK        | power control register for I2SIN_2 bit clock from pad        |

|              | 0x0154 | PCR_I2SOUT_BCK         | power control register for I2SOUT bit clock from pad         |

|              | 0x0158 | PCR_SRI_GCC_SHO        | power control register for SRI gated channel clock from pace |

|              | 0x015C | PCR_CR_CLK_OUT1        | power control register for crystal output 1 from pad         |

|              | 0x0160 | PCR_CR_CLK_OUT2        | power control register for crystal output 2 from pad         |

|              | 0x0164 | PCR_SRI_CHCLK          | power control register for SRI channel clock                 |

|              | 0x0168 | PSR_SPD_SYSCLK         | power status register for system clock                       |

|              | 0x016C | PSR_SYSCLK_DIV4        | power status register for $0.25 \times f_s$ system clock     |

|              | 0x0170 | PSR_UART_UCLK          | power status register for UART clock                         |

|              | 0x0174 | PSR_VPB1_PCLK          | power status register for VPB1 bus clock                     |

|              | 0x0178 | PSR_UART_PCLK          | power status register for UART bus clock                     |

|              | 0x017C | PSR_DEBOUNCE_PCLK      | power status register for DEBOUNCE bus clock                 |

|              | 0x0180 | PSR_CGU_PCLK           | power status register for CGU bus clock                      |

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key                    | Description                                                    |

|--------------|--------|------------------------|----------------------------------------------------------------|

|              | 0x0184 | PSR_WDOG_PCLK          | power status register for WDOG bus clock                       |

|              | 0x0188 | PSR_ADC_PCLK           | power status register for control ADC bus clock                |

|              | 0x018C | PSR_IOCONF_PCLK        | power status register for IO configuration bus clock           |

|              | 0x0190 | PSR_EVENT_ROUTER_PCLK  | power status register for event router bus clock               |

|              | 0x0194 | PSR_SRI_I2C_PCLK       | power status register for SRI I <sup>2</sup> C-bus clock       |

|              | 0x0198 | PSR_ADC_CLK            | power status register for control ADC system clock             |

|              | 0x019C | PSR_I2C_MS_PCLK        | power status register for M/S I <sup>2</sup> C-bus clock       |

|              | 0x01A0 | PSR_RSC_PCLK           | power status register for RSC bus clock                        |

|              | 0x01A4 | PSR_EXTDMACNTR_PCLK    | power status register for external DMA controller clock        |

|              | 0x01A8 | PSR_DIO2VPB0 _PCLK     | power status register for DIO2VPB0 bus clock                   |

|              | 0x01AC | PSR_DIO2VPB1_PCLK      | power status register for DIO2VPB1 bus clock                   |

|              | 0x01B0 | PSR_I2SIN_1 _PCLK      | power status register for I2SIN_1 bus clock                    |

|              | 0x01B4 | PSR_I2SIN_2 _PCLK      | power status register for I2SIN_2 bus clock                    |

|              | 0x01B8 | PSR_I2SOUT_1 _PCLK     | power status register for I2SOUT_1 bus clock                   |

|              | 0x01BC | PSR_I2SOUT_2_PCLK      | power status register for I2SOUT_2 bus clock                   |

|              | 0x01C0 | PSR_ADSS _PCLK         | power status register for ADSS bus clock                       |

|              | 0x01C4 | PSR_AUDIO_CONFIG _PCLK | power status register for audio configuration bus clock        |

|              | 0x01C8 | PSR_SPDIF _PCLK        | power status register for SPDIF bus clock                      |

|              | 0x01CC | PSR_SRI _PCLK          | power status register for SRI bus clock                        |

|              | 0x01D0 | PSR_FRAMESYNCREF       | power status register for SRI frame sync reference             |

|              | 0x01D4 | PSR_CR_I2SIN_2_BCK     | power status register for I2SIN_2 bit clock                    |

|              | 0x01D8 | PSR_CR_I2SIN_1_BCK     | power status register for I2SIN_1 bit clock                    |

|              | 0x01DC | PSR_CR_I2SOUT_BCK      | power status register for I2SOUT bit clock                     |

|              | 0x01E0 | PSR_CR_I2SIN_2_WS      | power status register for I2SIN_2 word select                  |

|              | 0x01E4 | PSR_CR_I2SIN_1_WS      | power status register for I2SIN_1 word select                  |

|              | 0x01E8 | PSR_CR_I2SOUT_WS       | power status register for I2SOUT word select                   |

|              | 0x01EC | PSR_SDAC_NS_CLK        | power status register for SDAC new sample                      |

|              | 0x01F0 | PSR_SDAC_DSPCLK        | power status register for SDAC DSP clock                       |

|              | 0x01F4 | PSR_SADC_DECCLK        | power status register for SADC decimation filter clock         |

|              | 0x01F8 | PSR_SADC_SYSCLK        | power status register for SADC system clock                    |

|              | 0x01FC | PSR_DCDC_CONVERTER_CLK | power status register for DC-to-DC converter clock             |

|              | 0x0200 | PSR_SPDIF_BCK          | power status register for SPDIF bit clock from pad             |

|              | 0x0204 | PSR_I2SIN_1_BCK        | power status register for I2SIN_1 bit clock from pad           |

|              | 0x0208 | PSR_I2SIN_2_BCK        | power status register for I2SIN_2 bit clock from pad           |

|              | 0x020C | PSR_I2SOUT_BCK         | power status register for I2SOUT bit clock from pad            |

|              | 0x0210 | PSR_SRI_GCC_SHO        | power status register for SRI gated channel clock from part    |

|              | 0x0214 | PSR_CR_CLK_OUT1        | power status register for crystal output 1 from pad            |

|              | 0x0218 | PSR_CR_CLK_OUT2        | power status register for crystal output 2 from pad            |

|              | 0x021C | PSR_SRI_CHCLK          | power status register for SRI channel clock                    |

|              | 0x0220 | ESR_SPD_SYSCLK         | enable fraction divider for system clock                       |

|              | 0x0224 | ESR_SYSCLK_DIV4        | enable fraction divider for 0.25 × f <sub>s</sub> system clock |

Table 11:

VPB0 bridge interface description ...continued

| ase address | Offset | Key                    | Description                                                |

|-------------|--------|------------------------|------------------------------------------------------------|

|             | 0x0228 | ESR_UART_UCLK          | enable fraction divider for UART clock                     |

|             | 0x022C | ESR_VPB1_PCLK          | enable fraction divider for VPB1 bus clock                 |

|             | 0x0230 | ESR_UART_PCLK          | enable fraction divider for UART bus clock                 |

|             | 0x0234 | ESR_DEBOUNCE_PCLK      | enable fraction divider for DEBOUNCE bus clock             |

|             | 0x0238 | ESR_CGU_PCLK           | enable fraction divider for CGU bus clock                  |

|             | 0x023C | ESR_WDOG_PCLK          | enable fraction divider for WDOG bus clock                 |

|             | 0x0240 | ESR_ADC_PCLK           | enable fraction divider for control ADC bus clock          |

|             | 0x0244 | ESR_IOCONF_PCLK        | enable fraction divider for IO configuration bus clock     |

|             | 0x0248 | ESR_EVENT_ROUTER_PCLK  | enable fraction divider for event router bus clock         |

|             | 0x024C | ESR_SRI_I2C_PCLK       | enable fraction divider for SRI I <sup>2</sup> C-bus clock |

|             | 0x0250 | ESR_ADC_CLK            | enable fraction divider for control ADC system clock       |

|             | 0x0254 | ESR_I2C_MS_PCLK        | enable fraction divider for M/S I <sup>2</sup> C-bus clock |

|             | 0x0258 | ESR_RSC_PCLK           | enable fraction divider for RSC bus clock                  |

|             | 0x025C | ESR_EXTDMACNTR_PCLK    | enable fraction divider for external DMA controller clock  |

|             | 0x0260 | ESR_DIO2VPB0 _PCLK     | enable fraction divider for DIO2VPB0 bus clock             |

|             | 0x0264 | ESR_DIO2VPB1_PCLK      | enable fraction divider for DIO2VPB1 bus clock             |

|             | 0x0268 | ESR_I2SIN_1 _PCLK      | enable fraction divider for I2SIN_1 bus clock              |

|             | 0x026C | ESR_I2SIN_2 _PCLK      | enable fraction divider for I2SIN_2 bus clock              |

|             | 0x0270 | ESR_I2SOUT_1 _PCLK     | enable fraction divider for I2SOUT_1 bus clock             |

|             | 0x0274 | ESR_I2SOUT_2_PCLK      | enable fraction divider for I2SOUT_2 bus clock             |

|             | 0x0278 | ESR_ADSS _PCLK         | enable fraction divider for ADSS bus clock                 |

|             | 0x027C | ESR_AUDIO_CONFIG _PCLK | enable fraction divider for audio configuration bus clock  |

|             | 0x0280 | ESR_SPDIF _PCLK        | enable fraction divider for SPDIF bus clock                |

|             | 0x0284 | ESR_SRI _PCLK          | enable fraction divider for SRI bus clock                  |

|             | 0x0288 | ESR_FRAMESYNCREF       | enable fraction divider for SRI frame sync reference       |

|             | 0x028C | ESR_CR_I2SIN_2_BCK     | enable fraction divider for I2SIN_2 bit clock              |

|             | 0x0290 | ESR_CR_I2SIN_1_BCK     | enable fraction divider for I2SIN_1 bit clock              |

|             | 0x0294 | ESR_CR_I2SOUT_BCK      | enable fraction divider for I2SOUT bit clock               |

|             | 0x0298 | ESR_CR_I2SIN_2_WS      | enable fraction divider for I2SIN_2 word select            |

|             | 0x029C | ESR_CR_I2SIN_1_WS      | enable fraction divider for I2SIN_1 word select            |

|             | 0x02A0 | ESR_CR_I2SOUT_WS       | enable fraction divider for I2SOUT word select             |

|             | 0x02A4 | ESR_SDAC_NS_CLK        | enable fraction divider for SDAC new sample                |

|             | 0x02A8 | ESR_SDAC_DSPCLK        | enable fraction divider for SDAC DSP clock                 |

|             | 0x02AC | ESR_SADC_DECCLK        | enable fraction divider for SADC decimation filter clock   |

|             | 0x02B0 | ESR_SADC_SYSCLK        | enable fraction divider for SADC system clock              |

|             | 0x02B4 | ESR_DCDC_CONVERTER_CLK | enable fraction divider for DC-to-DC converter clock       |

|             |        | ESR_SPDIF_BCK          | no fractional divider supported for this clock             |

|             |        | ESR_I2SIN_1_BCK        | no fractional divider supported for this clock             |

|             |        | ESR_I2SIN_2_BCK        | no fractional divider supported for this clock             |

|             |        | ESR_I2SOUT_BCK         | no fractional divider supported for this clock             |

|             |        | ESR_SRI_GCC_SHO        | no fractional divider supported for this clock             |

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key                    | Description                                                   |

|--------------|--------|------------------------|---------------------------------------------------------------|

|              | 0x02B8 | ESR_CR_CLK_OUT1        | enable fraction divider for crystal output 1 from pad         |

|              | 0x02BC | ESR_CR_CLK_OUT2        | enable fraction divider for crystal output 2 from pad         |

|              | 0x02C0 | ESR_SRI_CHCLK          | enable fraction divider for SRI channel clock                 |

|              | 0x02C4 | BCR_LP0                | base control register for system PLL clock                    |

|              | 0x02C8 | BCR_HP0                | base control register for audio PLL clock                     |

|              | 0x2CC  | FDC_SPD_SYSCLK         | fractional divider control for system clock                   |

|              | 0x2D0  | FDC_SYSCLK_DIV4        | fractional divider control for $0.25 \times f_s$ system clock |

|              | 0x02D4 | FDC_UART_UCLK          | fractional divider control for UART clock                     |

|              | 0x02D8 | FDC_DEBOUNCE_PCLK      | fractional divider control for DEBOUNCE bus clock             |

|              | 0x02DC | FDC_ADC_CLK            | fractional divider control for control ADC system clock       |

|              | 0x02E0 | FDC_DIO_PCLK           | fractional divider control for DIO interface clock            |

|              | 0x02E4 | FDC_AUDIO_PCLK         | fractional divider control for audio bus clock                |

|              | 0x02E8 | FDC_FRAMESYNCREF       | fractional divider control for SRI frame sync reference       |

|              | 0x02EC | FDC_CR_I2SIN_2_BCK     | fractional divider control for I2SIN_2 bit clock              |

|              | 0x02F0 | FDC_CR_I2SIN_1_BCK     | fractional divider control for I2SIN_1 bit clock              |

|              | 0x2F4  | FDC_CR_I2SOUT_BCK      | fractional divider control for I2SOUT bit clock               |

|              | 0x02F8 | FDC_I2S_WS             | fractional divider control for I2S word select                |

|              | 0x02FC | FDC_SDAC_NS_CLK        | fractional divider control for SDAC new sample                |

|              | 0x300  | FDC_AUDIO_SYSCLK       | fractional divider control for audio system clock             |

|              | 0x0304 | FDC_DCDC_CONVERTER_CLK | fractional divider control for DC-to-DC converter clock       |

|              | 0x0308 | FDC_CR_CLK_OUT1        | fractional divider control for crystal output 1 from pad      |

|              | 0x030C | FDC_CR_CLK_OUT2        | fractional divider control for crystal output 2 from pad      |

|              | 0x0310 | FDC_SRI_CHCLK          | fractional divider control for SRI channel clock              |

|              | 0x0C00 | CNF_POWERMODE          | power-down CGU                                                |

|              | 0x0C04 | CNF_WD_BARK            | watchdog bark register                                        |

|              | 0x0C08 | reserved               |                                                               |

|              | 0xC0C  | reserved               |                                                               |

|              | 0x0C10 | OSC_ON                 | activate crystal oscillator                                   |

|              | 0x0C14 | OSC_BYPASS             | bypass crystal oscillator                                     |

|              | 0x0C18 | CNF_UART_RST_N         | reset for UART                                                |

|              | 0x0C1C | CNF_I2SIN_1_RST_N      | reset for I2S input 1                                         |

|              | 0x0C20 | CNF_I2SIN_2_RST_N      | reset for I2S input 2                                         |

|              | 0x0C24 | CNF_I2SOUT_1_RST_N     | reset for I2S output 1                                        |

|              | 0x0C28 | CNF_I2SOUT_2_RST_N     | reset for I2S output 2                                        |

|              | 0x0C2C | CNF_DEC_RST_N          | reset for decimation filter                                   |

|              | 0x0C30 | CNF_INT_RST_N          | reset for interpolation filter                                |

|              | 0x0C34 | CNF_SPDIF_RST_N        | reset for SPDIF                                               |

|              | 0xC38  | CNF_EPICS7B_RST_N      | reset for EPICS7B                                             |

|              | 0x0C3C | CNF_DIO2VPB0_RST_N     | reset for VPB0 bridge                                         |

|              | 0x0C40 | CNF_DIO2VPB1_RST_N     | reset for UART VPB bridge                                     |

|              |        |                        |                                                               |

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key                | Description                               |

|--------------|--------|--------------------|-------------------------------------------|

|              | 0x0C48 | CNF_SRI _RST_N     | reset for serial radio interface          |

|              | 0x0C4C | CNF_RSC_RST_N      | reset for Reed-Solomon codec              |

|              | 0x0C50 | CNF_SRI_I2C_RST_N  | reset for SRI I <sup>2</sup> C-bus        |

|              | 0x0C54 | CNF_ad10bit_RST_N  | reset for control ADC                     |

|              | 0x0C58 | CNF_FSL_RST_N      | reset for frame sync lock                 |

|              | 0x0C5C | CNF_GCC_RST_N      | reset for gated channel clock             |

|              | 0x0C60 | CNF_ad10bit_PRST_N | preset for control ADC                    |

|              | 0x0C64 | HP0_FIN_SELECT     | audio clock PLL input select              |

|              | 0x0C68 | HP0_MDEC           | audio clock PLL M divider                 |

|              | 0x0C6C | HP0_NDEC           | audio clock PLL N divider                 |

|              | 0x0C70 | HP0_PDEC           | audio clock PLL P divider                 |

|              | 0x0C74 | HP0_MODE           | audio clock PLL mode                      |

|              | 0x0C78 | HP0_STATUS         | audio clock PLL status                    |

|              | 0x0C7C | HP0_ACK            | audio clock PLL acknowledge               |

|              | 0x0C80 | HP0_REQ            | audio clock PLL change request            |

|              | 0x0C84 | HP0_INSELR         | audio clock PLL input bandwidth selection |

|              | 0x0C88 | HP0_INSELI         | audio clock PLL input bandwidth selection |

|              | 0x0C8C | HP0_INSELP         | audio clock PLL input bandwidth selection |

|              | 0x0C90 | HP0_SELR           | audio clock PLL input bandwidth selection |

|              | 0x0C94 | HP0_SELI           | audio clock PLL input bandwidth selection |

|              | 0x0C98 | HP0_SELP           | audio clock PLL input bandwidth selection |

|              | 0x0C9C | LP0_FIN_SELECT     | system clock PLL input select             |

|              | 0x0CA0 | LP0_PWD            | system clock PLL power-down               |

|              | 0x0CA4 | LP0_BYPASS         | system clock PLL bypass                   |

|              | 0x0CA8 | LP0_LOCK           | system clock PLL in-lock                  |

|              | 0x0CAC | LP0_DIRECT         | system clock PLL direct CCO control       |

|              | 0x0CB0 | LP0_MSEL           | system clock PLL M divider                |

|              | 0x0CB4 | LP0_PSEL           | system clock PLL P divider                |

| x1000        |        |                    | SRI I <sup>2</sup> C-bus                  |

|              | 0x0000 | RX                 | receive FIFO                              |

|              | 0x0000 | TX                 | transmit FIFO                             |

|              | 0x0004 | STS                | status register                           |

|              | 0x0008 | CTL                | control register                          |

|              | 0x000C | CLKHI              | clock divisor high                        |

|              | 0x0010 | CLKLO              | clock divisor low                         |

|              | 0x0014 | ADDR               | I <sup>2</sup> C-bus address              |

|              | 0x0028 | TXS                | slave transmit FIFO                       |

| 0x2000       |        |                    | control ADC                               |

|              | 0x0000 | ADC_R0             | ADC data channel 0                        |

|              | 0x0004 | ADC_R1             | ADC data channel 1                        |

|              | 0x0008 | ADC_R2             | ADC data channel 2                        |

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key            | Description                               |

|--------------|--------|----------------|-------------------------------------------|

|              | 0x000C | ADC_R3         | ADC data channel 3                        |

|              | 0x0010 | ADC_R4         | ADC data channel 4                        |

|              | 0x0014 | ADC_R5         | ADC data channel 5                        |

|              | 0x0018 | ADC_R6         | ADC data channel 6                        |

|              | 0x001C | ADC_R7         | ADC data channel 7                        |

|              | 0x0020 | ADC_CON        | control register                          |

|              | 0x0024 | ADC_CSEL_RES   | channel and resolution selection register |

|              | 0x0028 | ADC_INT_ENABLE | interrupt enable register                 |

|              | 0x002C | ADC_INT_STATUS | interrupt status register                 |

|              | 0x0030 | ADC_INT_CLEAR  | interrupt clear register                  |

| 0x3000       |        |                | watchdog timer                            |

|              | 0x0000 | IR             | interrupt register                        |

|              | 0x0004 | TCR_REG        | timer control register                    |

|              | 0x0008 | TC             | timer counter                             |

|              | 0x000C | PR_REG         | pre-scale register                        |

|              | 0x0010 | PC             | pre-scale counter                         |

|              | 0x0014 | MCR            | match control register                    |

|              | 0x0018 | MR0            | match register 0                          |

|              | 0x001C | MR1            | match register 1                          |

|              | 0x003C | EMR            | external match register                   |

| 0x4000       |        |                | event router                              |

|              | 0x0804 | DTR_GP_13_irq  | de-bounce time register for GP_13_irq     |

|              | 0x0808 | DTR_GP_12_irq  | de-bounce time register for GP_12_irq     |

|              | 0x080C | DTR_GP_11_irq  | de-bounce time register for GP_11_irq     |

|              | 0x0810 | DTR_GP_10_irq  | de-bounce time register for GP_10_irq     |

|              | 0x0814 | DTR_GP_9_irq   | de-bounce time register for GP_9_irq      |

|              | 0x0818 | DTR_GP_8_irq   | de-bounce time register for GP_8_irq      |

|              | 0x081C | DTR_GP_7_irq   | de-bounce time register for GP_7_irq      |

|              | 0x0820 | DTR_GP_6_irq   | de-bounce time register for GP_6_irq      |

|              | 0x0824 | DTR_GP_5_irq   | de-bounce time register for GP_5_irq      |

|              | 0x0828 | DTR_GP_4_irq   | de-bounce time register for GP_4_irq      |

|              | 0x082C | DTR_GP_3_irq   | de-bounce time register for GP_3_irq      |

|              | 0x0830 | DTR_GP_2_irq   | de-bounce time register for GP_2_irq      |

|              | 0x0834 | DTR_GP_1_irq   | de-bounce time register for GP_1_irq      |

|              | 0x0838 | DTR_GP_0_irq   | de-bounce time register for GP_0_irq      |

|              | 0x0C00 | PEND           | input event pending status                |

|              | 0x0C20 | INT_CLR        | interrupt clear                           |

|              | 0x0C40 | INT_SET        | interrupt set                             |

| 0x6000       |        |                | input/output configuration                |

|              | 0x0000 | IOC_PINS       | read pin values                           |

|              | 0x0010 | IOC_MODE0      | load mode 0                               |

|              |        |                |                                           |

Table 11:

VPB0 bridge interface description ...continued

| Base address | Offset | Key                 | Description                                      |

|--------------|--------|---------------------|--------------------------------------------------|

|              | 0x0014 | IOC_MODE0_SET       | set mode 0                                       |

|              | 0x0018 | IOC_MODE0_RESET     | reset mode 0                                     |

|              | 0x0020 | IOC_MODE1           | load mode 1                                      |

|              | 0x0024 | IOC_MODE1_SET       | set mode 1                                       |

|              | 0x0028 | IOC_MODE1_RESET     | reset mode 1                                     |

| 0x7000       |        |                     | audio configuration                              |

|              | 0x0000 | I2S_FORMAT_SETTINGS | I <sup>2</sup> S-bus format settings             |

|              | 0x0004 | I2S_MUX_SETTINGS    | I <sup>2</sup> S-bus multiplexer settings        |

|              | 8000x0 | SPDIF_STATUS        | SPDIF status                                     |

|              | 0x000C | SPDIF_IRQ_EN        | SPDIF interrupt enable                           |

|              | 0x0010 | SPDIF_IRQ_STATUS    | SPDIF interrupt status                           |

|              | 0x0014 | SPDIF_IRQ_CLEAR     | SPDIF interrupt clear                            |

|              | 0x0018 | SDAC_CTRL_INTI      | audio DAC input interpolation filter control     |

|              | 0x001C | SDAC_CTRL_INTO      | audio DAC output interpolation filter control    |

|              | 0x0020 | SDAC_SETTINGS       | audio DAC control                                |

|              | 0x0024 | SADC_CTRL_SDC       | audio ADC amplifiers control                     |

|              | 0x0028 | SADC_CTRL_ADC       | audio ADC control                                |

|              | 0x002C | SADC_CTRL_DECI      | audio ADC input decimation filter control        |

|              | 0x0030 | SADC_CTRL_DECO      | audio ADC output decimation filter control       |

|              | 0x0034 | E7B_IRQ             | EPICS7B interrupt request                        |

|              | 0x0038 | PD_ADC10B           | power-down control ADC                           |

|              | 0x003C | SET_DCDC1V8_ADJUST  | DC-to-DC converter adjust output voltage (1.8 V) |

|              | 0x0040 | SET_DCDC3V3_ADJUST  | DC-to-DC converter adjust output voltage (3.3 V) |

|              |        |                     |                                                  |

# 7.3 Clock generation unit

The Clock Generation Unit (CGU) generates all clock signals required for the SAA8200HL, it contains:

- A crystal oscillator

- For low power mode the internal DC-to-DC converter clock can be used as system clock

- An audio PLL to generate audio sample frequencies

- A system PLL to generate the clocks for the VPB bus and the DSP subsystem

- A clock switch block

- A configuration register block

- A reset and power block.

An 11.2896 MHz oscillator or an external 11.025 MHz clock (provided by the TEA7000) can be used in combination with the two PLLs and the external clocks to generate the system frequencies.

All PLLs are programmed with the registers in the register configuration block.

# **Ensation™ Base integrated wireless audio baseband**

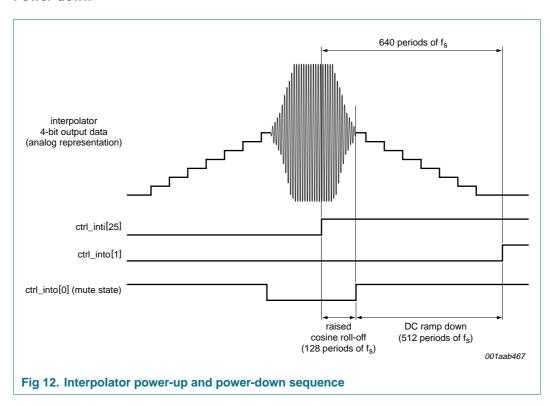

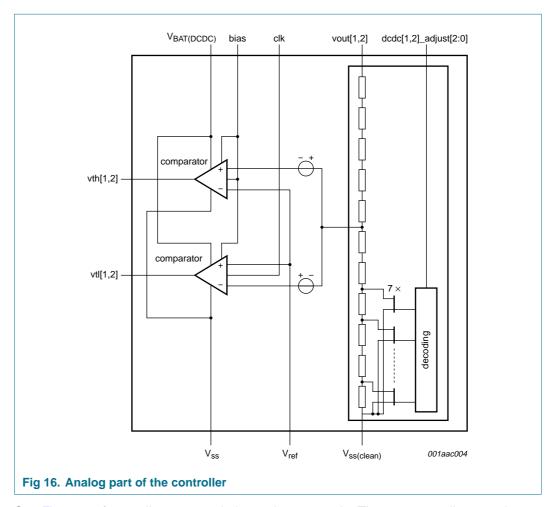

## 7.3.1 Crystal oscillator