### **Product Version: V1**

#### **Key Features**

- High-end security controller

- Common Criteria Certified EAL6+ (high) hardware

- Turnkey solution

- Compliant with the USB Type-C<sup>™</sup> Authentication standard

- Up to 10kB user memory

- PG-USON-10-2,-4 package (3 x 3 mm)

- Standard & Extended temperature ranges

- 12C interface with Shielded Connection (encrypted communication)

- Cryptographic support: ECC NIST P256/P384, SHA-256, TRNG, DRNG

- Crypto ToolBox commands for SHA-256, ECC NIST P256/P384 (sign, verify and key generation)

- **Device Security Monitor**

- 4 Monotonic up counters

- Protected (integrity) update of data objects

- Hibernate for zero power consumption<sup>1</sup>

- Lifetime for Industrial Automation and Infrastructure is 20 years and 15 years for other Application Profiles

- Wireless Power Consortium(WPC) Authentication

#### **Benefits**

- Protection of data

- Protection of business case

- Protection of corporate image

- Safeguarding of quality and safety

#### **Applications**

- Consumer electronics

- **Smart Home**

- **Drones**

#### **About this document**

### **Scope and purpose**

This Datasheet provides information to enable integration of a security device, and includes package, connectivity and technical data.

<sup>&</sup>lt;sup>1</sup> Leakage current < 2.5μA only

### **Product Version: V1**

### **Table of Contents**

### **Intended audience**

# **Table of Contents**

| Abou   | ıt this document                                                       | 1  |

|--------|------------------------------------------------------------------------|----|

| Table  | e of Contents                                                          | 2  |

| 1      | Introduction                                                           | 4  |

| 1.1    | Broad range of benefits                                                |    |

| 1.2    | Enhanced security                                                      | ∠  |

| 1.3    | Fast and easy integration                                              | 2  |

| 1.4    | Applications                                                           |    |

| 1.5    | Device Features                                                        | 2  |

| 2      | System Block Diagram                                                   | 6  |

| 3      | Interface and Schematics                                               | 8  |

| 3.1    | System Integration Schematics                                          | 8  |

| 3.2    | System Integration Schematics with Hibernation support                 | 8  |

| 4      | Description of packages                                                | 9  |

| 4.1    | PG-USON-10-2,-4                                                        | 9  |

| 4.2    | Production sample marking pattern                                      | 10 |

| 5      | Technical Data                                                         | 12 |

| 5.1    | I2C Interface Characteristics                                          | 12 |

| 5.1.1  | I2C Standard/Fast Mode Interface Characteristics                       | 12 |

| 5.1.2  | I2C Fast Mode Plus Interface Characteristics                           | 13 |

| 5.1.3  | Electrical Characteristics                                             | 14 |

| 5.1.3. | .1 DC Electrical Characteristics                                       | 14 |

| 5.1.3. |                                                                        |    |

| 5.1.4  | <b></b>                                                                |    |

| 5.1.4. | ı                                                                      |    |

| 5.1.4. | '                                                                      |    |

| 6      | Connecting to Host                                                     |    |

| 5.1    | OPTIGA™ Trust Charge Host Software Architecture                        |    |

| 6.2    | Release Package Folder Structure                                       |    |

| 6.3    | Porting Notes                                                          |    |

| 6.4    | Communication with OPTIGA™ Trust Charge                                |    |

| 6.5    | Reference code for communicating with OPTIGA™ Trust Charge             |    |

| 7      | OPTIGA™ Trust Charge External Interface                                |    |

| 7.1    | Commands                                                               |    |

| 7.2    | Crypto Performance                                                     |    |

| 8      | Security Monitor                                                       |    |

| 3.1    | Security Events                                                        |    |

| 3.2    | Security Monitor Policy                                                |    |

| 9      | RoHS Compliance                                                        | 28 |

| 10     | Appendix A – Infineon I2C Protocol Registry Map                        | 29 |

| 10.1   | Infineon I2C Protocol Variations                                       | 31 |

| 11     | Appendix B - OPTIGA™ Trust Charge Command/Response I2C Sample Logs     |    |

| 11.1   | Sequence of commands to read Coprocessor UID from OPTIGA™ Trust Charge | 33 |

| 11.1.  | 1 Check the status [I2C_STATE]                                         | 33 |

**(infineon**

# **Product Version: V1**

# **Table of Contents**

| 11.1.2   | Issue OpenApplication command | 33 |

|----------|-------------------------------|----|

| 11.1.3   | Read Coprocessor UID          |    |

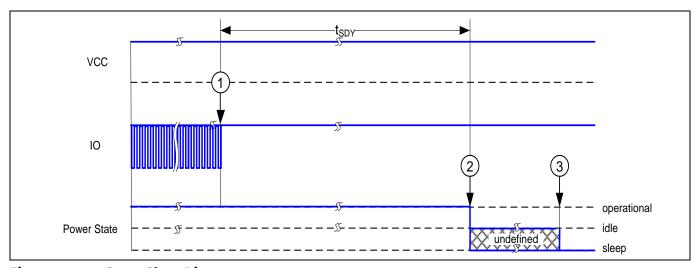

| 12 Ap    | pendix C – Power Management   | 35 |

| _        | Hibernation                   |    |

| 12.2     | Low Power Sleep Mode          | 35 |

| Revision | history                       | 36 |

### 1 Introduction

As embedded systems (e.g. IoT devices) are increasingly gaining the attention of attackers, Infineon offers the OPTIGA™ Trust Charge as an authentication solution for wireless power charging applications. This high-end security controller comes with full system integration support for easy and cost-effective deployment of high-end security for your assets.

# 1.1 Broad range of benefits

Integrated into your device, the OPTIGA™ Trust Charge supports protection of your brand and business case, differentiates your product from your competitors, and adds value to your product, making it stronger against cyberattacks.

# 1.2 Enhanced security

The OPTIGA™ Trust Charge is based on an advanced security controller with built-in tamper proof NVM for secure storage and Symmetric/Asymmetric crypto engines to support ECC 256/384 and SHA-256. This new security technology greatly enhances your overall system security.

# 1.3 Fast and easy integration

The turnkey setup – with full system integration and all key/certificate material preprogrammed – reduces your efforts for design, integration and deployment to a minimum. As a turnkey solution, the OPTIGA™ Trust Charge comes with preprogrammed OS/Application code locked and with host-side modules to integrate with host micro controller software. The temperature range of −40°C to +105°C combined with a standardized I2C interface and the small PG-USON-10-2,-4 footprints will facilitate onboarding in your existing ecosystem. Almost 30 years in a market-leading position with nearly 20 billion security controllers shipped worldwide are the results of Infineon's strong expertise and its commitment to make security a success factor for you.

# 1.4 Applications

The OPTIGA™ Trust Charge covers a broad range of use cases necessary for many types of applications that include the following:

- a) Protect the Authenticity, Integrity and Confidentiality of your product and data

- b) Datastore Protection

- c) Lifecycle Management

#### 1.5 Device Features

The OPTIGA™ Trust Charge comes with up to 10 kB user memories that can be used to store WPC certificates and data. OPTIGA™ Trust Charge is based on Common Criteria (CC) Certified EAL6+ (high) hardware enabling it to prevent physical attacks on the device itself and providing high assurance that the keys or arbitrary data stored cannot be accessed by an unauthorized entity. The CC certificate can be found at <a href="www.bsi.bund.de">www.bsi.bund.de</a> by searching for BSI-DSZ-CC-0961(Hardware Identifier IFX\_CCI\_00000Bh) and referring to the latest CC certificate. OPTIGA™ Trust Charge supports a highspeed I2C communication interface of up to 1MHz (FM+).

#### Table 1 Products

# Introduction

| Туре                                      | Description                                                                                                            | Temperature range                                   | Package         |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|

| OPTIGA™ Trust<br>Charge<br>SLS 32AIA020U2 | Embedded security solution for connected devices                                                                       | −25°C to +85°C Standard<br>Temperature Range (STR)  | PG-USON-10-2,-4 |

| OPTIGA™ Trust<br>Charge<br>SLS 32AIA020U3 | Embedded security solution for connected devices                                                                       | -40°C to +105°C Extended<br>Temperature Range (ETR) | PG-USON-10-2,-4 |

| Evaluation Kit                            | Provides all the components required to set up the environment to demonstrate the features of the OPTIGA™ Trust Charge |                                                     | Board           |

Infineon and its distribution partners offer a wide range of customization options (e.g. WPC certificate generation and key provisioning) for the security chip.

Table 2 **Abbreviations**

| Abbreviation | Definition                                     |

|--------------|------------------------------------------------|

| AES          | Advanced Encryption Standard                   |

| API          | Application Programming Interface              |

| CA           | Certification Authority                        |

| CC           | Common Criteria                                |

| DRNG         | Deterministic Random Number Generator          |

| EAL          | Evaluation Assurance Level                     |

| ECC          | Elliptic Curve Cryptography                    |

| ECDSA        | Elliptic Curve Digital Signature Algorithm     |

| I2C          | Inter-Integrated Circuit                       |

| IETF         | Internet Engineering Task Force                |

| IFX          | Infineon                                       |

| IOT          | Internet of Things                             |

| IP           | Intellectual Property                          |

| NIST         | National Institute of Standards and Technology |

| OS           | Operating System                               |

| PAL          | Platform Abstraction Layer                     |

| PKI          | Public Key Infrastructure                      |

| RFC          | Request For Comments                           |

| SHA          | Secure Hash Algorithm                          |

| SKU          | Stock Keeping Unit                             |

| STR          | Standard Temperature Range                     |

| TRNG         | True Random Number Generator                   |

| USB          | Universal Synchronous Bus                      |

| WPC          | Wireless Power Consortium                      |

# **System Block Diagram**

# 2 System Block Diagram

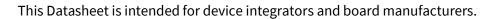

The following figure depicts the system block diagram for OPTIGA™ Trust Charge.

Figure 1 System Block Diagram

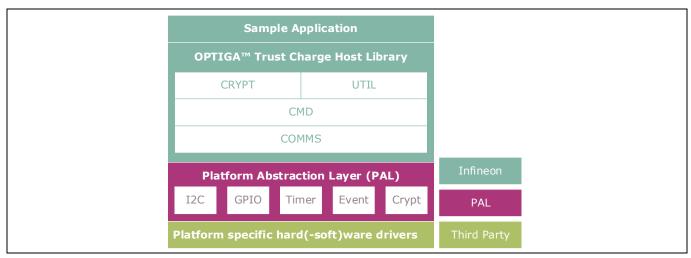

The System Block Diagram is explained below for each layer.

#### 1. Local Host

- Local Host Application This is the target application which utilizes OPTIGA™ Trust Charge for its security needs

- OPTIGA™ Trust Charge Host Library

- CRYPT Provides APIs to perform cryptographic functionalities.

- UTIL Provides APIs such as read/write, protected update of data objects and open/close application (e.g. Hibernate)

- CMD Provides APIs to send and receive commands (Section 7) to and from OPTIGA™

Trust Charge

- COMMS Provides wrapper APIs for communication (optional encrypted communication using Shielded Connection) with OPTIGA™ Trust Charge which internally uses Infineon I2C Protocol (IFX I2C)

- PAL A layer that abstracts platform specific drivers (e.g. I2C, Timer, GPIO, platform crypto library etc.)

#### 2. OPTIGA™ Trust Charge

- O Arbitrary Data Objects The target application can store up to 4.5kB (~4600 bytes) of data into OPTIGA™ Trust Charge. The data could be additional Trust Anchors, certificates and shared secret.

- Monotonic Counters Provides 4 monotonic counting data objects (up counters). These can be used as general purpose counter or as linked counter to other objects.

- For more information, please refer to Solution Reference Manual document available as part of the package.

- o WPC Certificates Up to 4 WPC Certificate chains can be stored

- o Keys Up to 4 ECC based keys can be stored

# **System Block Diagram**

- Trust Anchors 3 slots

- Crypto Functions OPTIGA<sup>™</sup> Trust Charge provides cryptographic functions that can be invoked via local host

Note:

Unique ECC private keys and WPC Certificates – During production at Infineon fab, unique asymmetric keys (private and public) are generated. The public key is signed by customer specific CA and the resulting WPC certificate issued is securely stored in the OPTIGA™ Trust Charge. Special measures are taken to prevent the leakage and modification of private key material at the Common Criteria Certified production site

#### **Interface and Schematics**

### 3 Interface and Schematics

This section explains the schematics of the product and gives some recommendations as to how the controller should be externally connected.

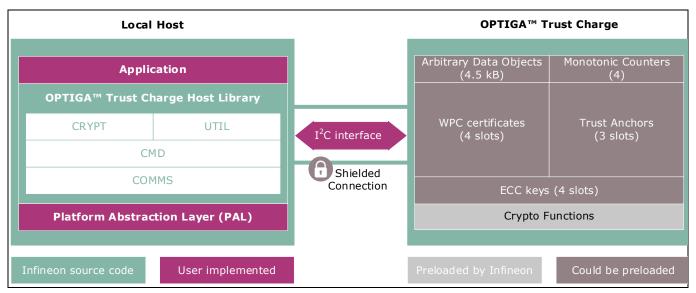

# 3.1 System Integration Schematics

The following figure illustrates how to integrate OPTIGA™ Trust Charge with your local host.

Figure 2 System Integration Schematic Diagram

Note: Value of the pullup resistors depend on the target application circuit and the targeted I2C

frequency.

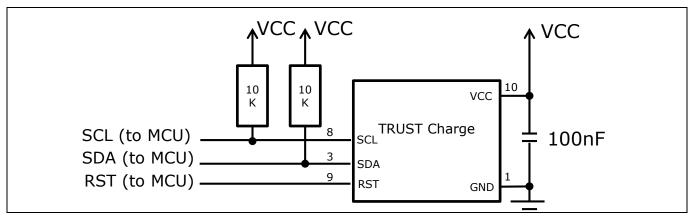

# 3.2 System Integration Schematics with Hibernation support

The following figure illustrates how to integrate OPTIGA™ Trust Charge with hibernation, with your local host.

Figure 3 System Integration Schematic Diagram with Hibernation

Note: Value of the pullup resistors depend on the target application circuit and the targeted I2C

frequency.

# **Description of packages**

# 4 Description of packages

This chapter provides information on the package types and how the interfaces of each product are assigned to the package pins. For further information on compliance of the packages with European Parliament Directives, see "RoHS Compliance" on Page 28.

For details and recommendations regarding the assembly of packages on PCBs, please see the following: <a href="http://www.infineon.com/cms/en/product/technology/packages/">http://www.infineon.com/cms/en/product/technology/packages/</a>

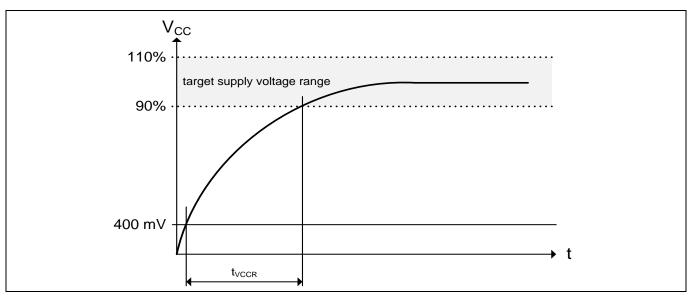

### 4.1 PG-USON-10-2,-4

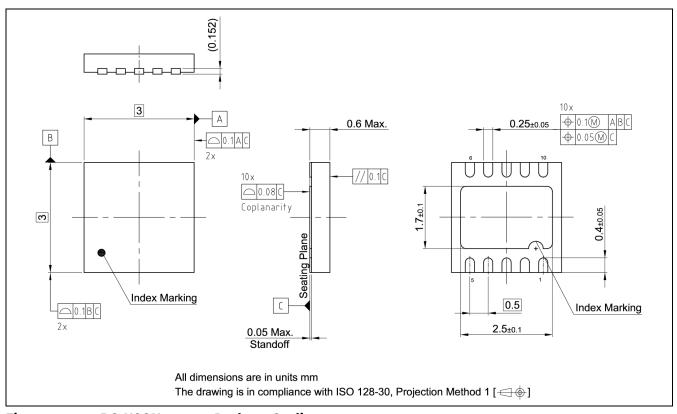

The package dimensions (in mm) of the controller in PG-USON-10-2,-4 packages are given below.

Figure 4 PG-USON-10-2,-4 Package Outline

The following figure shows the PG-USON-10-2,-4 in top view:

# **Description of packages**

Figure 5 PG-USON-10-2,-4 top view

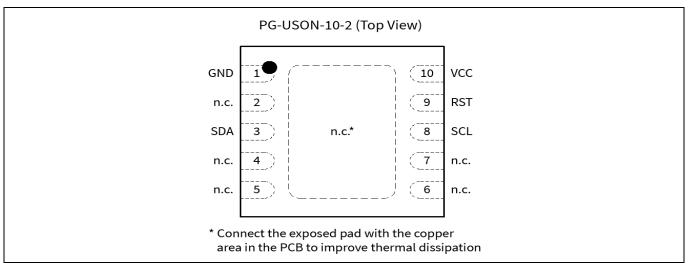

# 4.2 Production sample marking pattern

The following figure describes the productive sample marking pattern on PG-USON-10-2,-4.

Figure 6 PG-USON-10-2,-4 sample marking pattern

The black dot indicates pin 01 for the chip. The following Table 3 describes the sample marking pattern:

Table 3 Marking table for PG-USON-10-2,-4 packages

| Indicator | Description                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LOT CODE  | Defined and inserted during fabrication                                                                                                                                                                                                                             |  |  |  |  |  |

| ZZ        | Indicates the Certifying Authority Serial Number / SKU#, e.g. "00" would mean "SKU#00"                                                                                                                                                                              |  |  |  |  |  |

| H/E       | H = "Halogen-free", E = "Engineering samples" This indicator is followed by "YYWW", where YY is the "Year" and WW is the "Work Week" of the production. This is inserted during fabrication. Engineering samples have "E YYWW" and productive samples have "H YYWW" |  |  |  |  |  |

# **Description of packages**

| Indicator | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12345     | Convention: T&#\$@</td></tr><tr><td></td><td>where:</td></tr><tr><td></td><td>The letter "T" indicates the OPTIGA Trust family</td></tr><tr><td></td><td>& indicates the product is a Trust Charge controller</td></tr><tr><td></td><td>• # indicates the controller is a STR (S) variant</td></tr><tr><td></td><td>• \$ specifies the OPTIGA™ Trust Charge release version number</td></tr><tr><td></td><td>@ specifies the software version</td></tr><tr><td></td><td>Example: "TCS10" means 'OPTIGA™ Trust Charge', 'STR variant', 'release version 1', 'software version 0'</td></tr></tbody></table> |

The contacts and their functionality are given in the Table 4 below.

Table 4 Contact definitions and functions of PG-USON-10-2,-4 packages

| Pin | Туре | Function                                  |

|-----|------|-------------------------------------------|

| 01  | GND  | Supply voltage (Ground)                   |

| 02  | NC   | Not connected / Do not connect externally |

| 03  | I/O  | Serial Data Line (SDA)                    |

| 04  | NC   | Not connected / Do not connect externally |

| 05  | NC   | Not connected / Do not connect externally |

| 06  | NC   | Not connected / Do not connect externally |

| 07  | NC   | Not connected / Do not connect externally |

| 08  | I/O  | Serial Clock Line (SCL)                   |

| 09  | IN   | Active Low Reset (RST)                    |

| 10  | PWR  | Supply voltage (V <sub>cc</sub> )         |

### **Technical Data**

#### **Technical Data** 5

This section summarizes the technical data of the product. It provides the operational characteristics as well as the electrical DC and AC characteristics.

#### **12C Interface Characteristics** 5.1

Table 5 **I2C Operation Supply and Input Voltages**

| Parameter                 | Symbol               | Values |      |                                               |   | Note or Test                                           |

|---------------------------|----------------------|--------|------|-----------------------------------------------|---|--------------------------------------------------------|

|                           |                      | Min.   | Тур. | Max.                                          |   | Condition                                              |

| Supply voltage            | $V_{\text{CC\_I2C}}$ | 1.62   | -    | 5.5                                           | V |                                                        |

| SDA, SCL input<br>voltage | V <sub>IN_I2C</sub>  | -0.3   | -    | V <sub>CC_I2C</sub> + 0.5 or 5.5 <sup>1</sup> | V | V <sub>CC_I2C</sub> is in the operational supply range |

|                           |                      | -0.3   | -    | 5.5                                           | V | V <sub>CC_I2C</sub> is switched off                    |

<sup>1)</sup> Whichever is lower

#### **I2C Standard/Fast Mode Interface Characteristics** 5.1.1

For operation of the I2C interface, the electrical characteristics are compliant with the I2C bus specification Rev. 4 for "standard-mode" (f<sub>SCL</sub> up to 100 kHz) and "fast-mode" (f<sub>SCL</sub> up to 400 kHz), with certain deviations as stated in the table below.

Note:

$T_A$  as given for the operating temperature range of the controller unless otherwise stated.

Table 6 **I2C Standard Mode Interface Characteristics**

| Parameter                                                                      | Symbol           |      | Valı | Values                    |     | Note or Test Condition                                                                                             |

|--------------------------------------------------------------------------------|------------------|------|------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------|

|                                                                                |                  | Min. | Тур. | Max.                      |     |                                                                                                                    |

| SCL clock frequency                                                            | f <sub>SCL</sub> | 0    | -    | 100                       | kHz |                                                                                                                    |

| Input low-level                                                                | V <sub>IL</sub>  | -0.3 | _    | 0.3 * V <sub>CC_I2C</sub> | V   |                                                                                                                    |

| Low-level output<br>voltage                                                    | V <sub>OL1</sub> | 0    | -    | 0.4                       | V   | Sink current 3 mA;<br>$V_{CC_{12}C} \ge 2.7 \text{ V}$<br>Sink current 2 mA;<br>$V_{CC_{12}C} < 2.7 \text{ V}$     |

| Low-level output current                                                       | I <sub>OL</sub>  | 3 2  | -    | -                         | mA  | $V_{OL} = 0.4 \text{ V}; V_{CC\_12C} \ge 2.7 \text{ V}$<br>$V_{OL} = 0.4 \text{ V}; V_{CC\_12C} \le 2.7 \text{ V}$ |

| Output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub> (at device pin) | t <sub>OF</sub>  | -    | -    | 250                       | ns  | $C_b \le 400 \text{ pF}; V_{CC\_I2C} \ge 2.7 \text{ V}$<br>$C_b \le 200 \text{ pF}; V_{CC\_I2C} \le 2.7 \text{ V}$ |

| Capacitive load for each bus line                                              | Сь               | -    | -    | 400<br>200                | pF  | $V_{CC_{12C}} \ge 2.7 \text{ V}$<br>$V_{CC_{12C}} < 2.7 \text{ V}$                                                 |

### **Technical Data**

**Table 7 I2C Fast Mode Interface Characteristics**

| Parameter                                                                      | Symbol           | Values                                              |      |                           | Unit | Note or Test Condition                                                                                             |

|--------------------------------------------------------------------------------|------------------|-----------------------------------------------------|------|---------------------------|------|--------------------------------------------------------------------------------------------------------------------|

|                                                                                |                  | Min.                                                | Тур. | Max.                      |      |                                                                                                                    |

| SCL clock frequency                                                            | f <sub>SCL</sub> | 0                                                   | -    | 400                       | kHz  |                                                                                                                    |

| Input low-level                                                                | V <sub>IL</sub>  | -0.3                                                | -    | 0.3 * V <sub>CC_I2C</sub> | V    |                                                                                                                    |

| Low-level output<br>voltage                                                    | V <sub>OL1</sub> | 0                                                   | -    | 0.4                       | V    | Sink current 3 mA;<br>$V_{CC_{12}C} \ge 2.7 \text{ V}$<br>Sink current 2 mA;<br>$V_{CC_{12}C} < 2.7 \text{ V}$     |

| Low-level output current                                                       | I <sub>OL</sub>  | 3 2                                                 | -    | -                         | mA   | $V_{OL} = 0.4 \text{ V}; V_{CC\_I2C} \ge 2.7 \text{ V}$<br>$V_{OL} = 0.4 \text{ V}; V_{CC\_I2C} < 2.7 \text{ V}$   |

| Output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub> (at device pin) | t <sub>of</sub>  | 20 *<br>V <sub>CC_I2C</sub> /<br>5.5 V <sup>1</sup> | -    | 250                       | ns   | $C_b \le 400 \text{ pF}; V_{CC\_12C} \ge 2.7 \text{ V}$<br>$C_b \le 200 \text{ pF}; V_{CC\_12C} \le 2.7 \text{ V}$ |

| Capacitive load for each bus line                                              | Сь               | 15 <sup>2</sup>                                     | -    | 400<br>200                | pF   | $V_{CC\_12C} \ge 2.7 \text{ V}$<br>$V_{CC\_12C} < 2.7 \text{ V}$                                                   |

<sup>1)</sup> A min. capacitive load is necessary to reach top

# **5.1.2** I2C Fast Mode Plus Interface Characteristics

For operation of the I2C interface, the electrical characteristics are compliant with the I<sup>2</sup>C bus specification Rev. 4 for "fast mode plus" ( $f_{SCL}$  up to 1 MHz), with certain deviations as stated in the table below.

Note:  $T_A$  as given for the operating temperature range of the controller unless otherwise stated.

**Table 8** I2C Fast Mode Plus Interface Characteristics

| Parameter                                                                      | Symbol           | Values                                              |      |                           | Unit | Note or Test Condition                                                                                           |

|--------------------------------------------------------------------------------|------------------|-----------------------------------------------------|------|---------------------------|------|------------------------------------------------------------------------------------------------------------------|

|                                                                                |                  | Min.                                                | Тур. | Max.                      |      |                                                                                                                  |

| SCL clock frequency                                                            | f <sub>SCL</sub> | 0                                                   | _    | 1000                      | kHz  |                                                                                                                  |

| Input low-level                                                                | V <sub>IL</sub>  | -0.3                                                | _    | 0.3 * V <sub>CC_I2C</sub> | ٧    |                                                                                                                  |

| Low-level output<br>voltage                                                    | V <sub>OL1</sub> | 0                                                   | -    | 0.4                       | V    | Sink current 3 mA;<br>$V_{CC\_12C} \ge 2.7 \text{ V}$<br>Sink current 2 mA;<br>$V_{CC\_12C} < 2.7 \text{ V}$     |

| Low-level output current                                                       | I <sub>OL</sub>  | 3 2                                                 | -    | -                         | mA   | $V_{OL} = 0.4 \text{ V}; V_{CC\_I2C} \ge 2.7 \text{ V}$<br>$V_{OL} = 0.4 \text{ V}; V_{CC\_I2C} < 2.7 \text{ V}$ |

| Output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub> (at device pin) | t <sub>OF</sub>  | 20 *<br>V <sub>CC_I2C</sub> /<br>5.5 V <sup>1</sup> | -    | 120                       | ns   | C <sub>b</sub> ≤ 150 pF                                                                                          |

| Capacitive load for each bus line                                              | Сь               | 15¹                                                 | -    | 150                       | pF   |                                                                                                                  |

<sup>1)</sup> A min. capacitive load is necessary to reach  $t_{\text{OF}}\,$

<sup>2)</sup> A min. capacitive load is necessary to reach  $t_{\text{fmin}}$

# **(infineon**

#### **Technical Data**

### 5.1.3 Electrical Characteristics

Note:

$T_A$  as given for the operating temperature range of the controller unless otherwise stated. All currents flowing into the controller are considered positive.

#### **5.1.3.1** DC Electrical Characteristics

T<sub>A</sub> as given for the controller's operating ambient temperature range unless otherwise stated.

All currents flowing into the controller are considered positive.

**Table 9 Electrical Characteristics**

| Parameter                     | Symbol              | Values                |       |                       | Unit | Note or Test Condition                                                                                                                                 |

|-------------------------------|---------------------|-----------------------|-------|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               |                     | Min.                  | Тур.  | Max.                  |      |                                                                                                                                                        |

| Supply voltage                | V <sub>cc</sub>     | 1.62                  | _     | 5.5                   | V    | Overall functional range                                                                                                                               |

|                               | V <sub>CC_I2C</sub> | 1.62                  | _     | 5.5                   | V    | Supply voltage range for operation of I2C                                                                                                              |

| Supply current <sup>1</sup>   | I <sub>CCAVG</sub>  | _                     | 14.0  | -                     | mA   | While running a typical authentication profile T <sub>A</sub> = 25°C; V <sub>CC</sub> = 5.0 V                                                          |

| Supply current, in sleep mode | I <sub>CCS3</sub>   | -                     | 70    | 100                   | μА   | $T_A$ = 25°C; $V_{CC\_I2C}$ = 3.3 V;<br>I2C ready for operation<br>(no bus activity), all<br>other inputs at $V_{CC}$ , no<br>other interface activity |

| RST input low voltage         | V <sub>IL</sub>     | -0.3                  | _     | 0.3 * V <sub>cc</sub> | V    | $I_{IL} = -50 \mu\text{A} \text{ to } +20 \mu\text{A}$                                                                                                 |

| RST input high voltage        | V <sub>IH</sub>     | 0.7 * V <sub>cc</sub> | _     | $V_{cc} + 0.3$        | V    | $I_{IL} = -50 \mu\text{A} \text{ to } +20 \mu\text{A}$                                                                                                 |

| Hibernate current             | _                   | _                     | < 2.5 | -                     | μΑ   | V <sub>cc</sub> = 0 V, GND = 0 V, RST = 0 V, SCL= 3.3 V and SCL = 3.3 V                                                                                |

<sup>1)</sup> Supply current can be limited from 6mA to 15mA by software commands.

# **5.1.3.2** AC Electrical Characteristics

$T_A$  as given for the controller's operating ambient temperature range unless otherwise stated. All currents flowing into the controller are considered positive.

Table 10 AC Characteristics

| Parameter                   | Symbol            | Values |      |      | Unit | Note or Test Condition                                  |

|-----------------------------|-------------------|--------|------|------|------|---------------------------------------------------------|

|                             |                   | Min.   | Тур. | Max. |      |                                                         |

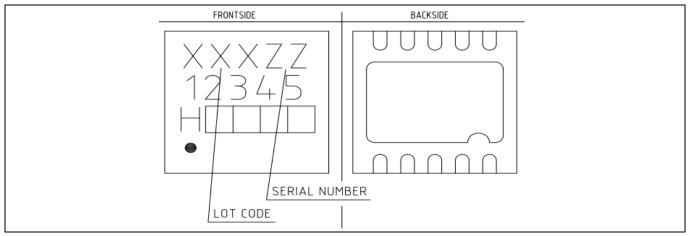

| V <sub>cc</sub> rampup time | t <sub>VCCR</sub> | 1      | -    | 1000 | μs   | 400 mV to 90% of V <sub>cc</sub><br>target voltage ramp |

The  $V_{CC}$  ramp is depicted in Figure 7. 90% of the target supply voltage must be reached within  $t_{VCCR}$  after it has exceeded 400 mV. Moreover, its variation must be kept within a  $\pm 10\%$  range.

### **Technical Data**

Figure 7 V<sub>cc</sub> Rampup

# 5.1.4 Start-Up of I2C Interface

There are 2 variants possible for performing the startup procedure:

- Startup after power-on

- Startup for warm resets

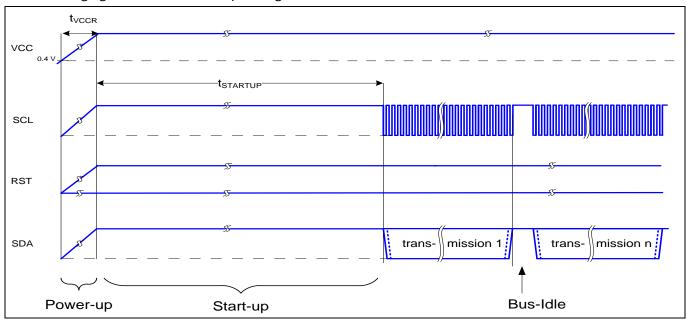

# 5.1.4.1 Startup after Power-On

The activation of the I2C interface after power-on needs the following reset procedure.

- VCC is powered up and the state of the SDA and SCL line are set to high level during power-up

- The first transmission may start at the earliest  $t_{\text{STARTUP}}$  after power-up of the device

The following figure shows the startup timing of the I2C interface for this case.

Figure 8 Startup of I2C Interface after Power-On

#### **Technical Data**

Table 11 Startup of I2C Interface After Power-On

| Parameter    | Symbol               | Values |      |      | Unit | Note or Test Condition |

|--------------|----------------------|--------|------|------|------|------------------------|

|              |                      | Min.   | Тур. | Max. |      |                        |

| Startup time | t <sub>STARTUP</sub> | 15     |      |      | ms   |                        |

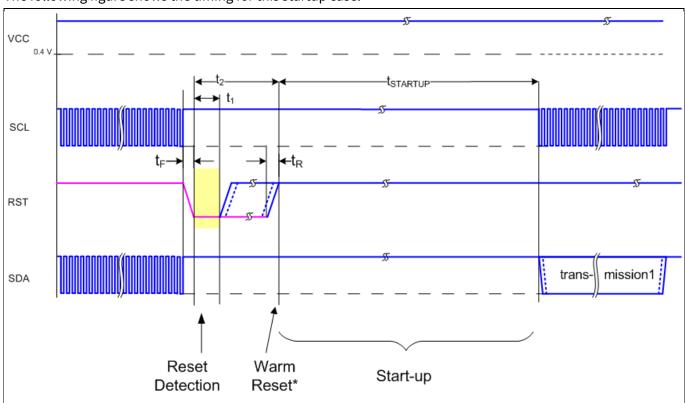

### 5.1.4.2 Startup for Warm Resets

When using the reset signal for triggering a warm reset after power-on, the activation of the I2C interface needs the following reset procedure

- VCC remains powered up.

- The terminal stops I2C communication. SDA and SCL lines are set to high level before RST is set to low level.

- After its falling edge, RST has to be kept at low level for at least t<sub>1</sub>. At the latest t<sub>2</sub> after the falling edge of RST, the terminal must set RST to high level.

- The first transmission may start at the earliest t<sub>STARTUP</sub> after the rising edge of RST

The following figure shows the timing for this startup case.

Figure 9 Startup of I2C Interface for Warm Resets

Note: If NVM programming was requested prior to the reset,  $t_{STARTUP}$  will be extended from a typical value of 15 ms to a maximum of 20 ms.

# **Technical Data**

Table 12 Startup of I2C Interface for Warm Resets<sup>1</sup>

| Parameter       | Symbol               | Values |      |      | Unit | Note or Test Condition              |  |

|-----------------|----------------------|--------|------|------|------|-------------------------------------|--|

|                 |                      | Min.   | Тур. | Max. |      |                                     |  |

| Startup time    | t <sub>STARTUP</sub> | 15     |      |      | ms   |                                     |  |

| Rise time       | t <sub>R</sub>       |        |      | 1    | μs   | From 10% to 90% of signal amplitude |  |

| Fall time       | t₅                   |        |      | 1    | μs   | From 10% to 90% of signal amplitude |  |

| Reset detection | t <sub>1</sub>       | 10     |      |      | μs   |                                     |  |

| Reset low       |                      | 10     |      | 2500 | μs   |                                     |  |

<sup>1)</sup> Reset triggered by software (without power off/on cycle)

# **Connecting to Host**

# **6** Connecting to Host

# **6.1** OPTIGA™ Trust Charge Host Software Architecture

The OPTIGA™ Trust Charge Host Library layers were explained in System Block Diagram Figure 1. In following sections, we will cover how to communicate with OPTIGA™ Trust Charge using I2C.

Figure 10 OPTIGA™ Trust Charge Host Software Architecture

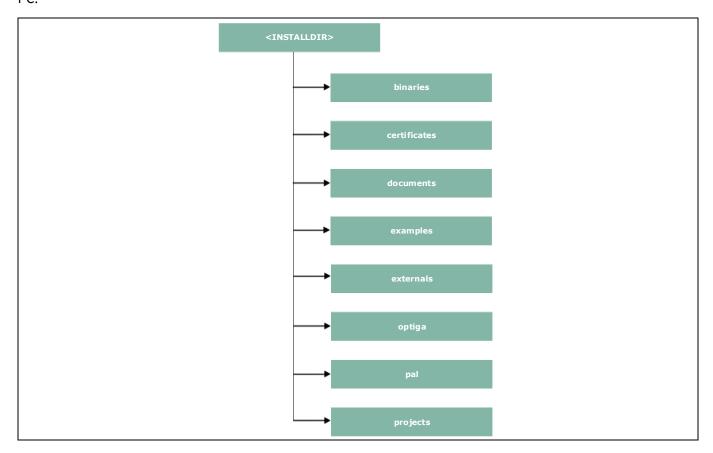

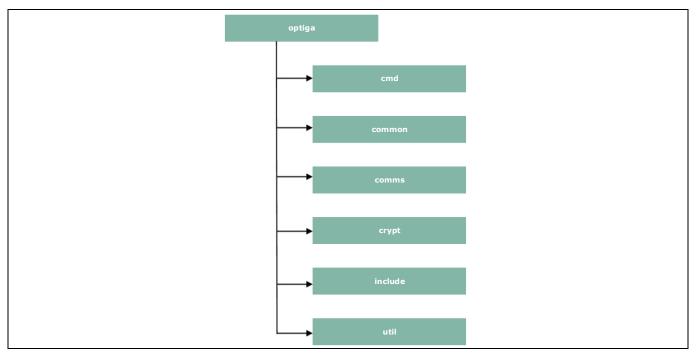

# 6.2 Release Package Folder Structure

The following figure shows the release package structure when OPTIGA™ Trust Charge is installed/extracted on PC.

# **Connecting to Host**

#### Figure 11 Release Package Folder Structure

<INSTALLDIR> is the root directory to which the release package contents are extracted. The following section explains the contents of each subdirectory under installed directory:

#### 3. binaries

This directory contains binaries for OPTIGA™ Trust Charge sample application.

#### 4. certificates

This directory contains OPTIGA™ Trust Charge certificates.

#### 5. documents

This directory contains all relevant OPTIGA™ Trust Charge documentation.

#### 6. examples

This directory contains example usecases for Toolbox features and a tool for generation of manifest for secure data object feature.

#### 7. externals

This directory contains mbedtls software crypto libraries.

#### 8. optiga

This directory contains OPTIGA™ Trust Charge libraries.

#### 9. pal

This directory contains PAL for development kit and for mbedtls and wolfssl software crypto libraries.

#### 10. projects

This directory contains development kit sample project in DAVE™ workspace.

Further the following figure elaborates the OPTIGA™ Trust Charge Host Software folder structure.

# **Connecting to Host**

Figure 12 Host Source Folder Structure

- 1. cmd This folder contains sources for all OPTIGA™ Trust Charge commands

- 2. common This folder contains the common functions used across all the modules

- 3. comms This folder contains the driver to communicate with OPTIGA™ Trust Charge

- 4. crypt This folder contains sources for cryptographic functionalities

- 5. include This folder contains header files for all OPTIGA™ Trust Charge Host Software

- 6. util This folder contains utility functions e.g. read/write and open/close application

# 6.3 Porting Notes

The implementation of Platform Abstraction Layer (PAL) needs to be updated in order to migrate to a new target platform.

The PAL reference code for the XMC4700 IoT connectivity kit is provided as part of package which can be used. The implementation can be found in "<INSTALLDIR>/pal/xmc4700" and the header files are available in "<INSTALLDIR>/optiga/include" with the required APIs used by upper layers. The header files are platform agnostic and would not require any changes. The low level drivers used by PAL for XMC4700 are configured and generated using DAVE™.

# **6.4** Communication with OPTIGA™ Trust Charge

The hardware/platform resource configuration with respect to I2C master and GPIOs (Vdd and Reset) are to be updated in *pal\_ifx\_i2c\_config.c*. These configurations are used by the IFX I2C implementation to communicate with OPTIGA™ Trust Charge.

1. Update I2C master platform specific context[e.g. (void\*)&i2c\_master\_0]

```

001 /**

001 *\brief PAL I2C configuration for OPTIGA

002 */

003 pal_i2c_t optiga_pal_i2c_context_0 =

004 {

005 /// Pointer to I2C master platform specific context

```

# **Connecting to Host**

```

006

(void*)&i2c master 0,

007

/// Slave address

800

0x30,

009

/// Upper layer context

NULL,

010

011

/// Callback event handler

012

NULL

013

};

```

2. Update platform specific context for GPIOs (Vdd and Reset)

```

001

/**

* \brief Vdd pin configuration for OPTIGA

002

003

004

pal_gpio_t optiga vdd 0 =

005

006

// Platform specific GPIO context for the pin used to toggle Vdd

007

(void*) &vdd pin

800

};

009

010

011

* \brief Reset pin configuration for OPTIGA

012

013

pal_gpio_t optiga reset 0 =

014

015

// Platform specific GPIO context for the pin used to toggle Reset

016

(void*) & reset pin

017

};

```

3. Update PAL I2C APIs [pal\_i2c.c] to communicate with OPTIGA™ Trust Charge

The pal\_i2c is expected to provide the APIs for I2C driver initialization, de-initialization, read, write and set bitrate kind of operations

- a) pal\_i2c\_init

- b) pal\_i2c\_deinit

- c) pal\_i2c\_read

- d) pal\_i2c\_write

- e) pal i2c set bitrate

A few target platforms, the I2C master driver initialization (<code>pal\_i2c\_init</code>) is done during the platform start up. In such an environment, there is no need to implement <code>pal\_i2c\_init</code> and <code>pal\_i2c\_deinit</code> functions. Otherwise, these (<code>pal\_i2c\_init</code> & <code>pal\_i2c\_deinit</code>) functions must be implemented as per the upper layer expectations based on the need. The details of these expectations are available in the Host library API documentation (chm).

The reference implementation of PAL I2C based on development kit does not need to have the platform I2C driver initialization explicitly done as part of  $pal\_i2c\_init$  as it is taken care by the DAVE<sup>TM</sup> library initialization. Hence  $pal\_i2c\_init \& pal\_i2c\_deinit$  are not implemented.

In addition to the above specified APIs, the PAL I2C must handle the events from the low level I2C driver and invoke the upper layer handlers registered with PAL I2C context for the respective transaction as shown in the below example.

```

001 //I2C driver callback function when the transmit is completed successfully

002 void i2c_master_end_of_transmit_callback(void)

003 {

```

# **Connecting to Host**

```

004 invoke_upper_layer_callback(gp_pal_i2c_current_ctx,

005 (uint8_t)PAL_I2C_EVENT_TX_SUCCESS);

006 }

```

In above example the I2C driver callback, when transmission is successful invokes the handler to inform the result.

- 4. Update PAL GPIO [pal\_gpio.c] to power on and reset the OPTIGA™ Trust Charge

- f) pal\_gpio\_set\_high

- g) pal\_gpio\_set\_low

- 5. Update PAL Timer [pal\_os\_timer.c] to enable timer

- h) pal\_os\_timer\_get\_time\_in\_milliseconds

- i) pal\_os\_timer\_delay\_in\_milliseconds

- 6. Update Event management for the asynchronous interactions for IFX I2C [pal\_os\_event.c]

- j) pal\_os\_event\_register\_callback\_oneshot

- k) pal\_os\_event\_trigger\_registered\_callback

The *pal\_os\_event\_register\_callback\_oneshot* function is expected to register the handler and context provided as part of input parameters and triggers the timer for the requested time. The p\_pal\_os\_event is an event instance created using *pal\_os\_event\_create*.

```

001

void pal os event register callback oneshot(

002

pal os event t * p pal os event,

003

register callback callback,

004

void* callback args,

005

uint32 t time us)

006

{

007

p pal os event->callback registered = callback;

p pal os event->callback ctx = callback args;

800

009

010

//lint --e{534} suppress "Return value is not required to be checked"

011

TIMER SetTimeInterval (&scheduler timer, (time us*100));

012

TIMER Start (&scheduler timer);

013

```

The handler registered must be invoked once the timer has elapsed as shown in pal\_os\_event\_trigger\_registered\_callback. The pal\_os\_event\_trigger\_registered\_callback is to be registered with event timer interrupt to get trigerred when the timer expires. The pal\_os\_event\_0 is the instance in the pal\_os\_event used store the registered callback and context.

```

001

void pal os event trigger registered callback(void)

002

003

register callback callback;

004

005

TIMER ClearEvent (&scheduler timer);

//lint --e{534} suppress "Return value is not required to be checked"

006

007

TIMER Stop(&scheduler timer);

800

TIMER Clear (&scheduler timer);

009

010

if (pal os event 0.callback registered)

011

012

callback = pal os event 0.callback registered;

```

# **Connecting to Host**

```

013 callback((void * )pal_os_event_0.callback_ctx);

014 }

015 }

```

# 6.5 Reference code for communicating with OPTIGA™ Trust Charge

```

static volatile uint32 t optiga pal event status;

001

002

static void optiga pal i2c event handler (void* upper layer ctx,

003

uint8 t event);

004

005

pal i2c t optiga pal i2c context 0 =

006

/// Pointer to I2C master platform specific context

007

(void*)&i2c master 0,

008

/// Slave address

009

010

0x30,

011

/// Upper layer context

012

NULL,

013

/// Callback event handler

014

NULL,

015

};

016

017

// OPTIGA pal i2c event handler

018

static void optiga pal i2c event handler (void* upper layer ctx,

019

uint8 t event)

020

{

021

optiga pal event status = event;

022

/* Function to verify I2C communication with OPTIGA */

001

002

pal status t test optiga communication (void)

003

004

pal status t pal return status;

005

uint8 t data buffer[10] = \{0x82\};

006

// set callback handler for pal i2c

007

optiga pal i2c context 0.upper layer event handler =

008

optiga pal i2c event handler;

009

010

011

// Send 0x82 to read I2C STATE from optiga

012

do

013

014

optiga pal event status = PAL I2C EVENT BUSY;

015

pal return status =

016

pal i2c write(&optiga pal i2c context 0,

017

data buffer,

018

1);

if (PAL STATUS FAILURE == pal_return_status)

019

020

021

// Pal I2C write failed due to I2C busy is in busy

// state or low level driver failures

022

023

break;

024

}

025

026

// Wait until writing to optiga is completed

```

# **Connecting to Host**

```

while (PAL I2C EVENT SUCCESS != optiga pal event status);

028

029

030

// Read the I2C STATE from OPTIGA

031

do

032

{

033

optiga pal_event_status = PAL_I2C EVENT BUSY;

034

pal return status =

035

pal i2c read(&optiga pal i2c context 0 ,

036

data buffer ,

037

4);

038

// Pal I2C read failed due to I2C busy is in busy

039

// state or low level driver failures

040

if (PAL STATUS FAILURE == pal return status)

041

042

break;

043

}

044

// Wait until reading from optiga is completed

045

} while (PAL I2C EVENT SUCCESS != optiga pal event status);

046

047

return pal return status;

048

}

049

/* Main Function */

050

051

int32 t main(void)

052

DAVE STATUS t status;

053

054

pal status t pal return status;

055

056

// Initialisation of DAVE Apps

057

status = DAVE Init();

058

// Stop if DAVE init fails

059

if (DAVE STATUS FAILURE == status)

060

061

062

while (1U)

063

{ ; }

064

pal return status = test optiga communication();

065

066

067

return (int32 t)pal return status;

068

```

# **OPTIGA™** Trust Charge External Interface

#### **OPTIGA™ Trust Charge External Interface** 7

#### 7.1 **Commands**

This section provides short description of the commands exposed by the OPTIGA™ Trust Charge secuirty chip and mapping of these commands w.r.t Use Cases.

Table 13 **Command table**

| <b>Command Name</b> | Description                                                          |

|---------------------|----------------------------------------------------------------------|

| OpenApplication     | Command to launch an application                                     |

| CloseApplication    | Command to close/hibernate an application                            |

| GetDataObject       | Command to get (read) a data object                                  |

| SetDataObject       | Command to set (write) a data object                                 |

| SetObjectProtected  | Command to set (write) data objects protected (integrity protection) |

| GetRandom           | Command to generate a random stream                                  |

| CalcHash            | Command to calculate a Hash                                          |

| CalcSign            | Command to calculate a signature                                     |

| VerifySign          | Command to verify a signature                                        |

| GenKeyPair          | Command to generate public/private key pairs                         |

#### Table 14 Mapping of commands with Use cases

| Use Case                          | OPTIGA™ Trust Charge commands used |

|-----------------------------------|------------------------------------|

| Charge Authentication request     | GetRandom, CalcHash, VerifySign    |

| Charge Authentication response    | CalcHash, CalcSign                 |

| Datastore (user memory ~ 10kB)    | GetDataObject and SetDataObject    |

| Secure Firmware Update            | VerifySign                         |

| Secure update of Trust Anchors on | SetObjectProtected command         |

| Security Chip                     |                                    |

#### 7.2 **Crypto Performance**

The performance metrics for various schemes are provided by the Table 15 below. If not particularly mentioned, the performance is measured @ OPTIGA™ Trust Charge I/O interface with:

- 12C FM (400KHz)

- Without power limitation

- @ 25°C

- VCC = 3.3V

- ECDSA Signature scheme: ECDSA FIPS 186-3 without hashing

- Hash scheme: SHA256

- ECC Key size: 256 bits (NIST P-256)

# OPTIGA™ Trust Charge External Interface

Table 15 Crypto performance

| Scheme              | Algorithm Performance in ms <sup>1</sup> |             | Performance with<br>Shielded<br>Connection in ms <sup>1</sup> | Notes                                                    |  |

|---------------------|------------------------------------------|-------------|---------------------------------------------------------------|----------------------------------------------------------|--|

| Calculate signature | ECDSA                                    | ~ 60        | ~ 65                                                          | Doesn't include message hashing before calling a toolbox |  |

| Verify signature    | ECDSA                                    | ~ 85        | ~ 90                                                          | function                                                 |  |

| Key pair generation | ECC                                      | ~ 75        | ~ 80                                                          | Generate 256 bit ECC key pair                            |  |

| Hash calculation    | SHA256                                   | ~ 5 Kbyte/s | ~ 4.5 Kbyte/s                                                 | In blocks of 500 bytes                                   |  |

<sup>&</sup>lt;sup>1</sup>Minimum Execution of the entire sequence in milli seconds, except the External World timings

# **Security Monitor**

#### **Security Monitor** 8

The Security Monitor is a central component which enforces the security policy of the OPTIGA™ Trust Charge. It consumes security events sent by security aware parts of the OPTIGA™ Trust Charge embedded SW and takes actions accordingly as specified in Security Policy below.

#### **Security Events** 8.1

The events below actively influence the security monitor.

Table 16 **Security Events**

| Event                   | Description                                                                                                                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Private Key Use         | This event occurs in case the internal services are going to use an OPTIGA™ Trust Charge hosted private key.                                                                                                   |

| Suspect System Behavior | This event occurs in case the embedded software detects inconsistencies with the expected behavior of the system. Those inconsistencies might be redundant information which doesn't fit to their counterpart. |

#### 8.2 **Security Monitor Policy**

Security Monitor judges the notified security events regarding the number of occurrence over time and in case those violate the permitted usage profile of the system takes actions to throttle down the performance and thus the possible frequency of attacks.

The permitted usage profile is defined as:

- 1.  $t_{max}$  is set to 5 seconds ( $\pm$  5%)

- 2. A Suspect System Behavior event is never permitted and will cause setting the Security Event Counter (SEC) to its maximum (= 255).

- 3. One protected operation (refer to Table 16) events per  $t_{max}$  period.

In other words it must not allow more than one out of the protected operations per t<sub>max</sub> period (worst case, ref to bullet 3. above). This condition must be stable, at least after 500 uninterrupted executions of protected operations.

For more information, please refer to Solution Reference Manual document available as part of the package.

# **RoHS Compliance**

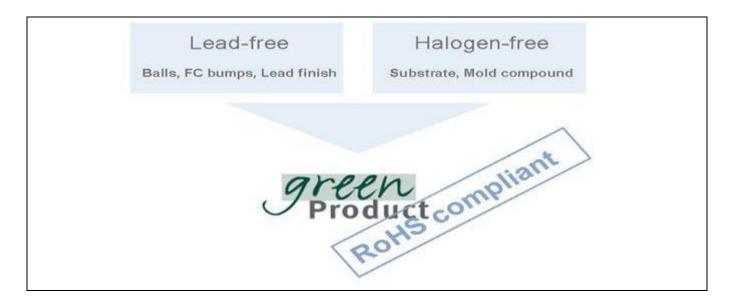

# 9 RoHS Compliance

On January 27, 2003 the European Parliament and the council adopted the directives:

- 2002/95/EC on the Restriction of the use of certain Hazardous Substances in electrical and electronic equipment ("RoHS")

- 2002/96/EC on Waste Electrical and Electrical and Electronic Equipment ("WEEE")

Some of these restricted (lead) or recycling-relevant (brominated flame retardants) substances are currently found in the terminations (e.g. lead finish, bumps, balls) and substrate materials or mold compounds.

The European Union has finalized the Directives. It is the member states' task to convert these Directives into national laws. Most national laws are available, some member states have extended timelines for implementation. The laws arising from these Directives have come into force in 2006 or 2007.

The electro and electronic industry has to eliminate lead and other hazardous materials from their products. In addition, discussions are on-going with regard to the separate recycling of ceratin materials, e.g. plastic containing brominated flame retardants.

Infineon Technologies is fully committed to giving its customers maximum support in their efforts to convert to lead-free and halogen-free<sup>1</sup> products. For this reason, Infineon Technologies' "Green Products" are ROHS-compliant.

Since all hazardous substances have been removed, Infineon Technologies calls its lead-free and halogen-free semiconductor packages "green." Details on Infineon Technologies' definition and upper limits for the restricted materials can be found here.

The assembly process of our high-technology semiconductor chips is an integral part of our quality strategy. Accordingly, we will accurately evaluate and test alternative materials in order to replace lead and halogen so that we end up with the same or higher quality standards for our products.

The use of lead-free solders for board assembly results in higher process temperatures and increased requirements for the heat resistivity of semiconductor packages. This issue is addressed by Infineon Technologies by a new classification of the Moisture Sensitivity Level (MSL). In a first step the existing products have been classified according to the new requirements.

<sup>&</sup>lt;sup>1</sup>Any material used by Infineon Technologies is PBB and PBDE-free. Plastic containing brominated flame retardants, as mentioned in the WEEE directive, will be replaced if technically/economically beneficial.

Datasheet 28 Revision 1.30

# Appendix A - Infineon I2C Protocol Registry Map

#### Appendix A - Infineon I2C Protocol Registry Map 10

OPTIGA™ Trust Charge supports IFX I2C v2.01 and is implemented as I2C slave, which uses different address locations for status, control and data communication registers. These registers with description are outlined below in the following table.

Table 17 **IFX I2C Registry Map Table**

| Register<br>Address | Name                       | Size in Bytes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Master<br>Access |

|---------------------|----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0x80                | DATA                       | DATA_REG_LEN  | This is the location where data shall be read from or written to the I2C slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read /<br>Write  |

| 0x81                | DATA_REG_LEN               | 2             | This register holds the maximum data register (Addr 0x80) length. The allowed values are 0x0010 up to 0xFFFF. After writing the new data register length it becomes effective with the next I2C master access. However, in case the slave could not accept the new length it indicates its maximum possible length within this register. Therefore it is recommended to read the value back after writing it to be sure the I2C slave did accept the new value.  Note: the value of MAX_PACKET_SIZE is derived from this value or vice versa (MAX_PACKET_SIZE=DATA_REG_LEN-5) | Read /<br>Write  |

| 0x82                | I2C_STATE                  | 4             | Bits 31:24 of this register provides the I2C state in regards to the supported features (e.g. clock stretching) and whether the device is busy executing a command and/or ready to return a response etc.  Bits 15:0 defining the length of the response data                                                                                                                                                                                                                                                                                                                 | Read only        |

| 0x83                | BASE_ADDR                  | 2             | block at the physical layer.  This register holds the I2C base address as specified by Table 18. Default value is 0x30. After writing a different address the new address become effective with the next I2C master access. In case the bit 15 is set in addition to the new address (bit 6:0) it becomes the new default address at reset (persistent storage).                                                                                                                                                                                                              | Write only       |

| 0x84                | MAX_SCL_FREQU              | 4             | This register holds the maximum clock frequency in KHz supported by the I2C slave. The value gets adjusted to the register I2C_Mode setting. Fast Mode (Fm): The allowed values are 50 up to 400. Fast Mode (Fm+): The allowed values are 50 up to 1000.                                                                                                                                                                                                                                                                                                                      | Read             |

| 0x85                | GUARD_TIME <sup>1</sup>    | 4             | For details refer to Table 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read only        |

| 0x86                | TRANS_TIMEOUT <sup>1</sup> | 4             | For details refer to Table 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read only        |

<sup>&</sup>lt;sup>1</sup> In case the register returns 0xFFFFFFF the register is not supported and the default values specified in Table 'List of protocol variations' shall be applied.

# Appendix A – Infineon I2C Protocol Registry Map

| Register<br>Address | Name       | Size in Bytes | Description                                                                                          | Master<br>Access |

|---------------------|------------|---------------|------------------------------------------------------------------------------------------------------|------------------|

| 0x88                | SOFT_RESET | 2             | Writing to this register will cause a device reset. This feature is optional                         | Write only       |

| 0x89                | I2C_MODE   | 2             | This register holds the current I2C Mode as defined by Table 19. The default mode is SM & FM (011B). | Read /<br>Write  |

### Table 18 Definition of BASE\_ADDR

| Fields    | Bits | Value     | Description                                                          |  |  |  |  |  |  |

|-----------|------|-----------|----------------------------------------------------------------------|--|--|--|--|--|--|

| DEF_ADDR  | 15   | 0         | Volatile address setting by bit 6:0, lost after reset.               |  |  |  |  |  |  |

|           |      | 1         | Persistent address setting by bit 6:0, becoming default after reset. |  |  |  |  |  |  |

| BASE_ADDR | 6:0  | 0x00-0x7F | I <sup>2</sup> C base address specified by Table 17                  |  |  |  |  |  |  |

| 15       | 14 | 13 | 12 | 11        | 10 | 9 | 8 |

|----------|----|----|----|-----------|----|---|---|

| DEF_ADDR |    |    |    | RFU       |    |   |   |

| 7        | 6  | 5  | 4  | 3         | 2  | 1 | 0 |

| RFU      |    |    |    | BASE_ADDR |    |   |   |

| 15       | 14  | 13  | 12 | 11   | 10 | 9 | 8 |  |

|----------|-----|-----|----|------|----|---|---|--|

| DEF_MODE | RFU |     |    |      |    |   |   |  |

| 7        | 6   | 5   | 4  | 3    | 2  | 1 | 0 |  |

|          |     | RFU |    | Mode |    |   |   |  |

|          |     |     |    |      |    |   |   |  |

### Table 19 Definition of I2C\_MODE

| Fields            | Bits | Value        | Description                                                                                     |

|-------------------|------|--------------|-------------------------------------------------------------------------------------------------|

| DEF_MODE          | 15   | 0            | Volatile mode setting by bit 2:0, lost after reset.                                             |

|                   |      | 1            | Persistent mode setting by bit 2:0, becoming default after reset. This bit is always read as 0. |

| MODE <sup>2</sup> | 2:0  | 001          | Sm                                                                                              |

|                   |      | 010          | Fm                                                                                              |

|                   |      | 011          | SM & Fm (fab out default)                                                                       |

|                   |      | 100          | Fm+                                                                                             |

|                   |      | other values | not valid; writing will be ignored                                                              |

$<sup>^{\</sup>rm 1}$  In case the register returns 0xFFFFFFF the register and its functionality is not supported

<sup>&</sup>lt;sup>2</sup> This mode defines the adherence of the bus signals to the electrical characteristics according standard I2C bus specification

# Appendix A - Infineon I2C Protocol Registry Map

| 31            | 30       | 29 | 28          | 27               | 26        | 25        | 24             |

|---------------|----------|----|-------------|------------------|-----------|-----------|----------------|

| BUSY          | RESP_RDY | RI | =U          | SOFT_RESET       | CONT_READ | REP_START | CLK_STRETCHING |

| 23            | 22       | 21 | 20          | 19               | 18        | 17        | 16             |

| PRESENT_LAYER |          |    |             | RFU              | J         |           |                |

|               |          |    |             | 15-0             |           |           |                |

|               |          |    | Length of o | data block to be | read      |           |                |

#### **Definition of I2C\_STATE** Table 20

| Field          | Bit(s) | Value | Description                              |

|----------------|--------|-------|------------------------------------------|

| BUSY           | 31     | 0     | Device is not busy                       |

|                |        | 1     | Device is busy executing a command       |

| RESP_RDY       | 30     | 0     | Device is not ready to return a response |

|                |        | 1     | Device is ready to return a response     |

| SOFT_RESET     | 27     | 0     | SOFT_RESET not supported                 |

|                |        | 1     | SOFT_RESET supported                     |

| CONT_READ      | 26     | 0     | Continue Read not supported              |

|                |        | 1     | Continue Read supported                  |

| REP_START      | 25     | 0     | Repeated start not supported             |

|                |        | 1     | Repeated start supported                 |

| CLK_STRETCHING | 24     | 0     | Clock stretching not supported           |

|                |        | 1     | Clock stretching supported               |

| PRESENT_LAYER  | 23     | 0     | Presentation Layer not supported         |

|                |        | 1     | Presentation Layer supported             |

#### **Infineon I2C Protocol Variations** 10.1

To fit best to application specific requirements the protocol might be tailored by specifying a couple of parameters which is described in the following table.

**List of Protocol Variations** Table 21

| Parameter       | <b>Default Value</b> | Description                                                                                                                                                                                                                                                |

|-----------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX_PACKET_SIZE | 0x110                | Maximum packet size accepted by the receiver. The protocol limits this value to 0xFFFF, but there might be project specific requirements to reduce the transport buffers size for the sake of less RAM footprint in the communication stack. If shortened, |

|                 |                      | it could be statically defined or negotiated at the physical layer.                                                                                                                                                                                        |

| WIN_SIZE        | 1                    | Window size of the sliding windows algorithm. The value could                                                                                                                                                                                              |

|                 |                      | be 1 up to 2.                                                                                                                                                                                                                                              |

| MAX_NET_CHAN    | 1                    | Maximum number of network channels. The value could be 1 up                                                                                                                                                                                                |

|                 |                      | to 16. One indicates the OSI Layer 3 is not used and the CHAN                                                                                                                                                                                              |

|                 |                      | field of the PCTR must be set to 0000.                                                                                                                                                                                                                     |

| CHAINING        | TRUE                 | Chaining on the transport layer is supported (TRUE) or not                                                                                                                                                                                                 |

|                 |                      | (FALSE)                                                                                                                                                                                                                                                    |

| TRANS_TIMEOUT   | 10 ms                | (Re) transmission timeout specifies the number of milliseconds                                                                                                                                                                                             |

|                 |                      | to be elapsed until the transmitter considers a frame                                                                                                                                                                                                      |

# Appendix A – Infineon I2C Protocol Registry Map

| Parameter     | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |               | transmission is lost and retransmits the non-acknowledged frame. The Timer gets started as soon as the complete frame is transmitted. The value could be 1 up to 1000. However, the higher the number, the longer it takes to recover from a frame transmission error.  Note: The acknowledge timeout on the receiver side must be                                                                                                         |

|               |               | shorter than the retransmission timeout to avoid unnecessary frame repetitions.                                                                                                                                                                                                                                                                                                                                                            |