# **Datasheet**

BL54L15µ Series

Version 1.1

## **Revision History**

| rsion           | Date         | Notes                                                                                                                                               | Contributor(s) | Approver      |

|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|

| 0.1             | 02 Oct 2024  | Preliminary release.                                                                                                                                | Raj Khatri     | Jonathan Kaye |

| 0.2 18 Oct 2024 |              | 18 Oct 2024 Updated table4 external antenna list to                                                                                                 |                | Jonathan Kaye |

|                 |              | Added antenna Ezurio iFlexPIFA Mini EFG2401A3S-<br>10MH4L to External Antenna Integration with BL54L15µ<br>RF trace pin variant (453-00224)         |                |               |

|                 |              | Change Mag Layers EDA-8709-2G4C1-B27-CY antenna gain from 2dBi to 2.32dBi.                                                                          |                |               |

| 0.3             | 5 Nov 2024   | Updated height of module to 1.75 mm.                                                                                                                | Dave Drogowski | Jonathan Kaye |

| 0.4             | 20 Nov 2024  | Updated power supply voltage to 1.7 – 3.6 V.                                                                                                        | Dave Drogowski | Jonathan Kaye |

| 0.5             | 19 Feb. 25   | Updated 6. Mechanical Details, 7.On -Board PCB Chip<br>Antenna Characteristics, 8.Application Note for Surface<br>Mount Modules, 9.Reliability Test | Louis Chang    | Jonathan Kaye |

| 0.6             | 18 Mar. 25   | Update Power consumption in 2.1                                                                                                                     | Louis Chang    | Jonathan Kaye |

| 0.7             | 11 Apr. 25   | Change (VDD_nRF) operating range from 1.7V-3.6V to 1.7V-3.5V.                                                                                       | Louis Chang    |               |

|                 |              | Add VDD_nRF supply voltage (1.7V-3.3V) under extended operating Temperature (85 to 105C)                                                            |                |               |

|                 |              | Update Absolute maximum ratings of VDD_nRF (-0.3V-3.6V)                                                                                             |                |               |

| 1.0             | 26 June 2025 | Initial Release.                                                                                                                                    | Louis Chang    | Jonathan Kaye |

|                 |              |                                                                                                                                                     | Dave Drogowski |               |

| 1.1             | 1 Aug 2025   | Updated max output power to +8 dBm                                                                                                                  | Dave Drogowski | Jonathan Kaye |

## Contents

| 1 | Ove   | rview and Key Features                                                       | 5  |

|---|-------|------------------------------------------------------------------------------|----|

|   | 1.1   | Features and Benefits                                                        | 5  |

|   | 1.2   | Application Areas                                                            | 5  |

| 2 | Spe   | cification                                                                   | 6  |

|   | 2.1   | Specification Summary                                                        | 6  |

| 3 | Hard  | dware Specifications                                                         | 9  |

|   | 3.1   | Block Diagram and Pin-out                                                    | 9  |

|   | 3.2   | Pin Definitions                                                              | 11 |

|   | 3.3   | Electrical Specifications                                                    | 15 |

|   | 3.3.1 | Absolute Maximum Ratings                                                     | 15 |

|   | 3.3.2 | 2 Recommended Operating Parameters                                           | 16 |

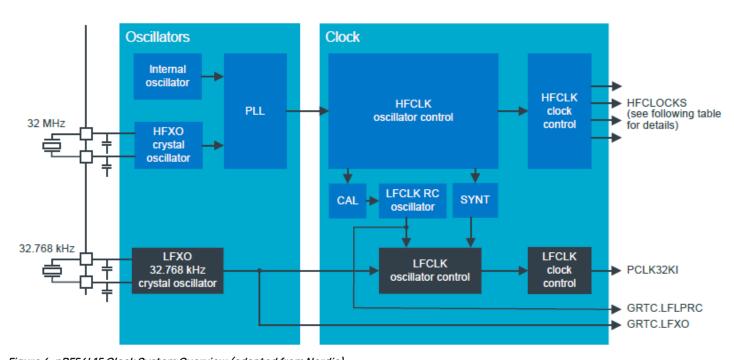

|   | 3.4   | Clocks                                                                       | 17 |

|   | 3.4.1 | HFXO - 32MHz crystal oscillator and nRF54L15 internal load capacitor setting | 17 |

|   | 3.4.2 | 2 LFCLK – Low Frequency clock source                                         | 17 |

|   | 3.4.3 | 3 Other Internal Clocks                                                      | 17 |

|   | 3.5   | BL54L15µ Power Supply                                                        | 18 |

| 4 | Man   | ndatory SW requirements related to hardware                                  | 19 |

|   | 4.1   | 32MHz crystal internal load capacitor setting                                | 19 |

| 5 | Hard  | dware Integration Suggestions                                                | 20 |

|   | 5.1   | Circuit                                                                      | 20 |

|   | 5.2   | PCB Layout on Host PCB - General                                             | 21 |

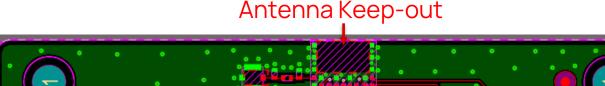

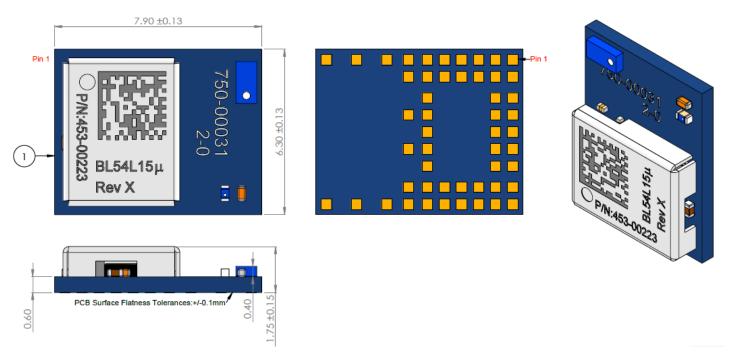

|   | 5.3   | PCB Layout on Host PCB for the 453-00223                                     | 21 |

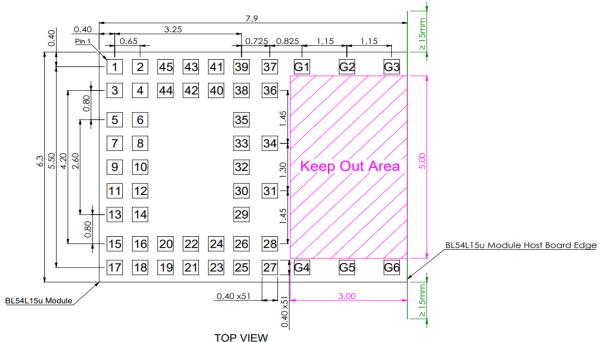

|   | 5.3.1 | I Antenna Keep-out on Host PCB                                               | 21 |

|   | 5.3.2 | 2 Antenna Keep-out and Proximity to Metal or Plastic                         | 21 |

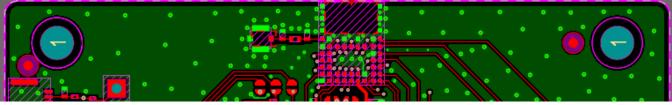

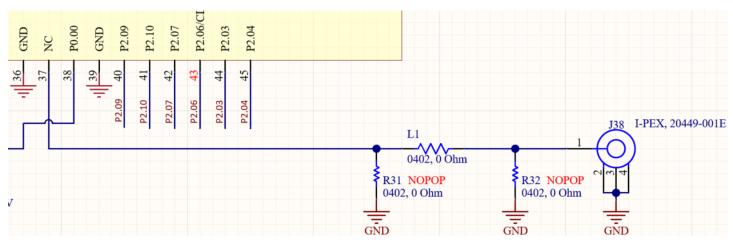

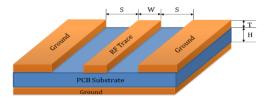

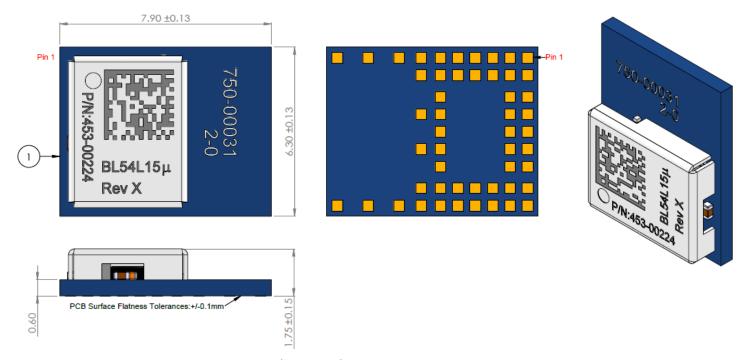

|   | 5.4   | 50-Ohms RF Trace on Host PCB for BL54L15µ RF pad variant (453-00224)         | 22 |

|   | 5.5   | External Antenna Integration with BL54L15µ RF trace pin variant (453-00224)  | 26 |

| 6 | Мес   | chanical Details                                                             | 27 |

|   | 6.1   | BL54L15u Mechanical Details                                                  | 27 |

|   | 6.2   | Host PCB Land Pattern and Antenna Keep-out for the 453-00223                 | 28 |

| 7 | On -  | Board PCB Chip Antenna Characteristics                                       | 29 |

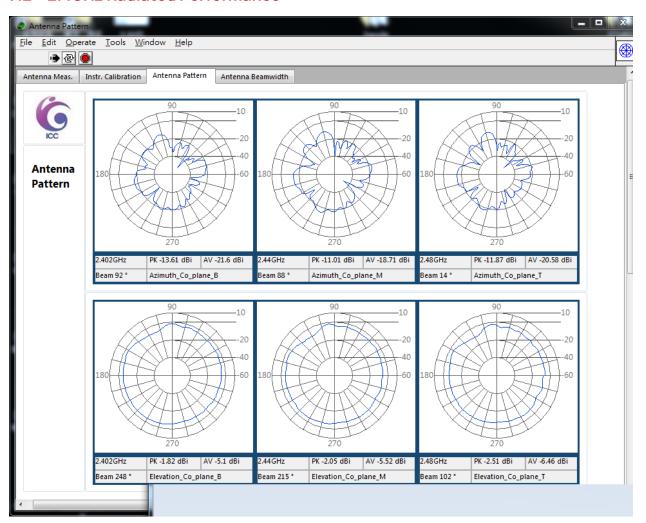

|   | 7.1   | Summary of Antenna Performance                                               | 29 |

|   | 7.2   | 2.4GHz Radiated Performance                                                  | 29 |

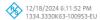

|   | 7.3   | Antenna S11 measuring data                                                   | 30 |

| 8 | Арр   | lication Note for Surface Mount Modules                                      | 31 |

|   | 8.1   | Introduction                                                                 | 31 |

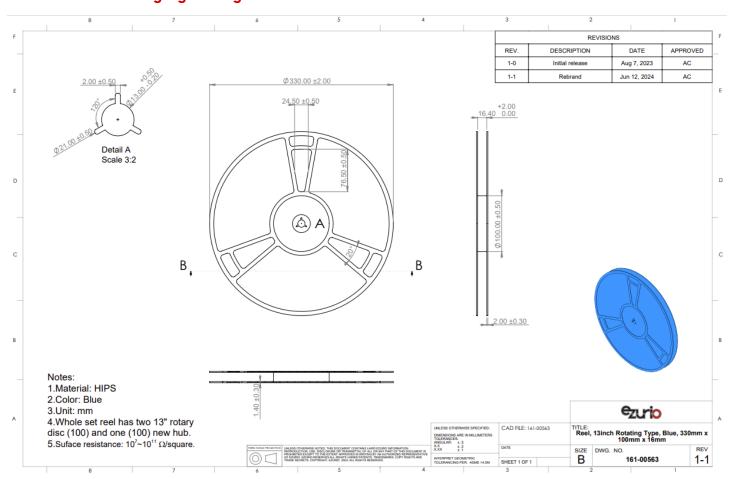

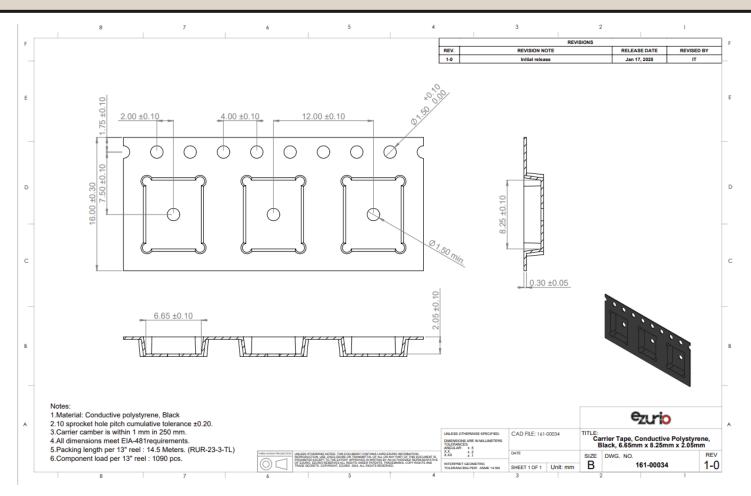

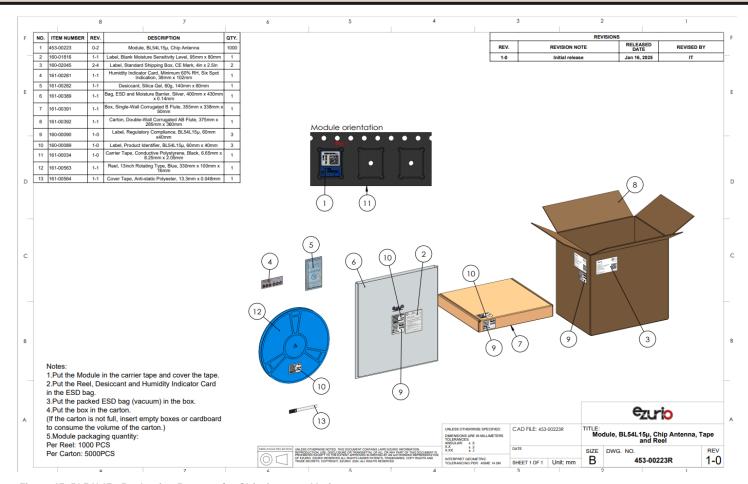

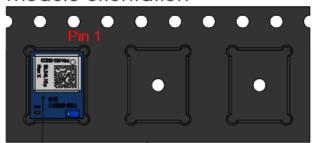

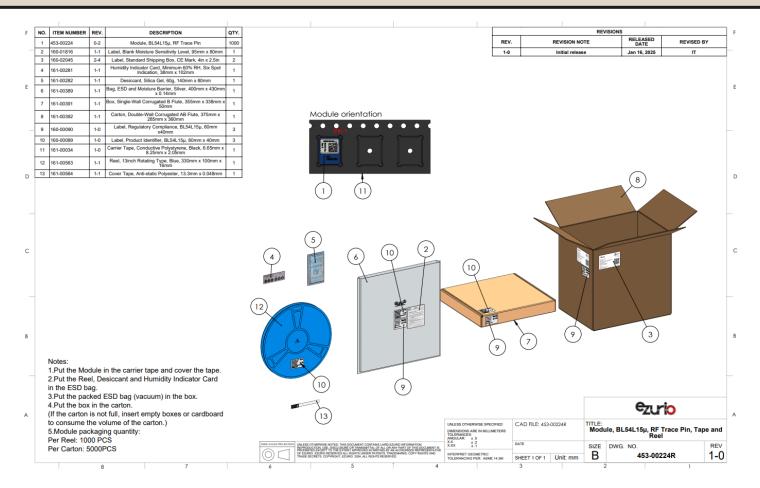

|   | 8.2   | Module Packaging Configuration                                               | 31 |

|   | 8.3   | Module Shipping                                                              | 35 |

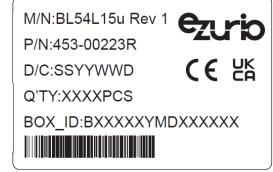

|   | 8.4   | Labeling                                                                     | 35 |

|    | 8.5    | Required Storage Conditions                                                                            | 37 |

|----|--------|--------------------------------------------------------------------------------------------------------|----|

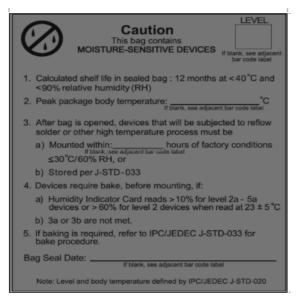

|    | 8.5.1  | Prior to Opening the Dry Packing                                                                       | 37 |

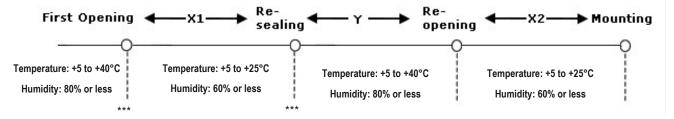

|    | 8.5.2  | After Opening the Dry Packing                                                                          | 37 |

|    | 8.5.3  | Temporary Storage Requirements after Opening                                                           | 37 |

|    | 8.6    | Baking Conditions                                                                                      | 38 |

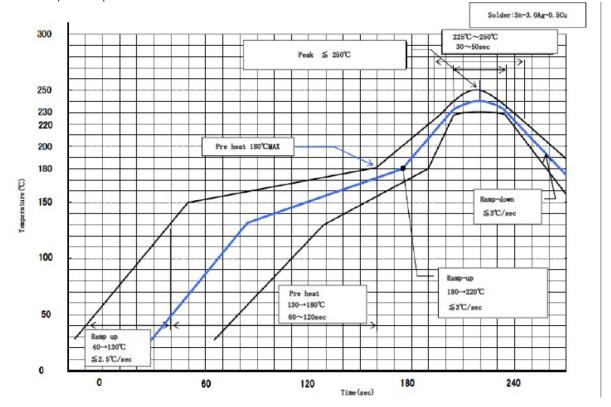

|    | 8.7    | Surface Mount Conditions                                                                               | 38 |

|    | 8.7.1  | Soldering                                                                                              | 38 |

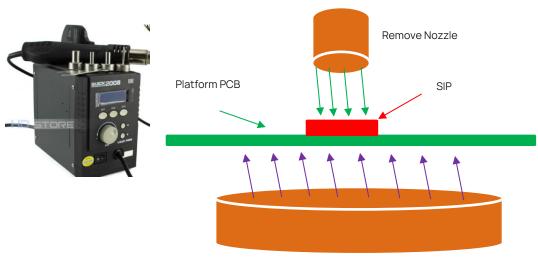

|    | 8.7.2  | Cautions When Removing the SIP from the Platform for RMA                                               | 39 |

|    | 8.7.3  | Precautions for Use                                                                                    | 39 |

| 9  | Relial | bility Test                                                                                            | 40 |

|    | 9.1    | Climatic And Dynamic Reliability Test                                                                  | 40 |

|    | 9.2    | Reliability MTBF Prediction                                                                            | 41 |

| 10 | Regu   | latory                                                                                                 | 42 |

|    | 10.1   | Certified Antennas for the BL54L15u                                                                    | 42 |

| 11 | Orde   | ring Information                                                                                       | 43 |

| 12 | Bluet  | ooth Qualification Process                                                                             | 44 |

|    | 12.1   | Overview                                                                                               | 44 |

|    | 12.2   | Scope                                                                                                  | 44 |

|    | 12.3   | Qualification Steps When Referencing multiple existing designs, (unmodified) – Option 2a in the QPRDv3 | 44 |

|    | 12.4   | Example Design Combinations                                                                            | 45 |

|    | 12.5   | Qualify More Products                                                                                  | 46 |

| 13 | Addit  | ional Information                                                                                      | 47 |

## 1 Overview and Key Features

Experience a new pinnacle of performance, efficiency, and security with our new BL54L15µ series, built on Nordic Semiconductor's powerful nRF54 silicon. Elevating what you know and love from the nRF52 series, this next generation redefines Bluetooth LE and 802.15.4 solutions. Unleashing enhanced processing power, expanded memory, and innovative peripherals, the BL54L15µ is the ultimate choice for low power connectivity, in the smallest footprint.

Powered by **Nordic's nRF54L15** (WLCSP 300um) SoC, our ultra compact BL54L15µ modules deliver secure and robust Bluetooth LE and 802.15.4 with flexible programming via the Nordic SDK, Zephyr RTOS and Canvas Software Suite.

Featuring a 128MHz ARM Cortex M33 and 128MHz RISC-V coprocessor, supported by 1.5 MB non-volatile memory and 256 KB RAM, the BL54L15µ modules offer double the processing power (vs prior BL654 – nRF52840). The BL54L15µ series brings out all nRF54L15 hardware features and capabilities including up to +8 dBm transmit power, 1.7V – 3.5V supply considerations, and NFC A-Tag implementation.

It's further enhanced with state-of-the-art security and is designed for PSA Certified level 3. It supports services such as Secure Boot, Secure Firmware Update, Secure Storage plus protection from physical attacks.

Note:

$BL54L15\mu$  hardware provides all functionality of the nRF54L15 chipset used in the module design. This is a hardware datasheet only – it does not cover the software aspects of the  $BL54L15\mu$ . This is to acknowledge that information in this datasheet is referenced from the nRF54L15 datasheet.

#### 1.1 Features and Benefits

- Nordic nRF54L15 2.4 x 2.25mm WSCLP with 32 GPIOs utilized.

- Multi-protocol support: Bluetooth LE Core 6.0, 802.15.4 (Thread/Matter)

- Cortex M33 processor core: 128 MHz ARM Cortex M33

- RISC-V co-processor core: 128 MHz VPR

- Memory: 1.5MB non-volatile memory, 256 KB RAM

- High Speed Peripherals: HS-SPI/UART, software defined peripherals on 128 MHz VPR, GPIO - 1x 64 MHz Port, 1.7 - 3.5V, 11 GPIOs

- Low Leakage Peripherals: 2x QDEC, 7x Timer, Global RTC, 2x WDT, NFC A-Tag, TEMP, I2S, COMP, 3x PWM, LPCOMP, 14-bit 8CH ADC, 5x TWI/SPI/UART, GPIO (2x 16 MHz Port (P0, P1), 20 GPIO's, 1.7-3.6V, 32 GPIO)

- Antenna choice integrated pre-certified Chip antenna or external antenna support via Trace Pad

- Ultra-small footprint (6.3 mm x 7.9 mm x 1.75 mm)

- Extended Industrial Temperature Rating (-40° to +105 °C)

- Development choice: Zephyr RTOS, Nordic nRF Connect SDK & Canvas

- Bluetooth LE: Peripheral/Central, 2 Mbps (high throughput), LE Coded (long range), AoA/AoD, Mesh

- Firmware Over the Air **(FOTA)** via MCUboot and Zephyr

- Hostless operation Multi Core MCU reduces BOM

- Fully featured development kits to jump start Bluetooth LE development

## 1.2 Application Areas

- Building Automation

- Security

- Medical Peripherals

- Industrial Sensors

## 2 Specification

## 2.1 Specification Summary

| Categories/Feature                                           | Implementation                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wireless Specification                                       |                                                                                                                                                                                                                                                                                                                           |

| Bluetooth <sup>®</sup>                                       | Bluetooth 6.0 - Single mode  GATT client/server - Any adopted/custom services  Central/Peripheral roles  Bluetooth LE mesh  2M PHY  LE Coded PHY  LE Advertising Extensions  LE secure connections  Data packet length extensions  LE privacy v1.2  LE ping  DTM Firmware (Test Modes)                                    |

| IEEE 802.15.4-2020 PHY                                       | <ul> <li>2405–2480 MHz IEEE 802.15.4-2006 radio transceiver, implementing IEEE 802.15.4-2006 compliant</li> <li>250kbps, 2450MHz, O-QPSK PHY</li> <li>Channels 11-26. Channel 11 2405MHz and CH26 2480MHz.</li> <li>Clear channel assessment (CCA)</li> <li>Energy detection (ED) scan</li> <li>CRC generation</li> </ul> |

| Nordic proprietary 1Mbps,<br>2Mbps, 4Mbps modes<br>radio     | <ul> <li>2402–2480 MHz Nordic proprietary 1Mbps and 2Mbps modes radio transceiver</li> <li>1Mbps nRF proprietary mode (ideal transmitter)</li> <li>2Mbps nRF proprietary mode (ideal transmitter)</li> <li>4Mbps nRF proprietary mode (ideal transmitter)</li> </ul>                                                      |

| Frequency                                                    | 2.402 - 2.480 GHz for BLE (CH0 to CH39)<br>2.405 - 2.480 GHz for IEEE 802.15.4-2006 PHY (CH11 to CH26)                                                                                                                                                                                                                    |

| Raw Data Rates                                               | 1 Mbps BLE (over-the-air) 2 Mbps BLE (over-the-air) 125 kbps BLE (over-the-air) 500 kbps BLE (over-the-air) 250 kbps IEEE 802.15.4 802.15.4-2006 (over-the-air) Nordic proprietary 1Mbps, 2Mbps and 4Mbps modes (over-the-air)                                                                                            |

| Maximum Transmit Power                                       | +8 dBm Conducted 453-00001 (Integrated antenna) (Exclude antenna gain)                                                                                                                                                                                                                                                    |

| Setting                                                      | +8 dBm Conducted 453-00044 (External antenna) (Test at MHF4 connector)                                                                                                                                                                                                                                                    |

| Minimum Transmit Power<br>Setting                            | -40dBm                                                                                                                                                                                                                                                                                                                    |

| Receive Sensitivity <sup>1</sup><br>(≤37byte packet for BLE) | BLE 1 Mbps (BER=1E-3) -95dBm typical  BLE 2 Mbps -92dBm typical  BLE 125 kbps -103dBm typical  BLE 500 kbps -98.5dBm typical  IEEE 802.15.4-2006 250kbps TBD dBm typical                                                                                                                                                  |

| Link Budget (conducted)                                      | 102 dB @ BLE 1 Mbps (TX power used is 7dBm) 110 dB @ BLE 125 kbps (TX power used is 7dBm)                                                                                                                                                                                                                                 |

| NFC                    |                                                                                                                                                                                                                                     |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NFC-Type A Listen mode | Based on NFC forum specification: 13.56 MHz, Date rate 106 kbps, NFC Type2 and Type 4 emulation                                                                                                                                     |  |

| compliant              | Modes of Operation: Disable, Sense, Activated                                                                                                                                                                                       |  |

|                        | Use Cases: Touch-to-Pair with NFC, NFC enabled Out-of-Band Pairing                                                                                                                                                                  |  |

| Security               | Designed for PSA Certified Level 3 with Secure Boot, Secure Firmware Update, and Secure Storage. Integrated tamper sensors detect attacks and take action, and cryptographic accelerators are hardened against sidechannel attacks. |  |

| FLPR) dedicated for                               |

|---------------------------------------------------|

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

| tem time. Can run in<br>lock, 32.76kHz when other |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

| phones                                            |

| •                                                 |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

| Host Interfaces and<br>Peripherals      | Applications Core<br>(High Performance) | Software defined peripheral Core<br>(ultra-low power)                                                                                                                                                                                                                               |

|-----------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NFC A-Tag                               |                                         | 1x                                                                                                                                                                                                                                                                                  |

| Wakeup pins                             |                                         | 21                                                                                                                                                                                                                                                                                  |

| External optional<br>32.768 kHz crystal |                                         | Not needed for normal radio operation.  Optionally, connect +/-20ppm accuracy crystal for more accurate protocol timing. Fit associated load capacitor for crystal or use nRF54L15 internal load capacitor, which is configurable as 4 pF to 18 pF in 0.5pF steps on pins XL1, XL2. |

| Security                                | •                                       | vel 3 with Secure Boot, Secure Firmware Update, and Secure Storage. Integrated ks and take action, and cryptographic accelerators are hardened against side-channel                                                                                                                 |

| Zephyr RTOS                    | Via SWD (JTAG) 2 wire interface                                                           |         |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------|---------|--|--|--|

| Programmability Options        | Nordic nRFConnect SDK: Software/Support available from Nordic directly                    |         |  |  |  |

|                                | https://devzone.nordicsemi.com/                                                           |         |  |  |  |

|                                | Zephyr RTOS: Software/Support available from https://www.zephyrproject.org/               |         |  |  |  |

|                                | Canvas SW Suite: Software/ Support available from https://www.ezurio.com/canvas/software/ | e-suite |  |  |  |

| FW upgrade                     | Via SWD (JTAG) 2 wire interface or UART                                                   |         |  |  |  |

| Supply Voltage                 | 1.7V-3.5V                                                                                 |         |  |  |  |

| Power Consumption              |                                                                                           |         |  |  |  |

| Active Modes Peak Current (for | 29 mA peak Tx@ 1.8V, LE1M                                                                 |         |  |  |  |

| maximum Tx power +8dBm)        | 23 mA peak Tx@ 1.8V, CW                                                                   |         |  |  |  |

| – Radio only                   | 16 mA peak Tx@ 3.3V, LE1M                                                                 |         |  |  |  |

|                                | 13 mA peak Tx@ 3.3V, CW                                                                   |         |  |  |  |

| Active Modes Peak Current (for | 9 mA peak Tx @ 1.8V, LE1M                                                                 |         |  |  |  |

| Tx power -40dBm) - Radio only  | 6.5 mA peak Tx @ 1.8V, CW                                                                 |         |  |  |  |

|                                | 6 mA peak Tx @ 3.3V, LE1M                                                                 |         |  |  |  |

|                                | 5 mA peak Tx @ 3.3V, CW                                                                   |         |  |  |  |

| Ultra-low Power Modes          | System ON Idle 3 uA (System ON IDLE with GRTC (XOSC) and 256 KB RAM)                      |         |  |  |  |

|                                | System OFF 0.6 uA                                                                         |         |  |  |  |

| Antenna Options                |                                                                                           | ı       |  |  |  |

| Internal                       | Chip antenna - on-board (453-00223 variant)                                               |         |  |  |  |

| External                       | Connection via off module IPEX MHF4 (453-00224 RF trace pin variant)                      |         |  |  |  |

| Physical                       |                                                                                           |         |  |  |  |

| Dimensions                     | 7.9mm x 6.3mm x 1.75mm                                                                    |         |  |  |  |

|                                | Pad Pitch - 0.65 mm                                                                       |         |  |  |  |

|                                | Pad Type – Two rows of pads (LGA - Land Grid Array).                                      |         |  |  |  |

| Weight                         | <1 gram                                                                                   |         |  |  |  |

| Environmental                  |                                                                                           |         |  |  |  |

| Operating                      | -40 °C to +105 °C                                                                         |         |  |  |  |

| Storage                        | -40 °C to +105 °C                                                                         |         |  |  |  |

| Miscellaneous                  |                                                                                           |         |  |  |  |

| Lead Free                      | Lead-free and RoHS compliant                                                              |         |  |  |  |

| Warranty                       | One-Year Warranty                                                                         |         |  |  |  |

| Development Tools              | ·                                                                                         |         |  |  |  |

| Development Kit                | Development kit per module SKU (453-00223-K1 and 453-00224-K1 respectively)               |         |  |  |  |

| Development Tools              | Nordic nRFConnect - Android and iOS applications                                          |         |  |  |  |

|                                | UART firmware upgrade                                                                     | Xb      |  |  |  |

|                                | Tools and utilities                                                                       |         |  |  |  |

| Bluetooth®                     | Full Bluetooth SIG Declaration ID                                                         |         |  |  |  |

| FCC/ISED/CE/MIC/RCM/UKCA       | All BL54L15µ Series                                                                       |         |  |  |  |

## 3 Hardware Specifications

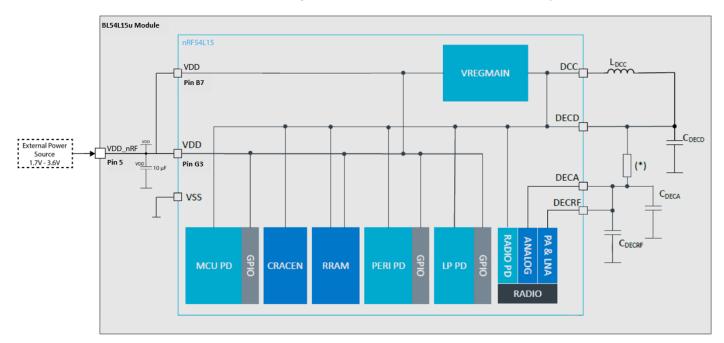

## 3.1 Block Diagram and Pin-out

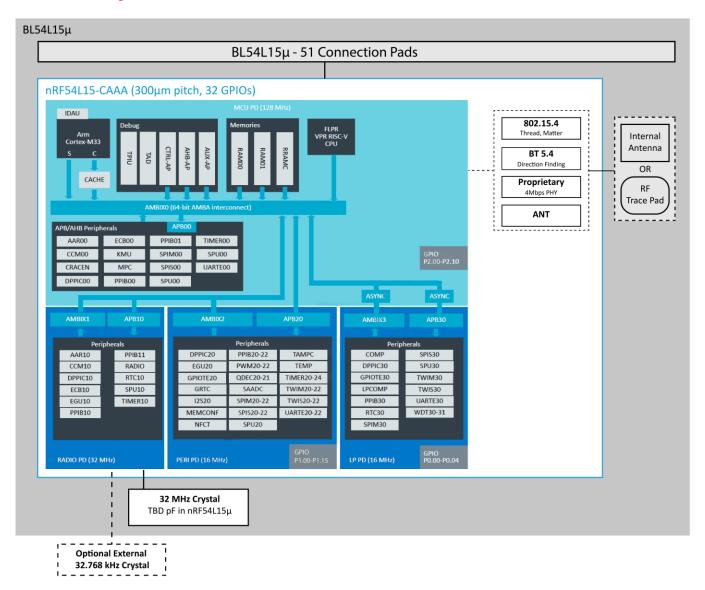

Figure 1: BL54L15µ HW block diagram

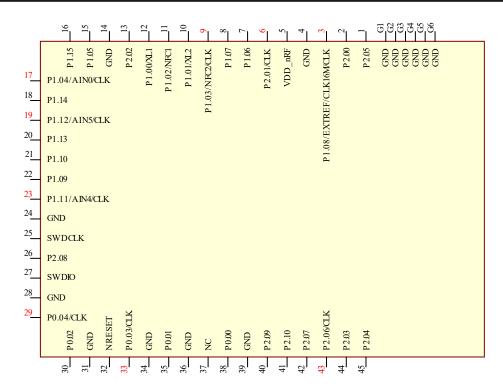

Figure 2: Top view - Schematic symbol for 453-00223 BL54L15µ Module (Nordic nRF54L15-CAAA) - Chip Antenna variant

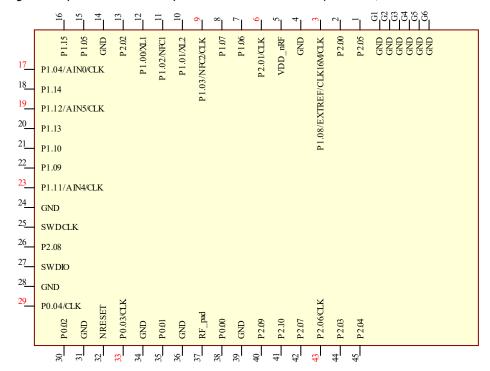

Figure 3: Top view - Schematic symbol for 453-00224 BL54L15µ Module (Nordic nRF54L15-CAAA) - RF Trace pin variant

## 3.2 Pin Definitions

Table 1: Pin definitions

| Pin<br># | Pin definitions  Pin Name (red coloured pins for clock for interfaces, trace) | nRF54L15-<br>CAAA<br>300um<br>WLCSP,<br>32 GPIOs | nRF54L15-CAAA 300u pitch<br>WLCSP, 32GPIOs Name | Description                                                       | Example usage                                                                                                                                  |

|----------|-------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | P2.05                                                                         | G5                                               | P2.05                                           | General purpose I/O SPIM CS SPIS CS UARTE RTS FLPR.5 QSPI CS      | SPIM00/20<br>SPIS00/20<br>UARTE00/20<br>FLPR<br>FLPR (QSPI)                                                                                    |

| 2        | P2.00                                                                         | G6                                               | P2.00                                           | General purpose I/O<br>SPIM DCX<br>UARTE RXD<br>FLPR.4<br>QSPI D3 | SPIM00/20<br>UARTE00/20<br>FLPR<br>FLPR (QSPI)                                                                                                 |

| 3        | P1.08/GRTCHFOUT/EXTREF                                                        | F7                                               | P1.08 EXTREF                                    | General purpose I/O GRTC CLKOUTFAST External reference for SAADC  | Clock pin                                                                                                                                      |

| 5        | GND<br>VDD_nRF                                                                | G3                                               | VSS<br>VDD                                      | 1.7V-3.5V, connect external supply of 1.7V-3.5V to pin5(VDD_nRF)  |                                                                                                                                                |

| 6        | P2.01                                                                         | G7                                               | P2.01                                           | General purpose I/O<br>SPIM SCK<br>SPIS SCK<br>FLPR.0<br>QSPI SCK | Clock pin<br>SPIM00/20<br>SPIS00/20<br>FLPR<br>FLPR (QSPI)                                                                                     |

| 7        | P1.06/ASO[1]/AIN2                                                             | D7                                               | P1.06<br>ASO[1]<br>AIN2                         | General purpose I/O TAMPC active shield 1 output Analog input     | TAMPC                                                                                                                                          |

| 8        | P1.07/ASI[1]/AIN3                                                             | E7                                               | P1.07<br>ASI[1]<br>AIN3                         | General purpose I/O TAMPC active shield 1 input Analog input      | TAMPC                                                                                                                                          |

| 9        | P1.03/NFC2                                                                    | D5                                               | P1.03<br>NFC2                                   | General purpose I/O<br>NFC antenna connection                     | Clock pin                                                                                                                                      |

| 10       | P1.01/XL2                                                                     | C6                                               | P1.01<br>XL2                                    | General purpose I/O<br>Connection for 32.768 kHz<br>crystal       | Ezurio Devkit: Optional 32.768kHz crystal pad XL2, XL1 and associated built-in configurable internal capacitors inside nRF54L15- CAAA chipset. |

| 11       | P1.02/NFC1                                                                    | C7                                               | P1.02<br>NFC1                                   | General purpose I/O<br>NFC antenna connection                     |                                                                                                                                                |

| XL1  Connection for 32.768 kHz crystal  pa ass co int ins CA  13 P2.02/SWO  F6 P2.02  General purpose I/O SPIM SDO SPIS SDO SPIS SDO SPIS SDO SPIS SDO | zurio Devkit: ptional 2.768kHz crystal ad XL2, XL1 and associated built-in pnfigurable ternal capacitors side nRF54L15- AAA chipset. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| SPIM SDO SP<br>SPIS SDO SP                                                                                                                             |                                                                                                                                      |

| SPIS SDO SP                                                                                                                                            |                                                                                                                                      |

|                                                                                                                                                        | PIM00/20                                                                                                                             |

| UARTE TXD UA                                                                                                                                           | PIS00/20                                                                                                                             |

|                                                                                                                                                        | ARTE00/20                                                                                                                            |

| FLPR.1 FLI                                                                                                                                             | _PR                                                                                                                                  |

| QSPI D0 FLI                                                                                                                                            | _PR (QSPI)                                                                                                                           |

| Serial wire output (SWO) Tra                                                                                                                           | ace                                                                                                                                  |

| 14 GND VSS                                                                                                                                             |                                                                                                                                      |

| 15 P1.05/ASI[0]/AIN1 E6 P1.05 General purpose I/O                                                                                                      |                                                                                                                                      |

| TAMPC active shield unput                                                                                                                              | AMPC<br>ADIO                                                                                                                         |

| AIN1 RADIO DEGPIO                                                                                                                                      | ADIO                                                                                                                                 |

| Analog input                                                                                                                                           |                                                                                                                                      |

| 16 P1.15 B6 P1.15 General purpose I/O                                                                                                                  |                                                                                                                                      |

| ACC[0]                                                                                                                                                 | lock pin<br>AMPC                                                                                                                     |

| AINO                                                                                                                                                   | AIVIPC                                                                                                                               |

| Output                                                                                                                                                 |                                                                                                                                      |

| 18 P1.14/RADIO[5]/AIN7 B5 P1.14 General purpose I/O                                                                                                    |                                                                                                                                      |

| DADIO[E]                                                                                                                                               | ADIO                                                                                                                                 |

| AINT                                                                                                                                                   | ADIO                                                                                                                                 |

| Analog input                                                                                                                                           | la alombia                                                                                                                           |

|                                                                                                                                                        | lock pin<br>AMPC                                                                                                                     |

|                                                                                                                                                        | ADIO                                                                                                                                 |

| AIN5 Analog input                                                                                                                                      | .5.0                                                                                                                                 |

| 20 P1.13/RADIO[4]/AIN6 B4 P1.13 General purpose I/O                                                                                                    |                                                                                                                                      |

|                                                                                                                                                        | ADIO                                                                                                                                 |

| AIN6 Analog input                                                                                                                                      |                                                                                                                                      |

| 21 P1.10/ASI[2]/RADIO[1] C3 P1.10 General purpose I/O                                                                                                  |                                                                                                                                      |

| Please see note 7 ASI[2] TAMPC active shield 2 input                                                                                                   | AMPC                                                                                                                                 |

| RADIO[1] RADIO DFEGPIO RA                                                                                                                              | ADIO                                                                                                                                 |

| 22 P1.09/ASO[2]/RADIO[0] B3 P1.09 General purpose I/O                                                                                                  |                                                                                                                                      |

|                                                                                                                                                        | AMPC                                                                                                                                 |

| RADIO[0] output RA                                                                                                                                     | ADIO                                                                                                                                 |

| RADIO DEEGPIO                                                                                                                                          |                                                                                                                                      |

| Pin<br># | Pin Name (red coloured pins for clock for interfaces, trace) | nRF54L15-<br>CAAA<br>300um<br>WLCSP,<br>32 GPIOs | nRF54L15-CAAA 300u pitch<br>WLCSP, 32GPIOs Name | Description                                                                                       | Example usage                                                                                                                  |

|----------|--------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 23       | P1.11/ASO[3]/RADIO[2]/AIN4<br>Please see note 7              | C4                                               | P1.11<br>ASO[3]<br>RADIO[2]<br>AIN4             | General purpose I/O TAMPC active shield 3 output RADIO DFEGPIO Analog input                       | Clock pin<br>TAMPC<br>RADIO                                                                                                    |

| 24       | GND                                                          | -                                                | VSS                                             |                                                                                                   |                                                                                                                                |

| 25       | SWDCLK                                                       | E3                                               | SWDCLK                                          | Serial Wire Debug clock input<br>with on-chip pull-up for<br>debug and programming                |                                                                                                                                |

| 26       | P2.08/TRACEDATA[1]                                           | D4                                               | P2.08<br>TRACEDATA[1]                           | General purpose I/O<br>FLPR.8<br>Trace data<br>SPIM SDO<br>SPIS SDO<br>UARTE TXD                  | FLPR<br>Trace<br>SPIM00/21<br>SPIS00/21<br>UARTE00/21                                                                          |

| 27       | SWDIO                                                        | F2                                               | SWDIO                                           | Serial Wire Debug IO<br>withstandard-drive and on-<br>chip pull-down for debug and<br>programming |                                                                                                                                |

| 28       | GND                                                          | -                                                | VSS                                             |                                                                                                   |                                                                                                                                |

| 29       | P0.04/GRTCLFCLKOUT                                           | D3                                               | P0.04                                           | General purpose I/O<br>GRTC CLKOUT32K                                                             | Clock pin<br>GRTC                                                                                                              |

| 30       | P0.02                                                        | E2                                               | P0.02                                           | General purpose I/O                                                                               |                                                                                                                                |

| 31       | GND                                                          | -                                                | VSS                                             |                                                                                                   |                                                                                                                                |

| 32       | nRESET                                                       | D2                                               | nRESET                                          | Pin RESET with internal pull-<br>up resistor (13k Ohms).<br>System Reset (Active Low).            |                                                                                                                                |

| 33       | P0.03/GRTCPWM                                                | E1                                               | P0.03                                           | General purpose I/O<br>GRTC PWM                                                                   | Clock pin<br>GRTC                                                                                                              |

| 34       | GND                                                          | -                                                | VSS                                             |                                                                                                   |                                                                                                                                |

| 35       | P0.01                                                        | F1                                               | P0.01                                           | General purpose I/O                                                                               |                                                                                                                                |

| 36       | GND                                                          | -                                                | VSS                                             |                                                                                                   |                                                                                                                                |

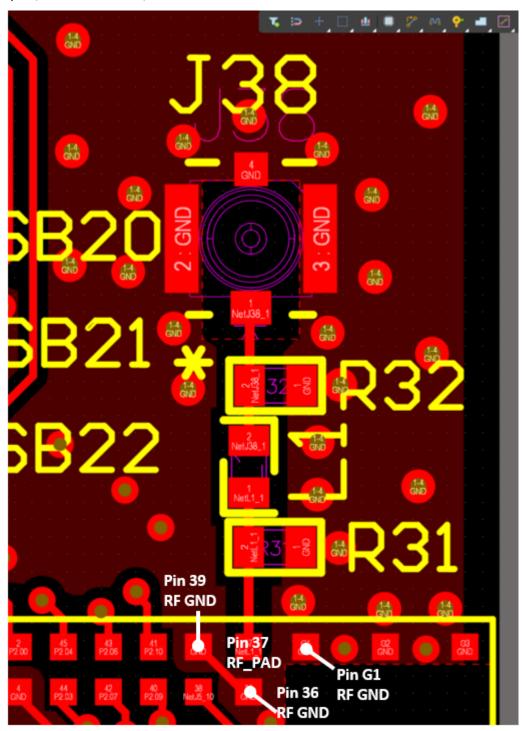

| 37       | RF_pad or NC                                                 | D1                                               | ANT                                             | Single ended radio antenna connection                                                             | RF pad active on<br>BL54L15µ RF pin<br>variant 453-<br>00224. NC on<br>BL54L15µ<br>Integrated<br>antenna variant<br>453-00223. |

| 38       | P0.00                                                        | G1                                               | P0.00                                           | General purpose I/O                                                                               |                                                                                                                                |

| 39<br>40 | GND P2.09/TRACEDATA[2]                                       | -<br>F3                                          | VSS<br>P2.09<br>TRACEDATA[2]                    | General purpose I/O<br>FLPR.9<br>Trace data<br>SPIM SDI<br>SPIS SDI<br>UARTE CTS                  | FLPR<br>Trace<br>SPIM00/21<br>SPIS00/21<br>UARTE00/21                                                                          |

| Pin<br>#                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Name (red colou<br>pins for clock for<br>interfaces, trace) | red nRF54L15-<br>CAAA<br>300um<br>WLCSP,<br>32 GPIOs                      | nRF54L15-CAAA 300u pitch<br>WLCSP, 32GPIOs Name                                                              | Description                                                                                                                                                   | Example usage                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 41                                                                                                                                                                                                                                                                                                                                                                                                           | P2.10/TRACEDATA[3]                                              | G2                                                                        | P2.10<br>TRACEDATA[3]                                                                                        | General purpose I/O FLPR.10 Trace data SPIM CS SPIS CS UARTE RTS                                                                                              | FLPR<br>Trace<br>SPIM00/21<br>SPIS00/21<br>UARTE00/21       |

| 42                                                                                                                                                                                                                                                                                                                                                                                                           | P2.07/TRACEDATA[0]                                              | /SWO E4                                                                   | P2.07<br>TRACEDATA[0]<br>SWO                                                                                 | General purpose I/O<br>FLPR.7<br>Trace data<br>Serial wire output (SWO)<br>SPIM DCX<br>UARTE RXD                                                              | FLPR<br>Trace<br>Trace<br>SPIM00/21<br>UARTE00/21           |

| 43                                                                                                                                                                                                                                                                                                                                                                                                           | P2.06/TRACECLK                                                  | F4                                                                        | P2.06<br>TRACECLK                                                                                            | General purpose I/O<br>FLPR.6<br>SPIM SCK<br>SPIS SCK<br>Trace clock                                                                                          | Clock pin<br>FLPR<br>SPIM00/21<br>SPIS00/21<br>Trace        |

| 44                                                                                                                                                                                                                                                                                                                                                                                                           | P2.03                                                           | E5                                                                        | P2.03                                                                                                        | General purpose I/O<br>FLPR.3<br>QSPI D2                                                                                                                      | FLPR<br>FLPR (QSPI)                                         |

| 45                                                                                                                                                                                                                                                                                                                                                                                                           | P2.04                                                           | F5                                                                        | P2.04                                                                                                        | General purpose I/O<br>SPIM SDI<br>SPIS SDI<br>UARTE CTS<br>FLPR.2<br>QSPI D1                                                                                 | SPIM00/20<br>SPIS00/20<br>UARTE00/20<br>FLPR<br>FLPR (QSPI) |

| G1                                                                                                                                                                                                                                                                                                                                                                                                           | GND                                                             | -                                                                         | VSS                                                                                                          | 40.15.                                                                                                                                                        |                                                             |

| G2                                                                                                                                                                                                                                                                                                                                                                                                           | GND                                                             | -                                                                         | VSS                                                                                                          |                                                                                                                                                               |                                                             |

| G3                                                                                                                                                                                                                                                                                                                                                                                                           | GND                                                             | -                                                                         | VSS                                                                                                          |                                                                                                                                                               |                                                             |

| G4                                                                                                                                                                                                                                                                                                                                                                                                           | GND                                                             | -                                                                         | VSS                                                                                                          |                                                                                                                                                               |                                                             |

| G5                                                                                                                                                                                                                                                                                                                                                                                                           | GND                                                             | -                                                                         | VSS                                                                                                          |                                                                                                                                                               |                                                             |

| G6                                                                                                                                                                                                                                                                                                                                                                                                           | GND                                                             | -                                                                         | VSS                                                                                                          |                                                                                                                                                               |                                                             |

| Pin Definition Notes:  Note 1  GPIO = General Input or Output (GPIO level voltage tracks VDD pin). AIN = Analog input.  GPIO  If GPIO is selected as an input, ensure the input is not floating (which can cause current consumption to drive with time in low power modes (such as System ON Idle), by selecting the internal pull up or pull down.  Must connect all GND pads to host board PCB GND plane. |                                                                 |                                                                           |                                                                                                              |                                                                                                                                                               | onsumption to drive                                         |

| Clock                                                                                                                                                                                                                                                                                                                                                                                                        | for serial interfaces<br>or trace                               | optimized to ensure c<br>can be used as clock s<br>The peripheral data si | orrect timing relationship betwee<br>signals are shown with pin name ir<br>gnal must be configured to use pi | ave clock signals. Dedicated clock pen clock and data signal for these pen red colour. Insclose to the clock pin. This ensume delay, so that the data and clo | eripherals. Pins that<br>res that the                       |

|                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |                                                                           | s, the printed circuit board (PCB)                                                                           | layout must use short PCB traces of sures close to identical delay and cl                                                                                     | ~                                                           |

| Pin<br># | Pin Name (red colo<br>pins for clock for<br>interfaces, trace) | C <i>A</i><br>30<br>Wi                                                           | RF54L15-<br>AAA<br>Oum<br>LCSP,<br>GPIOs | nRF54L15-CAAA 300u pitch<br>WLCSP, 32GPIOs Name                                           | Description                 | Example usage                 |  |  |

|----------|----------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|--|--|

|          | Note 3                                                         | UARTE20/21:                                                                      | Can use                                  | any pin on GPIO port P1. Can be co                                                        | nnected across power don    | nains to dedicated pin on P2. |  |  |

|          | Dedicated pins                                                 | SPIM00:                                                                          |                                          | cated pins on GPIO port P2. For 32I                                                       | MHz operation, the pins mu  | ust be configured using extra |  |  |

|          |                                                                |                                                                                  | •                                        | e E0/E1 configuration.                                                                    |                             |                               |  |  |

|          |                                                                | SPIM20/21:                                                                       |                                          | any pin on GPIO port P1. Can be co                                                        | •                           | •                             |  |  |

|          |                                                                | SPIS20/21:                                                                       |                                          | se any pin on GPIO port P1. Can be connected across power domains to dedicated pin on P2. |                             |                               |  |  |

|          |                                                                | TRACE:                                                                           |                                          | cated pins on GPIO port P2. For 32I                                                       | MHz operation, the pins mu  | ust be configured using extra |  |  |

|          |                                                                |                                                                                  |                                          | high drive E0/E1 configuration.                                                           |                             |                               |  |  |

|          |                                                                | GRTC:                                                                            |                                          | cated pins for clock and PWM outp                                                         |                             |                               |  |  |

|          |                                                                | TAMPC: Has dedicated pins for active shield inputs and outputs.                  |                                          |                                                                                           |                             |                               |  |  |

|          |                                                                | FLPR: Uses dedicated pins on GPIO port P2 for emulated peripherals such as QSPI. |                                          |                                                                                           |                             |                               |  |  |

|          |                                                                | RADIO:                                                                           |                                          | dicated pins on GPIO port P1 for ant                                                      |                             | SPIO for direction finding).  |  |  |

|          |                                                                | NFC:                                                                             | Uses ded                                 | dicated pin listed in pin definitions                                                     | table1.                     |                               |  |  |

|          | Note 4                                                         | Customer M                                                                       | UST bring                                | out SWDIO, SWCLK, nRESET, VDD,                                                            | GND for programming purp    | ooses.                        |  |  |

| SWDIC    | O / SWCLK / nRESET                                             |                                                                                  |                                          |                                                                                           |                             |                               |  |  |

|          | / VDD / GND                                                    |                                                                                  |                                          |                                                                                           |                             |                               |  |  |

|          | Note 5                                                         | P1.15 GPIO is                                                                    | only availa                              | able on the BL54L15µ which uses nf                                                        | RF54-CAAA(300um pitch)      | which as 32 GPIO's.           |  |  |

|          | GPIO P2.15                                                     |                                                                                  |                                          |                                                                                           |                             |                               |  |  |

|          | Note 6                                                         | RF_pad (pin:                                                                     | 37) is for th                            | ne BL54L15µ RF pad variant (453-00                                                        | 0224) module only. If using | the BL54L15µ module RF pad    |  |  |

|          | RF_PAD                                                         | variant (453-                                                                    | -00224), c                               | sustomer MUST copy the 50-Ohms                                                            | GCPW RF track design, det   | tailed in 50-Ohms RF Trace on |  |  |

|          |                                                                | Host PCB for                                                                     | BL54L15µ                                 | RF pad variant (453-00224)                                                                |                             |                               |  |  |

|          | Note 7                                                         | If GPIOs P1.0                                                                    | 9, P1.10, P1                             | .11, and P1.12 are used, please appl                                                      | y the following operations. |                               |  |  |

|          |                                                                | • Add a 330 s                                                                    | Ω or larger                              | series resistance directly after the                                                      | tracks enter the outer lay  | er of the PCB.                |  |  |

|          |                                                                | <ul> <li>Keep PCB t</li> </ul>                                                   | racks as s                               | short as possible and in between gr                                                       | ound layers if possible.    |                               |  |  |

|          |                                                                | <ul> <li>Use togglir</li> </ul>                                                  | ng speed le                              | ower than 1 MHz                                                                           |                             |                               |  |  |

|          |                                                                | If unused, lea                                                                   | ave these                                | pins unconnected.                                                                         |                             |                               |  |  |

## 3.3 Electrical Specifications

### 3.3.1 Absolute Maximum Ratings

Absolute maximum ratings are the extreme limits for supply voltage and voltages on digital and analogue pins of the module are listed below; exceeding these values causes permanent damage.

Table 2: Absolute maximum ratings

| able 2: Absolute maximum ratings  |                  |               |                    |

|-----------------------------------|------------------|---------------|--------------------|

| Parameter                         | Min              | Max           | Unit               |

| Supply Voltages                   |                  |               |                    |

| VDD_nRF                           | -0.3             | 3.6           | V                  |

| I/O pin voltage                   |                  |               |                    |

| Voltage at GPIO pin (at VDD≤3.5V) | -0.3             | VDD_nRF + 0.3 | V                  |

| Voltage at GPIO pin (at VDD>3.5V) |                  | 3.6           | V                  |

| NFC antenna pin current (NFC1/2)  | -                | 130           | mA                 |

| Environmental                     |                  |               |                    |

| Storage temperature               | -40              | +105          | °C                 |

| MSL (Moisture Sensitivity Level)  | -                | 4             | -                  |

| ESD (as per EN301-489)            |                  |               |                    |

| Conductive                        |                  | 4             | kV                 |

| Air Coupling                      |                  | 8             | kV                 |