# **Universal Serial Bus Transceiver**

- Utilizes digital inputs and outputs to transmit and receive USB cable data

- Supports 12Mbps "Full Speed" and 1.5Mbps "Low Speed" serial data transmission

- Compatible with the VHDL "Serial Interface Engine" from USB developer's conference

- Hysteresis on VP and VM Function)

- Ease of use for PC peripheral expansion

- Protocol flexibility for mixed-mode isochronous data transfers and asynchronous messaging

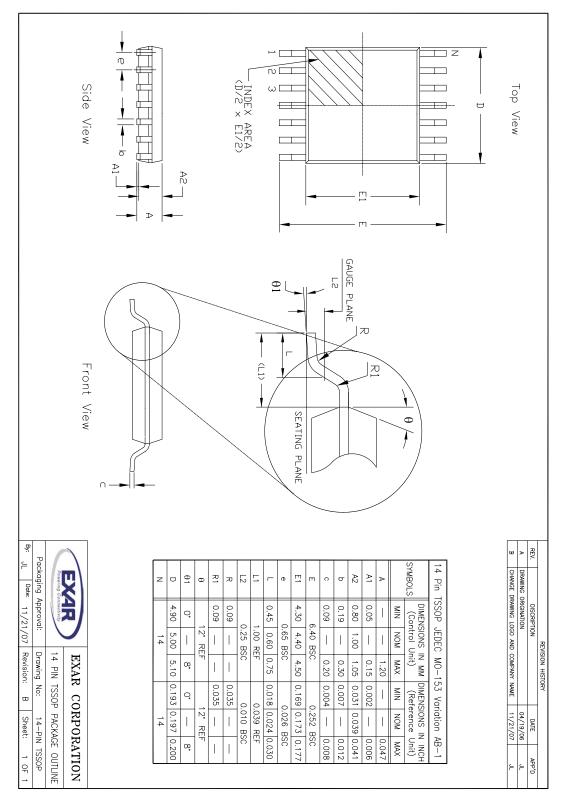

- Available in 14 pin TSSOP package

- Rail to Rail receiver common mode input range, 20mV typical receiver sensitivity

- Low Power; 20 nA in SUSPEND mode

- Enhanced version of the PDIUSBP11

#### DESCRIPTION

The SP5301 is a half-duplex Universal Serial Bus (USB) differential transceiver that interfaces with the USB Serial Interface Engine (SIE). The SP5301 is designed to allow 3.3V or 5.0V standard and programmable logic to interface with the physical layer of the Universal Bus. The USB protocol can support multiple connections for up to 127 physical devices composed of many diverse functions. It is capable of transmitting and receiving serial data at both full speed (12Mbps) and low speed (1.5Mbps) data rates. Implementation of the Serial Interface Engine along with the USB transceiver allow the designer to make flexible USB compatible devices with widely available logic components. The SP5301 is specifically geared towards low-cost USB solutions for the PC peripheral market.

#### **ABSOLUTE MAXIMUM RATINGS**

$I_{o}$  (DC output source or sink current for

$I_{o}$  (DC output source or sink current for

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.  $V_{cc}$ ......0.5V to +6.5V  $I_{GND'}$ ,  $I_{CC}$  (DC  $V_{cc}$  or GND current)......±100mA Input Current and Voltages:  $I_{IK}$  (DC input diode current at  $V_{I} < 0$ )......-50mA  $V_{I}$  (DC input voltage, Note 1).....-0.5V to  $V_{cc} + 0.5V$ Output Currents and Voltages:  $I_{OK}$  (DC output voltage range, I/O).....-0.5V to  $V_{cc} + 0.5V$ Output Currents and Voltages:  $I_{OK}$  (DC output diode current where  $V_{O} > V_{cc}$  or  $V_{O} < 0$ ).....±50mA  $V_{O}$  (DC output voltage), Note 1......-0.5V to ( $V_{cc} + 0.5V$ )

VP/VM/RCV/RERR/RSEO pins, Vo = 0 to Vcc).....±15mA

D+/D- pins, V<sub>o</sub> = 0 to V<sub>cc</sub>.....±50mA Storage Temperature.....-65°C to +150°C Ptot (Power dissipation per package)......1000mW

CAUTION: ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

| NOTE 1: The input and output voltage ratings may be exceeded if the input and output clamp current ratings are |

|----------------------------------------------------------------------------------------------------------------|

| observed.                                                                                                      |

| ŌĒ | SUSPND | RCV    | RERR   | RSEO   | VP/VM  | D+/D-  | Comments        |

|----|--------|--------|--------|--------|--------|--------|-----------------|

| 0  | 0      | 0      | 0      | 0      | 0      | Active | Driving         |

| 0  | 1      | 0      | 0      | 0      | 0      | Active | Driving         |

| 1  | 0      | Active | Active | Active | Active | HI-Z   | Receiving       |

| 1  | 1      | 0      | Active | Active | Active | HI-Z   | Low Power State |

**Function Table**

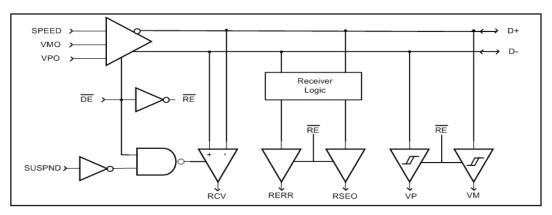

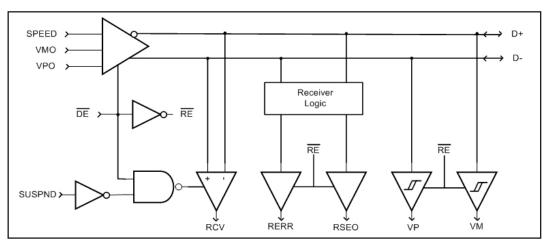

Figure 1. Block Diagram

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, the following specifications apply for Vcc = +3.0V to +3.6V with  $T_{amb} = 0^{\circ}C$  to +70°C.

Typical values apply at Vcc = +3.3V and  $\rm T_{amb}$  = 25°C.

| PARAMETERS                                                | MIN. | TYP.   | MAX.  | UNITS | CONDITIONS                                                                |

|-----------------------------------------------------------|------|--------|-------|-------|---------------------------------------------------------------------------|

| DC Characteristics                                        |      | r.     |       | n.    |                                                                           |

| HIGH level input, V <sub>IH</sub>                         | 2.0  |        |       | V     | Note 2                                                                    |

| LOW level input, $V_{IL}$                                 |      | İ      | 0.8   | V     | Note 2                                                                    |

| HIGH level Driver output<br>impedance, R <sub>DH</sub>    | 28   | 35     | 43    | Ω     | Note 3, Note 4                                                            |

| LOW level Driver output<br>impedance, R <sub>DL</sub>     | 28   | 35     | 43    | Ω     | Note 3, Note 4                                                            |

| D+/D- High output level, V <sub>OH</sub>                  | 2.8  |        |       | V     | $R_{L}$ of 15k to Ground                                                  |

| D+/D- Low output level, V <sub>oL</sub>                   |      |        | 0.3   | V     | R <sub>L</sub> of 1.5k to 3.6V                                            |

| Logic High level output, V <sub>OH</sub>                  | 2.2  | 2.7    |       | V     | Vcc = 3.0V, I <sub>o</sub> = 6mA, Note 2                                  |

| Logic High level output, V <sub>OH</sub>                  | 2.4  |        |       | V     | Vcc = 3.0V, I <sub>o</sub> = 4mA, Note 2                                  |

| Logic High level output, V <sub>oH</sub>                  | 2.8  |        |       | V     | Vcc = 3.0V, I <sub>o</sub> = 200µA, Note 2                                |

| Logic Low level output, V <sub>oL</sub>                   |      | 0.3    | 0.8   | V     | Vcc = 3.0V, I <sub>o</sub> = 6mA, Note 2                                  |

| Logic Low level output, V <sub>OL</sub>                   |      |        | 0.4   | V     | Vcc = 3.0V, I <sub>o</sub> = 4mA, Note 2                                  |

| Logic Low level output, V <sub>oL</sub>                   |      |        | 0.2   | V     | Vcc = 3.0V, I <sub>o</sub> = 200µA, Note 2                                |

| Receiver Differential Input<br>Threshold, V <sub>DI</sub> | -90  | +/-20  | +90   | mV    | Common Mode Voltage 0V to Vcc                                             |

| Receiver Common Mode<br>Range, V <sub>CM</sub>            | 0    |        | Vcc   | V     |                                                                           |

| Quiescent supply current, I <sub>ccq</sub>                |      | 450    | 800   | μA    | $Vcc = 3.6V, V_1 = Vcc \text{ or GND}, I_0 = 0$                           |

| Supply current in SUSPND, $I_{ccs}$                       |      | 0.02   | 1.0   | μA    | Vcc = 3.6V, $V_1$ = Vcc or GND, $I_0$ = 0                                 |

| Active Supply current<br>(Full Speed), I <sub>CCFS</sub>  |      | 6      | 14    | mA    | Vcc = 3.6V, C <sub>L</sub> = 50pF,<br>1,0,1,0input                        |

| Active Supply current<br>(Low Speed), I <sub>CCLS</sub>   |      | 3      | 8     | mA    | Vcc = 3.6V, C <sub>L</sub> = 350pF,<br>1,0,1,0input                       |

| Input Leakage current, I,                                 |      | +/-0.1 | +/-5  | μA    | Vcc = 3.6V, $V_1$ = 5.5V or GND, not for I/O pins                         |

| Tri-State output OFF-state current, I <sub>oz</sub>       |      |        | +/-10 | μA    | $V_{L} = V_{I} \text{ or } V_{IL}, V_{O} = Vcc \text{ or GND},$<br>Note 3 |

| Transceiver Capacitance<br>(D+/D-), C <sub>IN</sub>       |      |        | 20    | pF    |                                                                           |

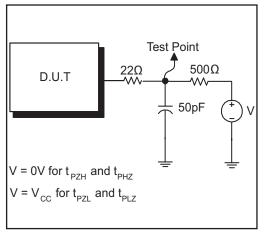

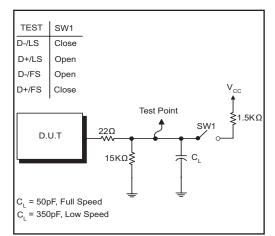

Note 2: All signals except D+ and D-. Note 3: See "Load D+ and D-" diagram for testing details.

Note 4: This value includes a  $22\Omega$  external resistor.

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, the following specifications apply for Vcc = +3.0V to +3.6V with T<sub>amb</sub> = 0°C to +70°C. Typical values apply at Vcc = +3.3V and T<sub>amb</sub> = 25°C.

| PARAMETERS                                            | MIN. | TYP. | MAX. | UNITS | CONDITIONS       |

|-------------------------------------------------------|------|------|------|-------|------------------|

| AC Characteristics                                    |      |      | •    | •     |                  |

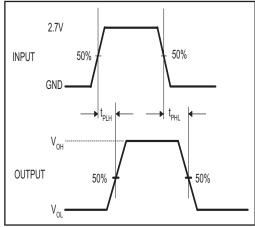

| VPO/VMO to D+/D- Delay, Full Speed, $\rm t_{\rm PLH}$ | 4    | 11   | 15   | ns    | Figure 2, 9      |

| VPO/VMO to D+/D- Delay, Full Speed, $\rm t_{_{PHL}}$  | 4    | 11   | 15   | ns    | Figure 2, 9      |

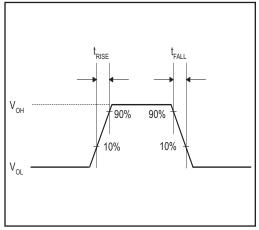

| D+/D- Rise Time, Full Speed, $t_{_{RISE}}$            | 4    | 5.6  | 20   | ns    | Figure 3, 9      |

| D+/D- Fall Time, Full Speed,<br>t <sub>FALL</sub>     | 4    | 5.6  | 20   | ns    | Figure 3, 9      |

| VPO/VMO to D+/D- Delay, Low Speed, $\rm t_{_{PLH}}$   | 30   | 80   | 200  | ns    | Figure 2, 9      |

| VPO/VMO to D+/D- Delay, Low Speed, $\rm t_{\rm PHL}$  | 30   | 80   | 200  | ns    | Figure 2, 9      |

| D+/D- Rise Time, Low Speed,<br>t <sub>RISE</sub>      | 75   | 110  | 250  | ns    | Figure 3, 9      |

| D+/D- Fall Time, Low Speed,<br>t <sub>FALL</sub>      | 75   | 110  | 250  | ns    | Figure 3, 9      |

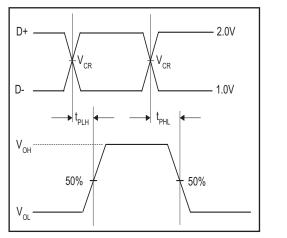

| D+/D- to RCV Delay, t <sub>PLH</sub>                  |      | 8.0  | 16   | ns    | Figure 4, 7      |

| D+/D- to RCV Delay, t <sub>PHL</sub>                  |      | 8.0  | 16   | ns    | Figure 4, 7      |

| D+/D- to VP/VM Delay, t <sub>PLH</sub>                |      | 6.0  | 10   | ns    | Figure 2, 7      |

| D+/D- to VP/VM Delay, t <sub>PHL</sub>                |      | 6.0  | 10   | ns    | Figure 2, 7      |

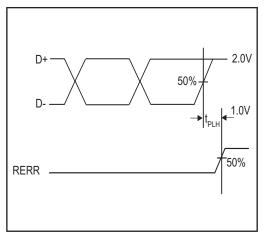

| D+/D- to RERR Delay, t <sub>PLH</sub>                 |      | 14   | 20   | ns    | Figure 7, Note 5 |

| D+/D- to RERR Delay, t <sub>PHL</sub>                 |      | 14   | 20   | ns    | Figure 7, Note 5 |

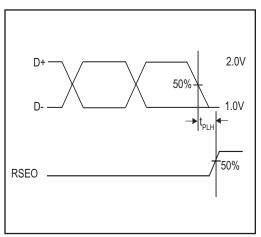

| D+/D- to RSEO Delay, t <sub>PLH</sub>                 |      | 11   | 16   | ns    | Figure 7, Note 5 |

| D+/D- to RSEO Delay, t <sub>PHL</sub>                 |      | 11   | 16   | ns    | Figure 7, Note 5 |

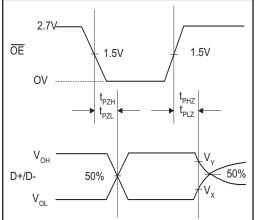

| OE to D+/D-, t <sub>PHZ</sub>                         |      | 11   | 20   | ns    | Figure 5, 8      |

| OE to D+/D-, t <sub>PZH</sub>                         |      | 12   | 20   | ns    | Figure 5, 8      |

| $\overline{OE}$ to D+/D-, t <sub>PLZ</sub>            |      | 11   | 20   | ns    | Figure 5, 8      |

| OE to D+/D-, t <sub>PZL</sub>                         |      | 12   | 20   | ns    | Figure 5, 8      |

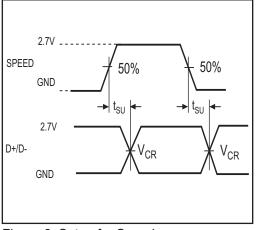

| Setup for SPEED, $t_{sU}$                             | 0    |      |      | ns    | Figure6, 9       |

| D+/D- Crossover point, V <sub>CR</sub>                | 1.3  | ĺ    | 2.0  | V     |                  |

Note 5: Delay defined from midpoint of input to midpoint of output, with other input at static (High or Low).

#### DESCRIPTION

The SP5301 is a half-duplex Universal Serial Bus (USB) differential transceiver that interfaces with the VHDL Serial Interface Engine (SIE) from the USB developer's conference. The SP5301 is designed to allow digital logic to communicate with the physical layer of the Universal Bus.

The USB is a cable bus that supports data exchange between a host computer and a wide range of peripherals. Attached peripherals share USB bandwidth through a host scheduled token based protocol. The USB allows peripherals to be atached, configured, used, and detached while the host and other peripherals are in operation. This is referred to as dynamic, or hot, attachment and removal. USB attributes include lower costs, hot plugand-play with dynamic attach-detach capabilities, ease of design and use, multiple peripherals, guaranteed latency, and guaranteed bandwidth.

The USB is specified to be an industry standard extension to the PC architecture with a focus on Computer Telephony Integration (CTI), consumer, and productivity applications. The architecture of the USB protocol can ease the expansion of PC peripherals, provide a low-cost solution that supports tranfer rates up to 12Mbps, and can fully support real-time data for voice, audio, and compressed video.

The USB protocol can provide protocol flexibility for mixed-mode isochronous data transfers and asynchrounous messaging. Guaranteed bandwidth and low latencies are appropriate for many telephony and audio applications. A 12Mbps bus covers the mid-speed and low-speed data ranges. Typically, mid-speed data types are isochronous and low-speed data comes from interactive devices. Isochronous communication can only be used by full speed devices.

### THEORY OF OPERATION

The USB protocol can support multiple connections for up to 127 physical devices composed of many diverse functions. This makes the SP5301 an ideal solution for multidrop applications. This lower protocol overhead results in high bus utilization. An isochronous workload may utilize the entire USB bus bandwidth. The USB protocol reflects a robust capability of dynamic insertion and removal of devices identified in user perceived real-time. This PC plug and play quality preserves the marketable synergy with the PC industry, being a simple protocol to implement and integrate into existing operating systems.

The SP5301 contains a differential driver and a differential receiver in a half-duplex configuration. The driver is enabled by the OE pin. If OE is asserted LOW, the driver is active and the D- and D+ pins drive USB signals. The differential receiver is also controlled by the OE pin. If OE is HIGH, while SUSPEND is LOW, the receiver is active and the driver is in tri-state. In this receive mode, the D- and D+ pins are now receiving USB signals.

The typical driver output voltage swing for D- and D+ of the SP5301 will be less than +0.3V for the LOW state and greater than +2.8V for the HIGH state.

The SP5301 is a USB differential interface with very high receiver input sensitivity. This makes data virtually immune to noise on the USB pipeline. The ±90mV minimum receiver input sensitivity of the SP5301 ensures recovery of even severely attenuated signals.

The SP5301 incorporates a receive error circuit. This error circuit outputs CMOS signals on the receive error pin (RERR) and the receive single ended zero pin (RSE0) under specific conditions from the USB bus. When  $\overline{OE}$  is asserted LOW, it enables the USB driver to transmit data on the D+ and D- output pins. The receive error circuit is disabled in this condition and both RERR and RSE0 are forced low. The receive error circuit is activated in receive mode when OE is HIGH. The receive error circuit will signal an error state when both D+ and D- are HIGH by forcing RERR HIGH. The receiver error circuit will signal a single ended zero when both D+ and D- are LOW by forcing RSE0 HIGH. A single ended zero is a valid state and is used to signal an end of packet (EOP) in signal transmission. (CAUTION: Since both RERR and RSE0 are CMOS outputs, care must be taken to ensure that RERR and RSE0 are NOT connected to VCC or GND.)

The SP5301 has a suspend input pin (SUSPND) which enables a low power state while the USB bus is inactive. When SUSPND is asserted HIGH or SP5301 is in transmit mode (OE is LOW), the receive data pin (RCV) will be forced LOW.

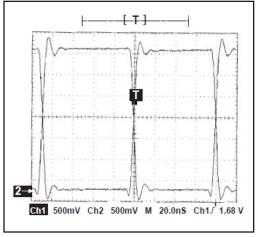

Chi 500mV Ch2 500mV M 250nS Ch1/ 1.68 V

Waveform 1. D+/D- Transmit Mode, low speed

The SP5301 can transmit and receive serial data at both full speed, 12Mbps, and at low speed, 1.5Mbps, data rates. At full speed, the active supply current of the SP5301 is 6mA. In the suspend state, the supply current is typically 20nA.

Full speed USB applications include ISDN, PBX, POTS, sampled analog devices, audio, printers, and telephony designs. Low speed USB applications include locator devices, keyboards, mouse, tablets, light pens, stylus, game peripherals, virtual reality peripherals, and monitor configurations. The USB protocol provides full support for the real-time data for voice, audio, and compressed video. The SP5301 is specifically geared towards low-cost USB solutions for the PC peripheral markets

Waveforms 1 and 2 below show device behavior in transmit mode, at both low and full speed, with the D+/D- pins driving the load specified in figure 9.

Waveform 2. D+/D- Transmit Mode, full speed

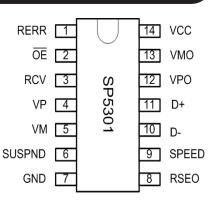

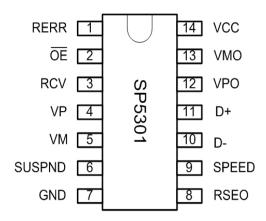

#### **PIN ASSIGNMENTS**

Pin 1 — RERR — Receive Error. This CMOS level output pin is forced HIGH when both D+ and D- are HIGH to signal an error state. **CAUTION**: Since RERR is a CMOS output, care must be taken to ensure that RERR is **NOT** connected to VCC or GND.

Pin 2 —  $\overline{\text{OE}}$  — Output Enable Not. When asserted LOW, this input pin enables the driver to transmit data on the bus. When HIGH, the receiver is active and the driver outputs are in tri-state.

Pin 3 — RCV — Receive data. This is a CMOS level output pin from D+ and D-, typically connected to the inputs of the USB Serial Interface Engine (SIE).

Pin 4, 5 — VP, VM — Gated version of D+ and D-. Used to detect single ended zero (SEO), error conditions, and interconnect speed. These pins have CMOS level outputs.

| VP | VM | RESULT     |

|----|----|------------|

| 0  | 0  | SEO        |

| 0  | 1  | Low Speed  |

| 1  | 0  | Full Speed |

| 1  | 1  | Error      |

Pin 6 — SUSPND — Suspend. This input pin provides a low power state for the SP5301 while the USB bus is inactive. While the SUSPND pin is asserted HIGH, it will drive RCV pin LOW.

Pin 7 — GND — Ground.

Pin 8 — RSEO — Receive Single Ended Zero. This CMOS level output pin is forced HIGH when both D+ and D- are LOW to signal the end of packet (EOP) in signal transmission. **CAUTION**: Since RSEO is a CMOS output, care must be taken to ensure that RSEO is **NOT** connected to VCC or GND.

Pin 9 — SPEED — Speed. Edge rate control. This input pin determines edge rates, where a logic HIGH designates edge rates for "full speed" and logic LOW designates edge rates for "low speed."

Pin 10, 11 — D-, D+ — Data-, Data+. These differential data bus I/O pins conform to the Universal Serial Bus standard.

Pin 12, 13 — VPO, VMO — These are the logic inputs to the differential driver, typically connected to the outputs of the serial Interface Engine (SIE).

| VPO | VMO | RESULT     |

|-----|-----|------------|

| 0   | 0   | SEO        |

| 0   | 1   | Logic Low  |

| 1   | 0   | Logic High |

| 1   | 1   | Undefined  |

Pin 14 — Vcc — +3.0V to +3.6V power supply

#### AC WAVEFORMS

Figure 2. D+/D- to VP/VM or VPO/VMO to D+/D-

Figure 3. Rise and Fall Times

Figure 4. D+/D- to RCV

Figure 5. OE to D+/D-

NOTE:  $V_x = V_{OL} + 0.3V$ ,  $V_y = V_{OH} - 0.3V$ ,  $V_{CC} \ge +3.0V$ ,  $V_{OL}$  and  $V_{OH}$  are the typical output voltage drops that occur with the output load.

## AC WAVEFORMS (continued)

Figure 6. Setup for Speed

Figure 8. Load for Enable and Disable Times

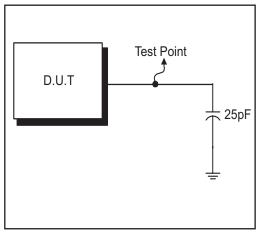

Figure 7. Load for VM, VP, RERR, RSEO and RCV

Figure 9. Load for D+/D-

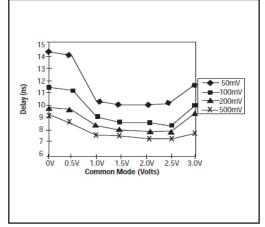

Figure 10. Receiver Delay VS. Common Mode Voltage (with peak to peak overdrive voltage as a parameter)

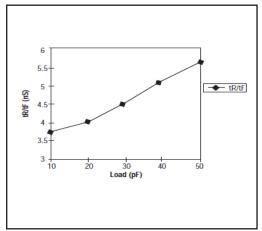

Figure 11. Transmitter Rise and Fall Time VS. Capacitive load (full speed)

Figure 12. D+/D- to RERR Delay

Figure 13. D+/D- to RSEO Delay

#### **ORDERING INFORMATION**

| Model         | Temperature Range | Package Types |

|---------------|-------------------|---------------|

| SP5301CY-L    | 0°C to +70°C      | 14-pin TSSOP  |

| SP5301CY-L/TR | 0°C to +70°C      | 14-pin TSSOP  |

Note: /TR = Tape and Reel

#### **REVISION HISTORY**

| DATE     | REVISION | DESCRIPTION                                                                                           |

|----------|----------|-------------------------------------------------------------------------------------------------------|

|          |          | Legacy Sipex Datasheet                                                                                |

| 08/17/10 | 1.0.0    | Convert to Exar Format. Update ordering information as a result of discontinued NSOIC package option. |

#### Notice

EXAR Corporation reserves the right to make changes to any products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no representation that the circuits are free of patent infringement. Charts and schedules contained herein are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writiting, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2010 EXAR Corporation

Datasheet August 2010

Send your Interface technical inquiry with technical details to: uarttechsupport@exar.com

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.