# AC-DC Controller for Dimmable LED Lighting

#### **Features**

- AC offline input range from 80 to 277 VAC

- Up to 25W output power range

- Intelligent wall dimmer detection:

- □ Leading edge (R, RL) dimmers

- ☐ Trailing edge (RC, RLC) dimmers

- □ No dimmer

- Wide dimming range from 2 to 100%

- Resonant control to achieve high efficiency (85% without dimmer)

- Meets harmonic requirement with high power factor (0.7 without dimmer)

- Primary-side sensing eliminates opto-isolators

- Tight LED current regulation (typically < ± 2.5%)

- Low startup current (typically 10 μA)

- Low startup time (typically 0.5s with active startup)

- Multiple protection features:

- Output overvoltage protection (OOVP)

- □ Output short circuit protection (OSCP)

- Overtemperature protection (OTP)

- □ Current-sense resistor short protection (CSSP)

- Peak current limit protection (PCLP)

- □ Single-point fault protection

- Applications:

- □ Dimmable offline LED driver

- ☐ Dimmable LED replacement lamps

- □ Dimmable LED luminaires

#### Description

The CY8CLEDAC02 is a high performance offline LED driver, designed to interface directly with most conventional phase cut based wall dimmers. The device uses proprietary digital control technology to provide automatic detection of dimmer type (leading or trailing edge). It automatically generates dimming signals for LED loads and has the ability to dim down to 2%. It modulates LED brightness using a linear dimming scheme and switches to a PWM based dimming scheme for output current levels lower than 20% of the full load current. In PWM mode optimized dimming frequencies in the range of 900 Hz result in zero visible flicker.

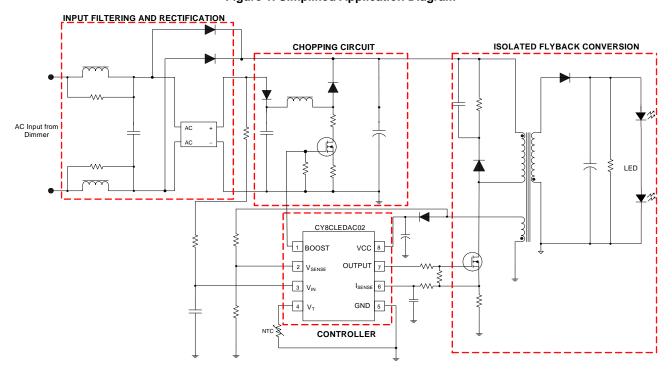

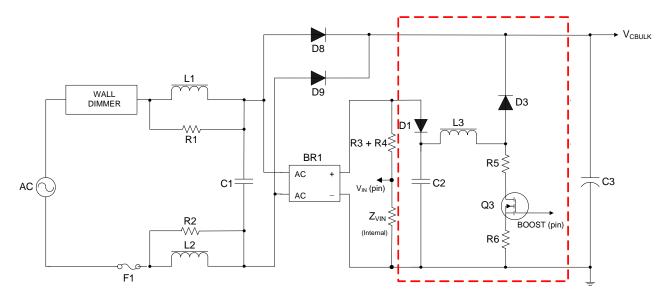

At the heart of a CY8CLEDAC02 based system is the chopping circuit which provides the load necessary to enable correct wall dimmer operation. It also improves PF when there is no dimmer on the line.

The devices' proprietary primary side sensing enables tight LED current regulation and eliminates the need for secondary feedback circuitry. No opto-couplers are necessary to meet UL isolation requirements; enabling flyback conversion with automatic isolation.

The CY8CLEDAC02 operates in quasi-resonant mode to achieve high efficiency. This mode of operation helps minimize external component count and simplifies EMI design, lowering the total bill of material cost.

The device's cycle-by-cycle adaptive digital regulation uses critical discontinuous conduction mode (CDCM) when driving LED loads. The control algorithm for cycle-by-cycle regulation has internal compensation for guaranteed system phase and gain margins; requiring no external components for loop compensation.

The CY8CLEDAC02 has full featured circuit protection not normally available with other primary-side control solutions. The built-in protection includes output overvoltage protection (OOVP), output short circuit protection (OSCP), overtemperature protection (OTP), current-sense resistor short protection (CSSP), and peak current limit protection (PCLP). It also enables automatic LED brightness adjustment to compensate for temperature drift by simply connecting a NTC resistor to the  $V_T$  pin.

Revised March 29, 2010

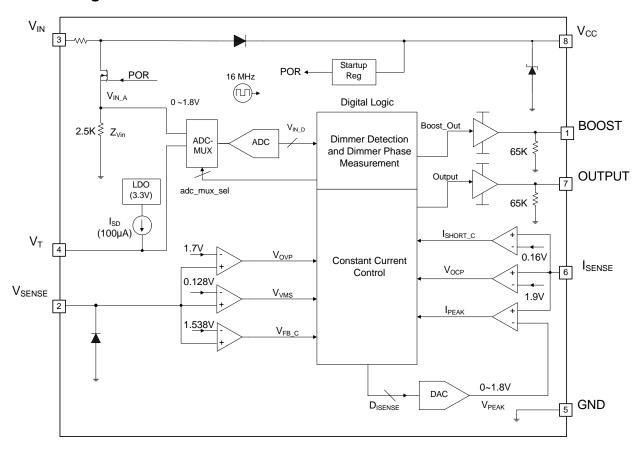

## **Logic Block Diagram**

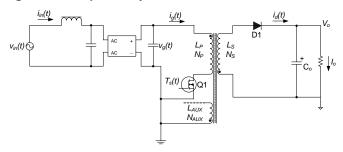

Figure 1. Simplified Application Diagram

## CY8CLEDAC02

## Contents

| eatures                               | 1  |

|---------------------------------------|----|

| Description                           | 1  |

| ogic Block Diagram                    | 2  |

| Contents                              | 3  |

| Pin Information                       | 4  |

| Functional Description                | 5  |

| Overview                              |    |

| Device Startup                        | 5  |

| Dimmer Detection                      | 6  |

| Dimmer Tracking and Phase Measurement | 7  |

| Protection Features                   | 9  |

| Understanding Primary Feedback 1      | 10 |

| Valley Mode Switching 1               | 11 |

| Electrical Specifications 1           | 12 |

| Absolute Maximum Ratings 1            |    |

| Electrical Characteristics              | 13 |

|-----------------------------------------|----|

| Typical Application Diagram             | 14 |

| Typical Performance Characteristics     | 15 |

| Performance Information                 | 16 |

| Ordering Code Definitions               | 17 |

| Packaging Information                   | 18 |

| Physical Package Dimensions             | 18 |

| Document History Page                   | 19 |

| Sales, Solutions, and Legal Information | 19 |

| Worldwide Sales and Design Support      | 19 |

| Products                                | 19 |

| PSoC Solutions                          | 19 |

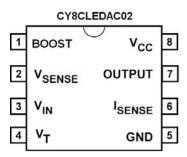

## **Pin Information**

| Pin No. | Name               | Туре         | Pin Description                                                                                          |

|---------|--------------------|--------------|----------------------------------------------------------------------------------------------------------|

| 1       | BOOST              | Output       | Gate driver for driving the MOSFET switch in the chopping circuit                                        |

| 2       | V <sub>SENSE</sub> | Analog Input | Auxiliary voltage sense (used for primary regulation and zero voltage switching)                         |

| 3       | V <sub>IN</sub>    | Analog Input | Rectified AC line voltage sense, also used for device startup                                            |

| 4       | $V_{T}$            | Analog Input | Used for temperature compensation and overtemperature protection, also used as an external shut down pin |

| 5       | GND                | Ground       | Ground                                                                                                   |

| 6       | I <sub>SENSE</sub> | Analog Input | Primary current sense. Used for cycle-by-cycle peak-current control and limiting                         |

| 7       | OUTPUT             | Output       | Gate driver for main MOSFET switch                                                                       |

| 8       | V <sub>CC</sub>    | Power Input  | Power supply for control logic and voltage sense for power-on reset circuitry                            |

### **Functional Description**

#### Overview

The digital logic block is the main control block. All the other blocks are either inputs or outputs for the digital logic block.

The digital logic block receives signals to determine the input voltage ( $V_{IN}$ ), output voltage ( $V_{SENSE}$ ), temperature ( $V_{T}$ ), and output current ( $I_{SENSE}$ ). It has three output controls;  $D_{ISENSE}$  (current control), Output (flyback MOSFET gate drive control), and Boost\_Out (chopper MOSFET gate drive control).

The bias winding of the transformer provides voltage feedback to the controller for regulation and safety features. The external voltage sense resistors (not shown) determine the feedback signal to the  $V_{\mbox{\footnotesize SENSE}}$  pin of the controller. The  $V_{\mbox{\footnotesize SENSE}}$  pin connects to circuitry composed of three comparators:  $V_{OVP}$  (output overvoltage protection),  $V_{VMS}$  (voltage valley mode switch), and  $V_{FB\_C}$  (voltage feedback from coil). When the V<sub>SENSE</sub> voltage exceeds V<sub>SENSE(MAX)</sub> (1.7V) the control block detects an overvoltage condition, it will enter a shutdown mode and wait for POR to re-initialize the system. V<sub>VMS</sub> is monitored by the control block to determine when the power in the flyback MOSFET is at a minimum or in a 'valley'. When the V<sub>SENSE</sub> voltage goes below the 0.128V threshold the control block starts monitoring valleys and will start the next cycle at the 'valley' for maximum efficiency and minimum switching EMI. For normal operation, the  $V_{SENSE}$  voltage should be set below  $V_{SENSE(NOM)}$ (1.538V). When the  $V_{SENSE}$  voltage exceeds  $V_{SENSE(NOM)}$  the controller senses an output overvoltage and tries to maintain a constant output voltage. This is an intermediate mode where the controller starts reacting to a problem with the output voltage. However, an OVP fault will only trigger if V<sub>SENSE</sub> voltage exceeds V<sub>SENSE(MAX)</sub>.

The I<sub>SENSE</sub> pin connects to circuitry composed of three comparators: I<sub>PEAK</sub>, V<sub>OCP</sub>, and I<sub>SHORT\_C</sub>. These three blocks work together for soft start control and peak current detection, overcurrent protection, and sense resistor short protection respectively. The DAC  $V_{PEAK}$  controls soft start; minimizing stress associated with system startup. The  $I_{PEAK}$  comparator monitors the voltage at the I<sub>SENSE</sub> pin. The voltage is generated by current flowing through a small external resistor (RISENSE not shown). When the  $I_{SENSE}$  voltage reaches  $V_{REG-TH}$  (1.8V), the I<sub>PEAK</sub> comparator asserts a high to the control block. The control block will shut off the output and wait for V<sub>VMS</sub> detection; then start the next cycle. The V<sub>OCP</sub> comparator provides primary side overcurrent protection. When the voltage on I<sub>SENSE</sub> reaches V<sub>PEAK</sub> (1.9V), the V<sub>OCP</sub> signal gets asserted. When overcurrent is detected, the control block will enter a shutdown mode and reset the system. When the I<sub>SENSE</sub> voltage reaches V<sub>RSNS</sub> (0.16V), a sense resistor short circuit fault is detected and the control block will enter a shutdown mode and reset all the digital

The Output signal connects to the gate driver block for the OUTPUT pin that, in turn, connects to the flyback MOSFET gate pin (not shown). The OUTPUT pin is a digital control pin that switches between high level (approximately  $V_{CC}$ ) and low level (approximately ground). The duration for high ( $t_{ON}$ ) and low

(t<sub>OFF</sub>) of the Gate Driver is a function of the control block operating upon its inputs:  $V_{IN}t_{ON}$ ,  $V_{FB}$ ,  $V_{VMS}$ ,  $V_{T}$ ,  $I_{PEAK}$ ,  $V_{OCP}$ , and  $V_{CC}$ .

The Boost\_Out signal connects to the gate driver block for the BOOST pin that, in turn, connects to the chopper MOSFET gate pin (not shown). The BOOST pin is again a digital control pin that switches between high level (approximately  $V_{\rm CC}$ ) and low level (approximately ground). The BOOST pin timing is internally controlled and depends on the mode of operation for the IC (that is, no dimmer, trailing edge dimmer, or leading edge dimmer mode).

The  $V_T$  pin connects to a current source ( $I_{SD}$ ), generated by an internal LDO, and an analog to digital converter. This pin can be used for OTP along with automatic LED brightness adjustment to compensate for temperature drift. This can be achieved by simply connecting the  $V_T$  pin to an external NTC component (not shown). The current source causes a voltage to develop at the  $V_T$  pin which is sampled once every AC half cycle by the ADC. If the voltage is between 0.5 to 2V, the controller operates normally. For a voltage range 0.5V to 0.3V, the LED intensity is linearly dimmed. At 0.3V the LEDs are dimmed to 10%. From 0.3V to 0.1V, the LED intensity stays at 10% and below 0.1V ( $V_{SH-TH}$ ), the controller will trigger a fault, enter shutdown mode, and reset all the digital logic.

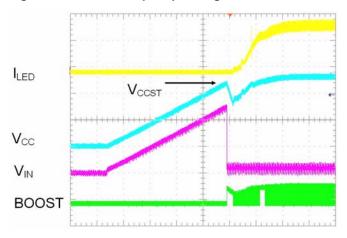

#### **Device Startup**

Before startup,  $V_{IN}$  charges up the  $V_{CC}$  capacitor through the internal diode between  $V_{IN}$  and  $V_{CC}$  (see "Logic Block Diagram" on page 2). When the voltage at  $V_{CC}$  rises above the startup threshold  $V_{CCST}$ , the control logic is enabled.

In the first four AC half cycles after startup, the BOOST pin is held high (see Figure 2 on page 6). During these half cycles the dimmer type is detected and the AC line period is measured. Following this, the controller enters an intermediate state and waits for the output voltage to ramp up. When the output voltage is higher than the forward voltage for the LED string, the controller enters constant current mode.

An adaptive soft start control algorithm is applied at startup, during which the initial output pulses are small and gradually get larger until the full pulse width is achieved. The peak current is limited cycle-by-cycle by I<sub>PEAK</sub> comparator.

If at any time the  $V_{CC}$  voltage drops below the  $V_{CCUVL}$  threshold, all the digital logic is reset. At this time the internal  $V_{IN}$  switch turns off allowing the  $V_{CC}$  capacitor to charge for a fresh startup.

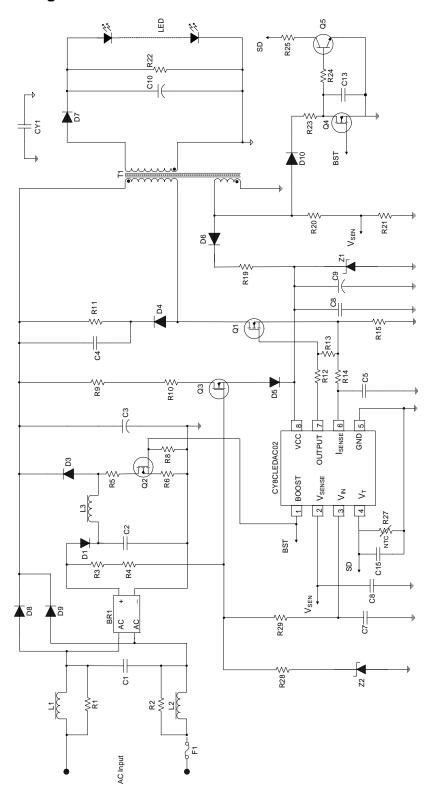

If a faster startup is required, then an external active startup scheme can be used. Components R10, R11, Q3, and D5 enable active startup as illustrated in the "Typical Application Diagram" on page 14. Q3, a depletion type MOSFET, is initially on before startup. The  $V_{CC}$  capacitor C8 charges a lot quicker as the resistors R10 and R11 can be made much smaller than R3 and R4 lowering the overall charging resistance. When  $V_{CC}$  rises above  $V_{CCST}$ , the internal control logic gets enabled pulling the  $V_{IN}$  node low. The gate to source voltage across Q3 becomes negative, thus turning Q3 off. This technique substantially reduces startup time.

Figure 2. Device Startup Sequencing

#### **Dimmer Detection**

Intelligent Wall Dimmer detection includes automatically detecting presence or absence of a dimmer and, if present, detecting the dimmer type (leading or trailing edge).

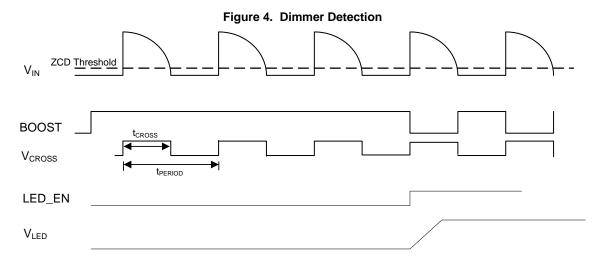

Dimmer detection or discovery takes place during the first four AC half cycles after startup. During this phase the BOOST pin remains high, placing a purely resistive load across the dimmer. As wall dimmers are designed to work with resistive loads such

as an incandescent lamp, loading the dimmer with a purely resistive load enables accurate dimmer detection.

The operation is broken into two stages. In the first stage, the controller simply determines whether a dimmer is present. If a dimmer is not detected, the dimmer type is set to 'no dimmer'. If a dimmer is detected, then in the next stage the dimmer type (leading or trailing edge) is determined.

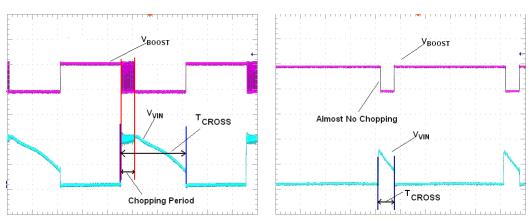

The presence or absence of a dimmer is determined by monitoring how long the  $V_{IN}$  voltage stays below a zero-cross detect (ZCD) threshold. This threshold is determined by the controller using the peak of line and half line period measurements. An internal digital signal,  $V_{CROSS}$ , is generated which tracks the  $V_{IN}$  signal and determines the duration ( $t_{PERIOD}-t_{CROSS}$ ) for which  $V_{IN}$  is below the ZCD threshold (see Figure 4 on page 7). This detection scheme is based on the fact that  $V_{IN}$  will remain below the ZCD threshold for a much longer duration in a single AC half cycle when a dimmer is present. In most cases  $V_{IN}$  is below the ZCD threshold for longer due to phase cut on the line. In cases when the dimmer does not exhibit any phase cut (at maximum setting) the duration is longer due to delays associated with dimmer operation.

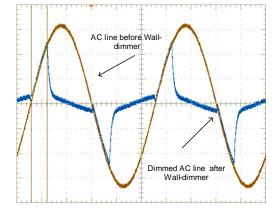

If a dimmer is detected, then the  $V_{\rm IN}$  pin voltage is filtered and differentiated to identify the largest positive and negative slopes in the AC half cycle. If the positive (rising) slope is greater than 1.5 times the negative (falling) slope, then a leading edge dimmer must be present. If not, a trailing edge dimmer must be present.

AC line before Wall-dimmer

Dimmed AC line after Wall-dimmer

Figure 3. AC Line Waveforms with Leading Edge (left) and Trailing Edge (right) Dimmers

#### **Dimmer Tracking and Phase Measurement**

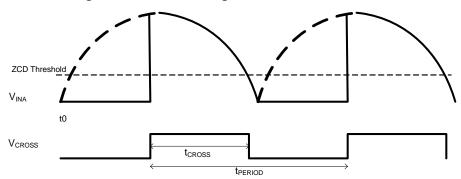

Dimmer detection and tracking algorithms depend on accurate measurement of the  $V_{\rm IN}$  period. The period is measured during the second cycle of the dimmer discovery process and is then latched for use. Using the measured  $V_{\rm IN}$  period in subsequent calculations rather than a constant value enables automatic 50 or 60 Hz operation.

The phase measurement algorithm uses an internal counter that starts counting when the rising threshold on  $V_{IN}$  is exceeded and counts input voltage samples until the voltage is above the threshold. The counter is synchronized with the measured  $V_{IN}$  period and is restarted on every rising threshold (as shown in Figure 5).

The dimmer phase is calculated as:

#### **Equation 1**

$$D_{PHASE} = \frac{t_{CROSS}}{t_{PERIOD}}$$

The calculated  $D_{PHASE}$  is then used to generate a signal  $D_{RATIO}.$  When  $D_{PHASE}$  is less than 0.2,  $D_{RATIO}$  is set to 0.02 and when

$D_{PHASE}$  is greater than 0.8,  $D_{RATIO}$  is set to 1.0. For all other cases  $D_{RATIO}$  is set using the following equation:

#### **Equation 2**

$$D_{RATIO} = D_{PHASE} \times K1 - K2$$

where K1 and K2 are constants with values 1.63 and 0.3 respectively.

The output power to the LED load is modulated by  $D_{RATIO}$ . When  $D_{RATIO}$  is 1, 100% power is provided to the LED load, and when  $D_{RATIO}$  of 0.1, 10% power is provided to the LED load.

The voltage at the  $I_{SENSE}$  pin  $V_{ISENSE}$ , which modulates the output LED current can be set at a nominal value and modulated using the following equation:

#### **Equation 3**

$$V_{ISENSE} = V_{I SENSE} (NOM) \times D_{RATIO}$$

This equation provides a mapping from the measured dimmer phase to actual light output.

Figure 5. Dimmer Tracking and Phase Measurement

#### **Chopping Operation**

The chopping circuit provides four key functions:

- At startup, it provides a low impedance load on the wall dimmer enabling the type of dimmer (none, leading edge, or trailing edge) to be determined.

- Each cycle intelligently provides a low impedance load to:

- ☐ Enable accurate determination of mains zero crossing points.

- Meet triac trigger current and latch current requirements for triac based (leading edge) dimmers.

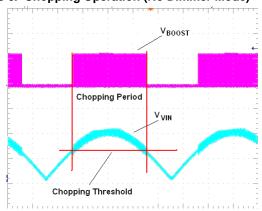

- Improves Power Factor

- Minimizes mains cycle peak current for triac based (leading edge) dimmers by boosting energy into the bulk capacitor.

The chopping circuit is shown in Figure 7. When Q3 is driven with short on pulses, the circuit operates as a boost converter. When Q3 turns on, the chopping inductor L3 stores energy. When Q3 turns off, this energy is released to capacitor C3 through diode D3. Source resistor R6 is used to limit the current in the chopper path to optimize the efficiency of the circuit. A dithering algorithm is used to control the period for Q3 to minimize EMI generated by the mainly discontinuous operation of the boost circuit. The voltage on  $Z_{\text{VIN}}$  is the scaled rectified mains voltage, a voltage only available internal to the device.

During the chopping period, the average current in L3 is in phase with and proportional to the input mains voltage inherently generating high power factor.

If the circuit determines it is connected to a dimmer, Q3 is held on while the mains voltage in is low. This provides a load on the dimmer enabling the internal circuitry of the dimmer to reset correctly for each half cycle. For leading edge dimmers, Q3 is held on for a significant time after the triac in the dimmer fires each half cycle. During this period L3 will saturate and R6 provides the current necessary for the triac latch current to be reached. For trailing edge dimmers, Q3 is held high after the trailing edge. This load forces the line to quickly fall to zero when

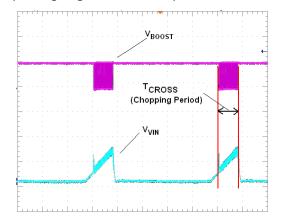

the dimmer turns off, enabling accurate detection of the dimmer on time.

D8 and D9 ensure C3 is charged to peak voltage output from the dimmer. This maximizes the voltage on C3 each half cycle, minimizing the in rush current when the triac fires on the next half cycle.

The chopper operates in three different modes as follows:

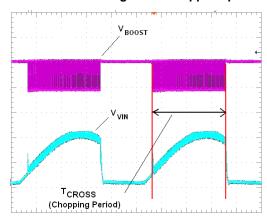

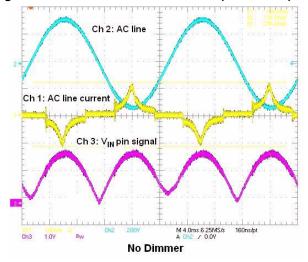

- No dimmer: Chopper operates when the internal voltage at Z<sub>VIN</sub> is above a pre-defined chopping threshold. The chopper remains off otherwise.(see Figure 6)

- Leading edge dimmer mode: The chopping period is defined as the percentage of the dimming period (T<sub>CROSS</sub>). The chopper FET remains hard on during the zero crossing section on V<sub>IN</sub>.(see Figure 8)

- Trailing edge dimmer mode: Chopping circuit is active across the entire dimming period (T<sub>CROSS</sub>). The chopper FET remains hard on otherwise (see Figure 9).

Figure 6. Chopping Operation (No Dimmer Mode)

Figure 7. Chopper Circuit

Figure 8. Chopper Operation (Leading Edge Dimmer Mode)

Figure 9. Chopper Operation (Trailing Edge Dimmer Mode)

#### **Protection Features**

The CY8CLEDAC02 has full featured circuit protection not normally available with other primary-side control solutions.

The built-in protection features include output overvoltage protection (OOVP), output short circuit protection (OSCP), peak current limit protection (PCLP), current-sense resistor short protection (CSSP), and overtemperature protection (OTP).

In an event a protection is triggered (except PCLP and OOVP),  $V_{CC}$  discharges below  $V_{CCUVL}$  and causes the digital logic to reset. The controller now initiates a new soft start cycle and continues to attempt start-up. It is unable to start-up until the fault condition is removed. PCLP does not trigger a shutdown. In case of OOVP the IC stays latched and cannot perform a reset unless the  $V_{CC}$  voltage drops approximately 1-2V below  $V_{CCUVL}$  threshold.

#### Output Overvoltage Protection (OOVP)

The CY8CLEDAC02 includes a function that protects against an output overvoltage. The output voltage is monitored by the  $V_{\rm SENSE}$  pin. The protection is triggered if the voltage at this pin exceeds the overvoltage threshold  $V_{\rm SENSE(MAX)}$ .

#### Output Short Circuit Protection (OSCP)

The CY8CLEDAC02 includes a function that protects against an output short circuit. The output voltage is monitored by the  $V_{\text{SENSE}}$  pin. The protection is triggered if the voltage at this pin is below 0.22V.

#### Overtemperature Protection (OTP)

The  $V_T$  pin along with an external NTC provides overtemperature protection. Having an internal current source to the pin allows for sensing the voltage across the NTC. The voltage across the pin is sampled once every AC half cycle and the protection mode is triggered if it reaches the  $V_T$  shutdown threshold ( $V_{SDTH}$ ).

#### Current Sense Resistor Short Protection (CSSP)

If the  $I_{SENSE}$  sense resistor is shorted, there is a potential danger of an overcurrent condition not being detected. The CY8CLEDAC02 has a separate circuit to detect this fault. This protection mode is triggered if the  $I_{SENSE}$  voltage is below  $I_{SENSE}$  short protection reference ( $V_{RSNS}$ ).

#### Peak Current Limit protection (PCLP)

The  $I_{\rm SENSE}$  pin of the CY8CLEDAC02 monitors the primary peak current. This enables cycle-by-cycle peak current control and limiting. When the  $I_{\rm SENSE}$  voltage is greater than the overcurrent limit threshold  $V_{\rm OCP}$ , an overcurrent condition is detected and the IC immediately turns off the MOSFET driver. During the next switching cycle, the driver sends out a regular switching pulse and turns off again if the OCP threshold is still reached. Normal switching resumes if the fault is removed and the OCP threshold is not reached.

#### Single Point Fault Protection

The CY8CLEDAC02 can detect a short on any of the following pins  $V_{IN}$ ,  $I_{SENSE}$ ,  $V_{SENSE}$ ,  $V_{CC}$ , OUTPUT, and  $V_{T}$ . Therefore any single point fault is protected against.

#### **Understanding Primary Feedback**

Figure 10 illustrates a simplified flyback converter. When the switch Q1 conducts during  $t_{ON}(t)$ , the current  $i_g(t)$  is directly drawn from rectified sinusoid  $v_g(t)$ . The energy  $E_g(t)$  is stored in the magnetizing inductance  $L_{\rm P}$ . The rectifying diode D1 is reverse biased and the load current  $I_{\rm O}$  is supplied by the secondary capacitor  $C_{\rm O}$ . When Q1 turns off, D1 conducts and the stored energy  $E_g(t)$  is delivered to the output.

Figure 10. Simplified Flyback Converter

To tightly regulate output current, information about the load current needs to be accurately sensed. To achieve CC regulation, this information can be derived indirectly by sensing the primary current.

To detect faults with output voltage, information about the output voltage and load current needs to be accurately sensed. In the DCM flyback converter, this information can be read through the auxiliary winding.

During the Q1 on time, the load current is supplied from the output filter capacitor  $C_O$ . The voltage across  $L_P$  is  $v_g(t)$ , assuming the voltage dropped across Q1 is zero. The current in Q1 ramps up linearly at a rate of:

#### **Equation 4**

$$\frac{di_g(t)}{dt} = \frac{v_g(t)}{L_p}$$

At the end of on time, the current has ramped up to:

#### **Equation 5**

$$i_{g_peak}(t) = \frac{v_g(t) \times t_{ON}}{L_p}$$

This current represents a stored energy of:

#### **Equation 6**

$$E_{g} = \frac{L_{P}}{2} \times i_{g_{-peak}}(t)^{2}$$

When Q1 turns off,  $i_g(t)$  in L<sub>P</sub> forces a reversal of polarities on all windings. Ignoring the commutation time caused by the leakage inductance L<sub>KP</sub> at the instant of turn-off, the primary current transfers to the secondary at a peak amplitude of:

#### **Equation 7**

$$i_{d}(t) = \frac{N_{P}}{N_{s}} \times i_{g_{peak}}(t)$$

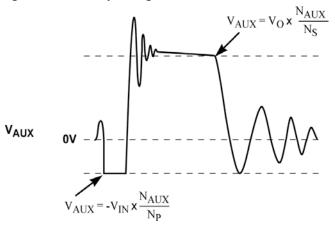

Assuming the secondary winding is master and the auxiliary winding is slave, the auxiliary voltage is given by:

#### **Equation 8**

$$V_{AUX} = \frac{N_{AUX}}{N_S} (V_O + \Delta V)$$

and reflects the output voltage as shown in Figure 11.

Figure 11. Auxiliary Voltage Waveforms

The voltage at the load differs from the secondary voltage by a diode drop and IR losses. The diode drop is a function of current, as are IR losses. Thus, if the secondary voltage is always read at a constant secondary current, the difference between the output voltage and the secondary voltage is a fixed  $\Delta V$ . Further, if the voltage can be read when the secondary current is small; for example, at the knee of the auxiliary waveform (see Figure 11), then  $\Delta V$  is also small. With the CY8CLEDAC02,  $\Delta V$  can be ignored.

The real time waveform analyzer in the CY8CLEDAC02 reads the auxiliary waveform information cycle by cycle. The part then generates a feedback voltage  $V_{FB\_C}$ . The  $V_{FB\_C}$  signal precisely represents the output voltage and is used to sense the output voltage.

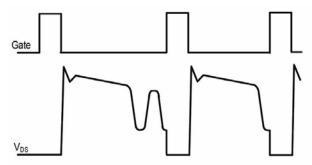

#### **Valley Mode Switching**

To reduce EMI and switching losses in the MOSFET, the CY8CLEDAC02 employs valley mode switching by switching at the lowest MOSFET  $V_{DS}$  (see Figure 12). It detects valleys in the MOSFET drain voltage indirectly through the  $V_{SENSE}$  pin. This voltage is provided by the auxiliary winding of the flyback transformer and represents a copy of the secondary side characteristics (see Figure 11).

Figure 12. Valley Mode Switching

Turning on at the lowest  $V_{DS}$  generates lowest dV/dt; thus valley mode switching can also reduce EMI. To limit the switching frequency range, the CY8CLEDAC02 can skip valleys (as shown in the first cycle in Figure 12) when the switching frequency becomes too high.

## **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8CLEDAC02. For the most up to date electrical specifications, confirm that you have the most recent data sheet by going to the web at <a href="http://www.cypress.com/powerpsoc">http://www.cypress.com/powerpsoc</a>. Specifications are valid for -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and T<sub>J</sub>  $\leq$  125°C, except where noted. Table 1 lists the units of measure that are used in this section.

Table 1. Units of Measure

| Symbol | Unit of Measure              | Symbol | Unit of Measure             | Symbol | Unit of Measure |

|--------|------------------------------|--------|-----------------------------|--------|-----------------|

| °C     | degrees Celsius              | Kbit   | 1024 bits                   | mA     | milliampere     |

| dB     | decibels                     | KHz    | kilohertz                   | ms     | millisecond     |

| Hz     | Hertz                        | ΚΩ     | kilohms                     | mV     | millivolts      |

| pp     | peak-to-peak                 | MHz    | megahertz                   | mA     | milliwatts      |

| σ      | sigma:one standard deviation | MΩ     | megaohms                    | nA     | nanoamperes     |

| V      | volts                        | μΑ     | microamperes                | ns     | nanoseconds     |

| Ω      | ohms                         | μF     | microfarads                 | nV     | nanovolts       |

| KB     | 1024 bytes                   | μΗ     | microhenrys                 | pA     | picoamperes     |

| ppm    | parts per million            | μS     | microseconds                | pF     | picofarads      |

| sps    | samples per second           | μV     | microvolts                  | ps     | picoseconds     |

| W      | watts                        | μVrms  | microvolts root-mean-square | fF     | femtofarads     |

| Α      | amperes                      | μW     | microwatts                  |        |                 |

#### **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. Not all user guidelines are production tested

| Symbol              | Description                                            | Min  | Тур                               | Max                               | Units | Notes                              |

|---------------------|--------------------------------------------------------|------|-----------------------------------|-----------------------------------|-------|------------------------------------|

| V <sub>CC</sub>     | DC Supply Voltage Range                                | -0.3 | -                                 | 18                                | V     | Pin 8, I <sub>CC</sub> = 20 mA max |

| I <sub>CC</sub>     | DC Supply Current at V <sub>CC</sub> Pin               | -    | -                                 | 20                                | mA    | Pin 8                              |

| V <sub>OUT</sub>    | OUTPUT Pin Voltage                                     | -0.3 | -                                 | 18                                | V     | Pin 7                              |

| V <sub>BOOST</sub>  | BOOST Pin Voltage                                      | -0.3 | -                                 | 18                                | V     | Pin 1                              |

| V <sub>VSENSE</sub> | V <sub>SENSE</sub> Pin Voltage                         | -0.7 | -                                 | 4                                 | V     | Pin 2, I <sub>VSENSE</sub> ≤ 10mA  |

| V <sub>VIN</sub>    | V <sub>IN</sub> Pin Voltage                            | -0.3 | -                                 | 18                                | V     | Pin 3                              |

| V <sub>ISENSE</sub> | I <sub>SENSE</sub> Pin Voltage                         | -0.3 | -                                 | 4                                 | V     | Pin 6                              |

| V <sub>VT</sub>     | V <sub>T</sub> Pin Voltage                             | -0.3 | -                                 | 4                                 | V     | Pin 4                              |

| P <sub>D</sub>      | Power Dissipation                                      | -    | -                                 | 526                               | mW    | T <sub>A</sub> ≤ 25°C              |

| T <sub>J MAX</sub>  | Maximum Junction Temperature                           | -    | -                                 | 125                               | °C    |                                    |

| T <sub>STG</sub>    | Storage Temperature                                    | -65  | -                                 | 150                               | °C    |                                    |

| T <sub>LEAD</sub>   |                                                        |      | °C                                | During IR reflow for ≤ 15 seconds |       |                                    |

| θ <sub>JB</sub> [1] | Thermal Resistance Junction-to-PCB board surface       | -    | -                                 | 70                                | °C/W  |                                    |

| V <sub>ESD</sub>    | ESD Voltage Rating 2000 V According to JEI JESD22-A114 |      | According to JEDEC<br>JESD22-A114 |                                   |       |                                    |

| I <sub>LU</sub>     | Latch Up Current                                       | -100 | -                                 | 100 mA According to JEDEC JESD    |       | According to JEDEC JESD78          |

#### Note

Document Number: 001-54879 Rev. \*B Page 12 of 19

θ<sub>JB</sub> provides an estimation of the die temperature relative to the Printed circuit board (PCB) surface temperature. This data is measured at the ground pin (pin 5) without using any thermal adhesives.

## **Electrical Characteristics**

$V_{CC} \! = \! 12V; \ \text{-}40^{\circ}C \leq T_{A} \leq 85^{\circ}C \ \text{unless otherwise specified}^{[2]}$

| Symbol                            | Description                                   | Min   | Тур   | Max   | Units | Notes                                   |

|-----------------------------------|-----------------------------------------------|-------|-------|-------|-------|-----------------------------------------|

| V <sub>IN</sub> Section (         | pin 3)                                        |       |       |       |       |                                         |

| V <sub>IN</sub>                   | Input Voltage Range                           | 0     | -     | 1.8   | V     | During normal operation (after startup) |

| I <sub>INST</sub>                 | Startup Current                               | -     | 10    | 15    | μΑ    | $V_{IN} = 10V, C_{VCC} = 10\mu F$       |

| Z <sub>VIN</sub>                  | Input Impedance                               | -     | 2.5   | -     | kΩ    | During normal operation (after startup) |

| V <sub>SENSE</sub> Secti          | on (pin 2)                                    |       |       |       |       | 1                                       |

| I <sub>BVS</sub>                  | Input Leakage Current                         | -     | -     | 1     | μА    | V <sub>SENSE</sub> = 2V                 |

| V <sub>SENSENOM</sub>             | Nominal Voltage Threshold                     | 1.523 | 1.538 | 1.553 | V     | T <sub>A</sub> = 25°C, Negative edge    |

| V <sub>SENSEMAX</sub>             | Output OVP Threshold                          | 1.683 | 1.700 | 1.717 | V     | T <sub>A</sub> = 25°C, Negative edge    |

| OUTPUT Sec                        | tion (pin 7)                                  |       |       |       |       | 1                                       |

| R <sub>DS(ON)LO</sub>             | Output Low Level ON-Resistance                | -     | 30    | -     | Ω     | I <sub>SINK</sub> = 5 mA                |

| R <sub>DS(ON)HI</sub>             | Output High Level ON-Resistance               | -     | 60    | -     | Ω     | I <sub>SOURCE</sub> = 5 mA              |

| t <sub>R</sub> [3]                | Rise Time (10% to 90%)                        | -     | 50    | -     | ns    | $T_A = 25$ °C, $C_L = 330$ pF           |

| t <sub>F</sub> [3]                | Fall Time (90% to 10%)                        | -     | 30    | -     | ns    | $T_A = 25$ °C, $C_L = 330$ pF           |

| f <sub>SWMAX</sub> <sup>[4]</sup> | Maximum Switching Frequency                   | -     | 200   | -     | kHz   |                                         |

| V <sub>CC</sub> Section           | (pin 8)                                       |       |       |       |       | 1                                       |

| V <sub>CCMAX</sub>                | Maximum Operating Voltage                     | -     | -     | 16    | V     |                                         |

| V <sub>CCST</sub>                 | Startup Threshold                             | 11    | 12    | 13    | V     | V <sub>CC</sub> Rising                  |

| V <sub>CCUVL</sub>                | Undervoltage Lockout Threshold                | 7.0   | 7.5   | 8.0   | V     | V <sub>CC</sub> Falling                 |

| I <sub>CC</sub>                   | Operating Current                             | -     | 3.9   | 4.5   | mA    | $C_L = 330 pF, V_{SENSE} = 1.5 V$       |

| V <sub>CC-CLAMP</sub>             | Zener Diode Clamp Voltage                     | -     | 19    | -     | V     | Test current of 10 mA                   |

| I <sub>SENSE</sub> Section        | on (pin 6)                                    | •     |       |       |       |                                         |

| V <sub>OCP</sub>                  | Overcurrent Threshold Limit                   | -     | 1.9   | -     | V     |                                         |

| V <sub>RSNS</sub>                 | I <sub>SENSE</sub> Short Protection Reference | -     | 0.16  | -     | V     |                                         |

| $V_{REGTH}$                       | CC Regulation Threshold Limit                 | -     | 1.8   | -     | V     |                                         |

| V <sub>T</sub> Section (p         | oin 4)                                        | •     | •     |       |       |                                         |

| V <sub>SDTH</sub>                 | Shutdown Threshold                            | -     | 0.09  | -     | V     |                                         |

| I <sub>BVSD</sub>                 | Input Leakage Current                         | -     | -     | 1.0   | μΑ    | V <sub>SD</sub> = 1.0V                  |

| I <sub>SD</sub>                   | Pull up Current Source                        | 95    | 100   | 105   | μΑ    |                                         |

| <b>BOOST Sect</b>                 | ion (pin 1)                                   |       |       | ı     |       |                                         |

| R <sub>DS(ON)LO-TR</sub>          | Output Low Level ON-Resistance                | -     | 100   | -     | Ω     | I <sub>SINK</sub> = 5 mA                |

| R <sub>DS(ON)HI-TR</sub>          | Output High Level ON-Resistance               | -     | 200   | -     | Ω     | I <sub>SOURCE</sub> = 5 mA              |

| t <sub>R-BST</sub> [3]            | Rise Time                                     | -     | 60    | -     | ns    |                                         |

| t <sub>F-BST</sub> <sup>[3]</sup> | Fall Time                                     | -     | 60    | -     | ns    |                                         |

- Adjust V<sub>CC</sub> above start-up threshold before setting at 12V.

These parameters are not 100% tested, guaranteed by design and characterization.

Operating frequency varies based on line and load conditions.

## **Typical Application Diagram**

## **Typical Performance Characteristics**

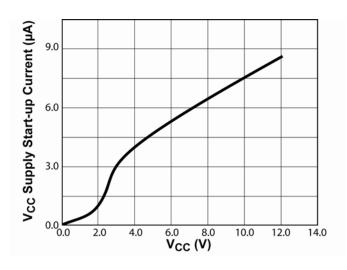

Figure 13.  $V_{CC}$  vs.  $V_{CC}$  supply start-up current

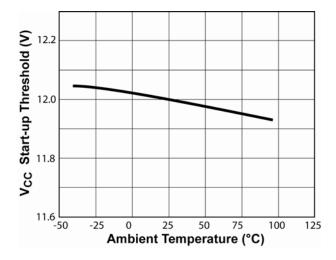

Figure 14.  $V_{CC}$  startup threshold vs. temperature

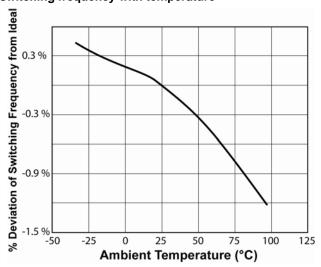

Figure 15. % Deviation of switching frequency to ideal switching frequency with temperature

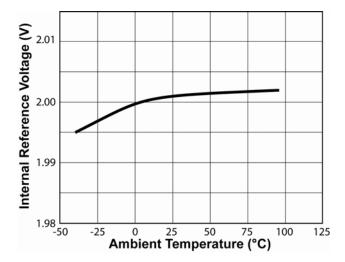

Figure 16. Internal reference voltage vs. temperature

#### **Performance Information**

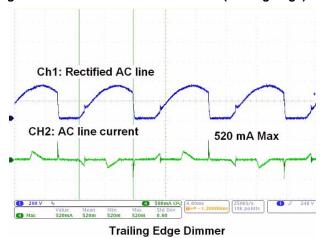

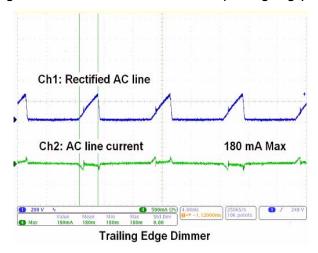

Figure 17. Inrush and AC Peak Current (Trailing Edge)

Figure 18. Inrush and AC Peak Current (Trailing Edge)

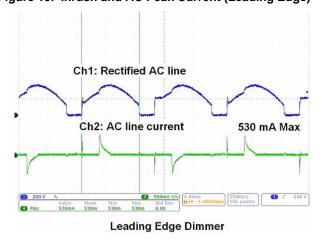

Figure 19. Inrush and AC Peak Current (Leading Edge)

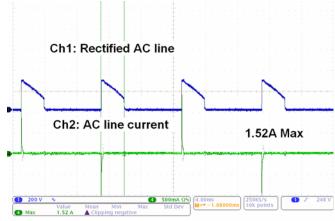

Figure 20. Inrush and AC Peak Current (Leading Edge)

Leading Edge Dimmer

Figure 21. Inrush and AC Peak Current (No Dimmer)

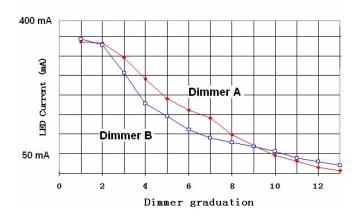

Figure 22. Dimming Curve

Document Number: 001-54879 Rev. \*B

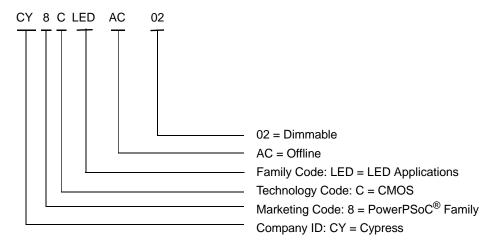

## **Ordering Information**

| Ordering Code | No. of Pins | Package | Temperature Range |

|---------------|-------------|---------|-------------------|

| CY8CLEDAC02   | 8           | SOIC    | -40°C to 85°C     |

## **Ordering Code Definitions**

## **Packaging Information**

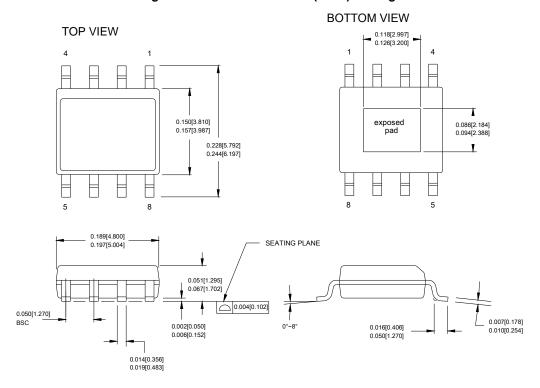

### **Physical Package Dimensions**

Figure 14. 8-Pin Small Outline (SOIC) Package

- 1. DIMENSIONS IN INCHES[MM]

- 2. REFERENCE JEDEC MS-012F

- 3. PACKAGE WEIGHT 0.07 gm

001-54263 \*A

#### **Document History Page**

| Document Title: CY8CLEDAC02 AC-DC Controller for Dimmable LED Lighting Document Number: 001-54879 |         |                    |                    |                                                                                                                                                                                                           |  |  |  |

|---------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                                          | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                     |  |  |  |

| **                                                                                                | 2746461 | KJV                | 07/30/09           | Preliminary data sheet                                                                                                                                                                                    |  |  |  |

| *A                                                                                                | 2882776 | KJV/AESA           | 02/22/2010         | Updated Features, Description, and Functional Description sections. Updated Electrical Specifications. Updated package diagram. Added Contents. Updated links in Sales, Solutions, and Legal Information. |  |  |  |

| *B                                                                                                | 2901104 | KJV/VED            | 03/29/2010         | Release to web                                                                                                                                                                                            |  |  |  |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive cypress.com/go/automotive Clocks & Buffers cypress.com/go/clocks Interface cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/powerpsoc

cypress.com/go/plc

Memory cypress.com/go/memory

Optical & Image Sensing cypress.com/go/image

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/USB

Wireless/RF cypress.com/go/wireless

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2009-2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-54879 Rev. \*B

Revised March 29, 2010