a leap ahead in analog

# AS8221D FlexRay Standard Transceiver

Objective Data Sheet

# 1 General Description

This objective data sheet describes the intended functionality of the AS8221 bus transceiver. As long the device is not fully qualified, the parameters are not characterized in the means that parameters may change or can be updated during final product qualification and characterization. This document shows the objective of the AS8221 and this document is subjected to change without notice.

The AS8221 is a high speed automotive bus driver\_designed according to the FlexRay Electrical Physical Layer Specification V2.1 Rev B. The AS8221 operates as a bi-directional interface between the FlexRay Communication Controller and the twisted-pair copper wiring.

The AS8221 provides an optimized host controller interface consisting of three low-active pins. The Enable and Standby input pins for mode handling by the microcontroller and the Error out pin where system, chip failures or status information are signalled to the microcontroller. Signalling logic high on the Enable and Standby pin the device will enter Normal mode in case no fault condition is given and in this mode the device is fully operational meaning FlexRay communication is possible. Additionally a Receive Only mode is implemented, which can be accessed by the microcontroller where only FlexRay streams can be received in order to avoid unwanted disturbances on the FlexRay bus while listening on the bus traffic. In the low power modes (Standby and Sleep mode) very low power consumption is achieved.

In case of undervoltage on one of the supply voltages (VBAT, Vccand VIO) the device will change its mode to a low power mode (either Standby or Sleep mode) and the device will signal an error accordingly. In case of low voltage is detected on both VBAT and Vcc the device will enter the Power Off mode, where no operation is possible. A safe mechanism from the low power modes to Power Off mode and vice versa is implemented ensuring that no deadlock can happen during the startup phase.

Ensuring application in safety critical environments a two wire bus-guardian interface is implemented where additional monitoring circuitries on the electronic-control-unit can activate and deactivate the transmitter and additionally on the receive enable output in low power modes the wake conditions and in normal power modes the received FlexRay streams can be monitored.

A thermal sensor circuit with an integral shutdown mechanism prevents damage to the device in extreme temperature conditions. The symmetrical transient control for the high- and low-side driver for both the busminus and bus-plus line allows an ideal balance of communications over different network topologies, with excellent EMC performance.

# 2 Key Features

- Compliant with FlexRay Electrical Physical Layer Specification V2.1 Rev. B

- Data transfer up to 10 Mbps

- Excellent EMC performances. High common mode range insure excellent EMI

- Interface for Bus Guardian or supervision circuits

- Automatic thermal shutdown protection

- Supports 12V and 24V systems with very low sleep current

- Integrated power management system

- Two inhibit pins for external voltage supply control

- Local wake-up input

- Remote wake-up capability via FlexRay bus in low power modes

- Supports 2.5, 3, 3.3, 5 V microcontrollers and automatically adapts to interface levels

- Protection against damage due to short circuit conditions on the bus (positive and negative battery voltage)

- Operating temperature range -40°C to +125°C

- Lead-free SSOP20 package

# 3 Applications

The AS8221 FlexRay Standard Transceiver is best fitting for all automotive applications where the full functionality of the FlexRay bus driver is needed in the electronic-control-unit like bus wake-up and control for voltage supplies.

The device addresses all ECUs connected to the permanent battery supply (clamp 30). The AS8221 is connected to the battery voltage and therefore can be used as the only ECU wake-up component with very low power consumption in Sleep mode.

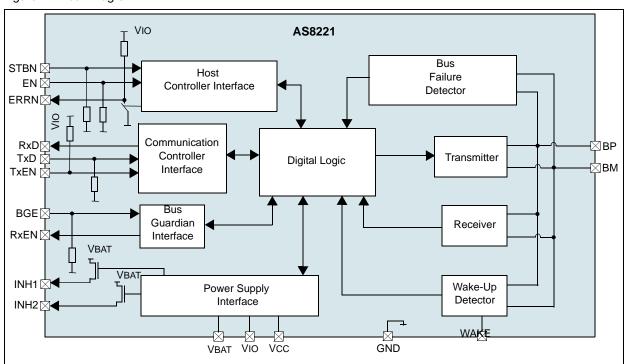

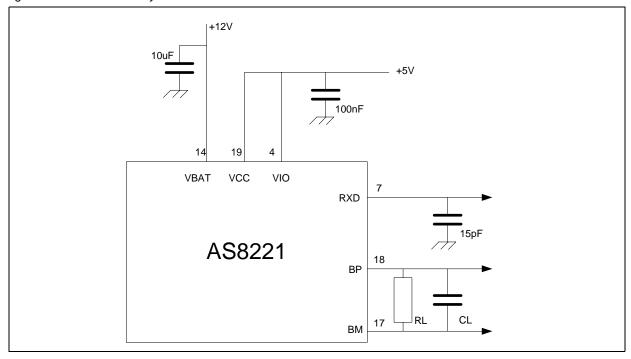

Figure 1. Block Diagram

# **Contents**

| 1 | General Description                                       | 1  |

|---|-----------------------------------------------------------|----|

| 2 | Key Features                                              | 1  |

| 3 | Applications                                              | 1  |

| 4 | Pin Assignments                                           | 5  |

|   | 4.1 Pin Descriptions                                      | 5  |

| 5 | Absolute Maximum Ratings                                  |    |

|   | Electrical Characteristics                                |    |

|   | Typical Operating Characteristics                         |    |

|   | Detailed Description                                      |    |

| U | 8.1 Block Description                                     |    |

|   | 8.2 Events                                                |    |

|   | 8.3 Operating Modes                                       |    |

|   | 8.3.1 NORMAL mode                                         |    |

|   | 8.3.2 RECEIVE ONLY mode                                   |    |

|   | 8.3.3 STANDBY mode                                        |    |

|   | 8.3.4 GO TO SLEEP mode                                    |    |

|   | 8.3.5 SLEEP mode                                          |    |

|   | 8.4 Non Operating Mode                                    |    |

|   | 8.4.1 POWER OFF                                           | 15 |

|   | 8.5 Undervoltage Events                                   | 16 |

|   | 8.5.1 Undervoltage VBAT                                   | 16 |

|   | 8.5.2 Undervoltage Vio                                    | 16 |

|   | 8.5.3 Undervoltage Vcc                                    | 16 |

|   | 8.6 Power On/Off Events                                   | 16 |

|   | 8.7 Wake-Up Events                                        | 16 |

|   | 8.7.1 Remote Wake-Up event                                | 16 |

|   | 8.7.2 Local Wake-Up Event                                 | 17 |

|   | 8.8 System Description                                    | 18 |

|   | 8.9 Fail Silent Behavior                                  | 19 |

|   | 8.9.1 State transitions due to under voltage detection    | 19 |

|   | 8.9.2 State transitions due to voltage recovery detection | 19 |

|   | 8.10 Wake-Up Mechanism                                    | 19 |

|   | 8.10.1 Remote Wake-Up                                     | 19 |

|   | 8.11 Mode Transitions                                     | 19 |

|   | 8.11.1 ERRN Signalling                                    | 23 |

|   | 8.12 Loss of ground                                       | 23 |

|   | 8.13 Error Flags Description                              | 23 |

|   | 8.13.1 Undervoltage VBAT detected                         | 23 |

|   | 8.13.2 Undervoltage Vio detected                          |    |

|   | 8.13.3 Undervoltage Vcc detected                          |    |

|   | 8.13.4 Bus error                                          |    |

|   | 8.13.5 Low current on BP high side driver                 |    |

|   | 8.13.6 Low current on BP low side driver                  |    |

|   | 8.13.7 Low current on BM high side driver                 |    |

|   | O. 13.0 FOM CRITCHE OH DIM IOM 2005 RHINGH                |    |

| 8.13.9 High current on BP high side driver                                                  | 24 |

|---------------------------------------------------------------------------------------------|----|

| 8.13.10 High current on BP low side driver                                                  | 24 |

| 8.13.11 High current on BM high side driver                                                 | 24 |

| 8.13.12 High current on BM low side driver                                                  | 24 |

| 8.13.13 BP open line                                                                        | 24 |

| 8.13.14 BM open line                                                                        | 24 |

| 8.13.15 BP short circuit to Vcc                                                             | 24 |

| 8.13.16 BP short circuit to GND                                                             | 24 |

| 8.13.17 BM short circuit to Vcc                                                             | 24 |

| 8.13.18 BM short circuit to GND                                                             |    |

| 8.13.19 Short circuit between BP and BM                                                     | 25 |

| 8.13.20 Over temperature                                                                    |    |

| 8.13.21 TxEN_BGE timeout                                                                    | 25 |

| 8.13.22 Error flag                                                                          | 25 |

| 8.14 Status Flags Description                                                               | 25 |

| 8.14.1 Power on flag                                                                        | 25 |

| 8.15 Error Flags and Status Flags Read Out                                                  | 25 |

| 8.15.1 Error and Status flag bit order                                                      | 26 |

| 8.16 Failure detector                                                                       | 26 |

| 8.16.1 Power Off                                                                            | 26 |

| 8.16.2 Undervoltage VBAT                                                                    |    |

| 8.16.3 Undervoltage Vcc                                                                     |    |

| 8.16.4 Undervoltage Vio                                                                     |    |

| 8.16.5 Bus Error (Short circuit/open load on bus lines and short circuit between BP and BM) | 27 |

| 8.16.6 TxD interrupted                                                                      | 27 |

| 8.16.7 TxEN timeout                                                                         | 27 |

| 8.16.8 Over temperature                                                                     | 27 |

| 8.16.9 No mode change                                                                       | 27 |

| 8.17 Transmitter                                                                            | 28 |

| 8.18 Receiver                                                                               | 30 |

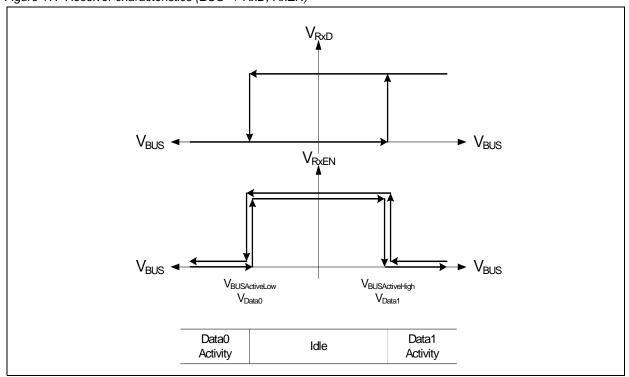

| 8.18.1 Bus activity and idle detection (only in NORMAL and RECEIVE ONLY mode)               | 30 |

| 8.18.2 Bus data detection (only in NORMAL and RECEIVE ONLY mode)                            | 30 |

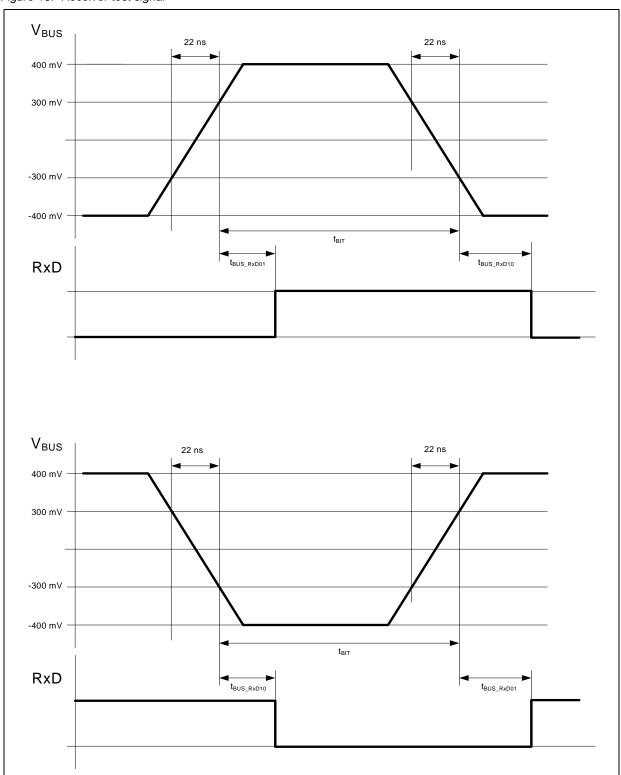

| 8.18.3 Receiver test signal                                                                 | 32 |

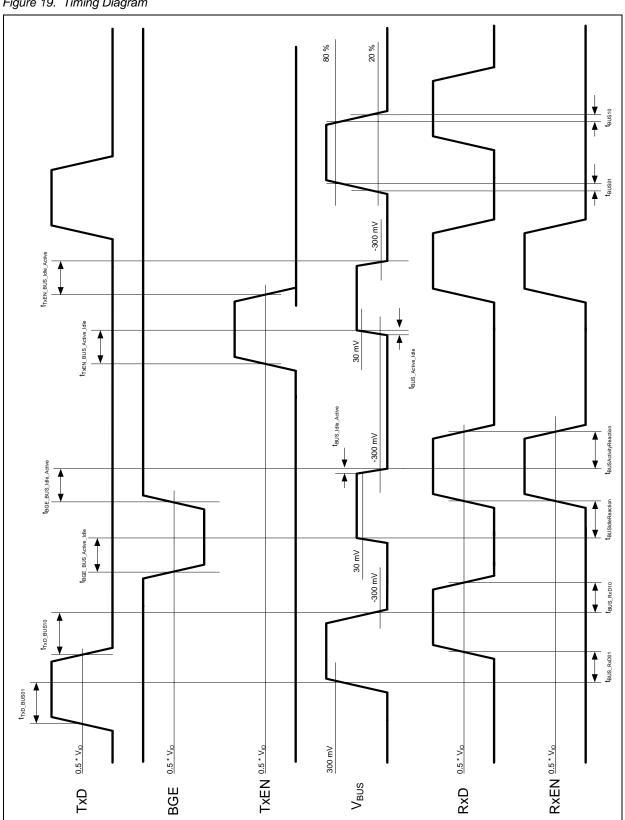

| 8.18.4 Transceiver Timing                                                                   | 33 |

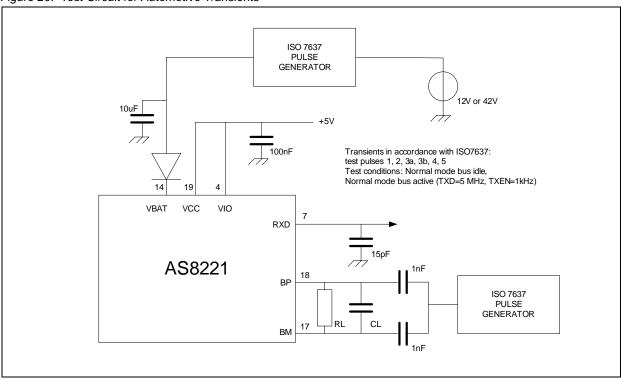

| 8.19 Test Circuits                                                                          | 34 |

| 9 Appendix                                                                                  | 35 |

| 9.1 FlexRay Functional Classes                                                              | 35 |

| 9.2 FlexRay Parameter Comparison                                                            |    |

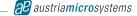

| 10 Package Drawings and Markings                                                            |    |

|                                                                                             |    |

| 11 Ordering Information                                                                     | 43 |

# 4 Pin Assignments

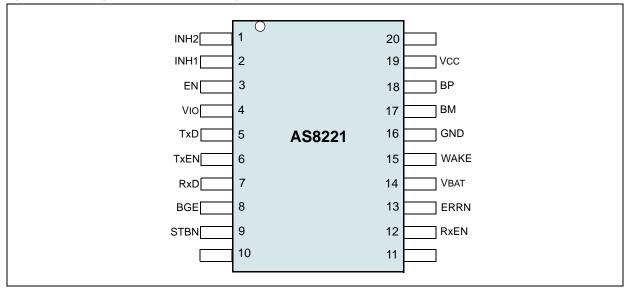

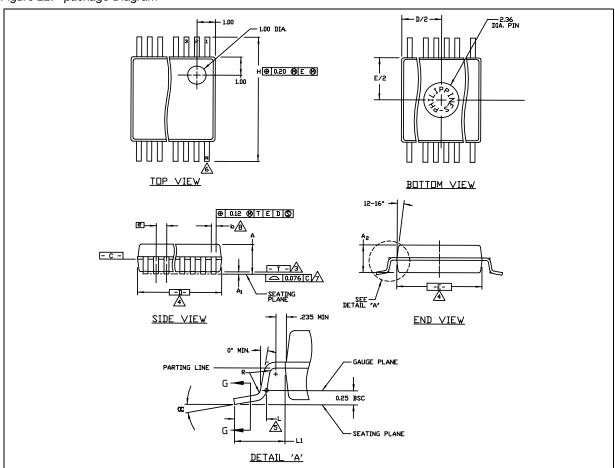

Figure 2. Pin Assignments SSOP20 Package

# **Pin Descriptions**

Table 1. Pin Descriptions

| Pin Name | Pin Number | Description                                                    |

|----------|------------|----------------------------------------------------------------|

| INH2     | 1          | Analog Output. Inhibit 2 output for switching external voltage |

| 111112   |            | regulator                                                      |

| INH1     | 2          | Analog Output. Inhibit 1 output for switching external voltage |

|          |            | regulator                                                      |

| EN       | 3          | Digital Input. Enable input                                    |

| Vio      | 4          | Supply Voltage. I/O supply voltage                             |

| TxD      | 5          | Digital Input. Transmit data input                             |

| TxEN     | 6          | Digital Input. Transmitter enable input                        |

| RxD      | 7          | Digital Output. Receive data output                            |

| BGE      | 8          | Digital Input. Bus guardian enable input                       |

| STBN     | 9          | Digital Input. Standby input                                   |

| Not used | 10         |                                                                |

| Not used | 11         |                                                                |

| RxEN     | 12         | Digital Output. Receive data enable output                     |

| ERRN     | 13         | Digital Output. Error diagnosis output and wake status output  |

| VBAT     | 14         | Supply Voltage. Battery supply voltage                         |

| WAKE     | 15         | Analog Input. Local wake-up input                              |

| GND      | 16         | Ground                                                         |

| BM       | 17         | Analog Input/Output. Bus line Minus                            |

| BP       | 18         | Analog Input/Output. Bus line Plus                             |

| Vcc      | 19         | Supply voltage.                                                |

| Not used | 20         |                                                                |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 7 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                               | Min  | Max          | Units | Notes                                                                                                             |

|---------------------------------------------------------|------|--------------|-------|-------------------------------------------------------------------------------------------------------------------|

| Battery Supply Voltage (VBAT)                           | -0.3 | +50          | V     |                                                                                                                   |

| Supply Voltage (Vcc)                                    | -0.3 | +7.0         | V     |                                                                                                                   |

| Supply Voltage (Vio)                                    | -0.3 | +7.0         | V     |                                                                                                                   |

| DC Voltage at EN, STBN, ERRN, TxD, RxD, TxEN, BGE, RxEN | -0.3 | Vio +<br>0.3 | V     | Vio < Vcc                                                                                                         |

| DC Voltage on pin WAKE, INH1, INH2                      | -0.3 | VBAT + 0.3   |       |                                                                                                                   |

| DC Voltage at BP and BM                                 | -40  | +50          | V     |                                                                                                                   |

| Input current (latchup immunity)                        | -100 | 100          | mA    | According to JEDEC 78                                                                                             |

| Electrostatic discharge at bus lines BP, BM, VBAT, WAKE | -4   | +4           | kV    | According to AEC-Q100-002                                                                                         |

| Electrostatic discharge                                 | -2   | +2           | kV    | According to AEC-Q100-002                                                                                         |

| Transient voltage on BP, BM                             | -200 | +200         | V     | According to ISO7637 part3 test pulses a and b; class C; RL=45 W, CL= 100 pF; (see Figure 20 on page 34).         |

|                                                         | -200 | +200         | V     | According to ISO7637 part2 test pulses 1, 2, 3a and 3b; class C; RL=45 W, CL= 100 pF; (see Figure 20 on page 34). |

| Transient voltage on VBAT                               | +6.5 | +50          | V     | According to ISO7637 part2 test pulse 4; class C; RL=45 W, CL= 100 pF; (see Figure 20 on page 34).                |

|                                                         |      | +50          |       | According to ISO7637 part2 test pulse 5b; class C; RL=45 W, CL= 100 pF; (see Figure 20 on page 34).               |

| Total power dissipation (all supplies and outputs)      |      | 150          | mW    |                                                                                                                   |

| Storage temperature                                     | -55  | +150         | °C    |                                                                                                                   |

| Junction temperature                                    | -40  | +150         | °C    |                                                                                                                   |

| Package body temperature <sup>1</sup>                   |      | 250          | °C    |                                                                                                                   |

| Humidity non-condensing                                 | 5    | 85           | %     |                                                                                                                   |

<sup>1.</sup> The reflow peak soldering temperature (body temperature) specified is in accordance with *IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices"*. The lead finish for Pb-free leaded packages is matte tin (100% Sn).

# **6 Electrical Characteristics**

$T_{Vj}$  = -40 to +150 °C, Vcc = +4.75V to +5.25V, VBAT= 6.5 to +50 V, VIO = +2.2 to Vcc,  $R_L$ = 45 $\Omega$ ,  $C_L$ = 100 pF unless otherwise specified.

Table 3. Electrical Characteristics

| Symbol Parameter         |                                                                                | Conditions M                                                                                      |              | Тур | Max          | Units |

|--------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------|-----|--------------|-------|

| Supply Voltage           |                                                                                |                                                                                                   |              |     |              |       |

| T <sub>amb</sub>         | Ambient temperature                                                            |                                                                                                   | -40          |     | +125         | ۰C    |

| Vcc-Vio                  | Difference of supplies                                                         |                                                                                                   | -0.1         |     | 3.05         | V     |

|                          |                                                                                | VBAT=12V; Low Power Mode <sup>1</sup><br>T <sub>vj</sub> < 125°C                                  | 0            |     | 30           | μΑ    |

| I <sub>BAT</sub>         | VBAT current consumption                                                       | VBAT=12V; Low Power Mode <sup>1</sup><br>T <sub>vj</sub> < 150°C                                  | 0            |     | 50           | μΑ    |

|                          |                                                                                | Non Low Power Mode                                                                                | 0            |     | 1            | mA    |

|                          |                                                                                | Low Power Mode <sup>1</sup><br>Vcc = 0V to +5.25V                                                 | -5           |     | 20           | μA    |

|                          | Voc surrent consumption                                                        | Non Low Power Mode:<br>NORMAL, driver enabled;                                                    | 0            |     | 45           | mA    |

| Icc                      | Vcc current consumption                                                        | Non Low Power Mode: NORMAL, driver enabled; $R_{BUS} = \infty \Omega$                             | 0            |     | 15           | mA    |

|                          |                                                                                | Non Low Power Mode:<br>RECEIVE ONLY                                                               | 0            |     | 10           | mA    |

| I <sub>IO</sub>          | Vio current consumption                                                        | Low Power Mode <sup>1</sup><br>Vio = 0V to +5.25V                                                 | -5           |     | 5            | μΑ    |

|                          |                                                                                | Non Low Power Mode                                                                                | 0            |     | 1            | mA    |

| State Transitions        |                                                                                |                                                                                                   |              |     | •            |       |

| tstbn_rxd                | Delay STBN high to RxD high with wake flag set                                 |                                                                                                   | 1            |     | 50           | μs    |

| t <sub>STBN_RxEN</sub>   | Delay STBN high to RxEN high with wake flag set                                |                                                                                                   | 1            |     | 50           | μs    |

| tsleep_INH1              | Delay STBN high to INH1<br>high                                                | INH1 high = 80% VBAT                                                                              | 1            |     | 50           | μs    |

| tstandby_inh2            | Delay STBN high to INH2<br>high                                                | INH2 high = 80% VBAT                                                                              | 1            |     | 50           | μs    |

| t <sub>SLEEP</sub>       | go-to-sleep hold time                                                          | INH1 low = 20% VBAT                                                                               | 10           |     | 70           | μs    |

| Transmitter              |                                                                                |                                                                                                   |              |     |              |       |

| V <sub>BUS_DIFF_D0</sub> | Differential bus voltage low in NORMAL mode (Data0)                            | $V_{BPdata0}$ - $V_{BMdata0}$ ;<br>$40\Omega < R_L < 55\Omega$                                    | -2           |     | -0.6         | V     |

| V <sub>BUS_DIFF_D1</sub> | Differential bus voltage<br>high in NORMAL mode<br>(Data1)                     | $V_{BPdata1}$ - $V_{BMdata1}$ ; $40\Omega$ < $R_L$ < $55\Omega$                                   | 0.6          |     | 2            | V     |

| $\Delta V_{BUS\_DIFF}$   | Matching between Data0<br>and Data1 differential bus<br>voltage in NORMAL mode | $\begin{array}{c} V_{BUS\_DIFF\_D0} - V_{BUS\_DIFF\_D1} \\ 40\Omega < R_L < 55\Omega \end{array}$ | -200         |     | 200          | mV    |

| V <sub>BUS_COM_D0</sub>  | Common mode bus voltage in case of Data0 in non low power modes                | $V_{\mathrm{BPdata0}/2} + V_{\mathrm{BMdata0}/2}$ $40\Omega < R_{\mathrm{L}} < 55\Omega$          | 0.4 *<br>Vcc |     | 0.6 *<br>Vcc | V     |

Table 3. Electrical Characteristics

| Symbol                                                 | Parameter                                                       | Conditions                                                                 | Min          | Тур | Max          | Units |

|--------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|--------------|-----|--------------|-------|

| V <sub>BUS_COM_D1</sub>                                | Common mode bus voltage in case of Data1 in non low power modes | $V_{BPdata1}/2 + V_{BMdata1}/2$<br>$40\Omega < R_L < 55\Omega$             | 0.4 *<br>Vcc |     | 0.6 *<br>Vcc | V     |

| ΔV <sub>BUS</sub> _COM                                 | Matching between Data0<br>and Data1 common mode<br>voltage      | $V_{BUS\_COM\_D0}$ - $V_{BUS\_COM\_D1}$<br>$40\Omega$ < $R_L$ < $55\Omega$ | -200         |     | 200          | mV    |

| V <sub>BUS_DIFF_Idle</sub>                             | Absolute differential bus voltage in idle mode                  |                                                                            |              |     | 30           | mV    |

| IBP <sub>BMShortMax</sub><br>IBM <sub>BPShortMax</sub> | Absolute max current when BP is shorted to BM                   | $V_{BP} = V_{BM}$                                                          |              |     | +100         | mA    |

| IBP <sub>GNDShortMax</sub>                             | Absolute max current when BP is shorted to GND                  | V <sub>BP</sub> = 0V                                                       |              |     | +100         | mA    |

| IBM <sub>GNDShortMax</sub>                             | Absolute max current when BM is shorted to GND                  | V <sub>BM</sub> = 0V                                                       |              |     | +100         | mA    |

| IBP <sub>-5VShortMax</sub>                             | Absolute max current when BP is shorted to -5 V                 | V <sub>BP</sub> = -5V                                                      |              |     | +100         | mA    |

| IBM <sub>-5VShortMax</sub>                             | Absolute max current when BM is shorted to -5 V                 | V <sub>BM</sub> = -5V                                                      |              |     | +100         | mA    |

| IBP <sub>27VShortMax</sub>                             | Absolute max current when BP is shorted to 27 V                 | V <sub>BP</sub> = 27V                                                      |              |     | +100         | mA    |

| IBM <sub>27VShortMax</sub>                             | Absolute max current when BM is shorted to 27 V                 | V <sub>BM</sub> = 27V                                                      |              |     | +100         | mA    |

| IBP <sub>48VShortMax</sub>                             | Absolute max current when BP is shorted to 48 V                 | V <sub>BP</sub> = 48V                                                      |              |     | +100         | mA    |

| IBM <sub>48VShortMax</sub>                             | Absolute max current when BM is shorted to 48 V                 | V <sub>BM</sub> = 48V                                                      |              |     | +100         | mA    |

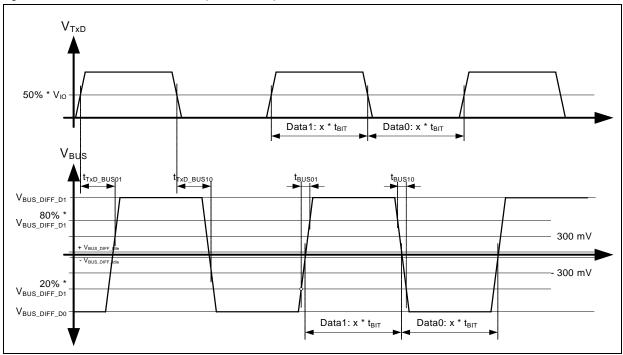

| t <sub>TxD_BUS01</sub>                                 | Delay time from TxD to<br>BUS positive edge                     | t <sub>TxD_RISE</sub> = 5ns                                                |              |     | 50           | ns    |

| t <sub>TxD_BUS10</sub>                                 | Delay time from TxD to<br>BUS negative edge                     | t <sub>TxD_FALL</sub> = 5ns                                                |              |     | 50           | ns    |

| t <sub>TxD_MISMATCH</sub>                              | Delay time from TxD to<br>BUS mismatch                          | t <sub>TxD_BUS10</sub> - t <sub>TxD_BUS01</sub>                            | -4           |     | 4            | ns    |

| t <sub>BUS10</sub>                                     | Fall time differential bus voltage                              | 80% - 20% of V <sub>BUS</sub>                                              | 3.75         |     | 18.75        | ns    |

| t <sub>BUS01</sub>                                     | Rise time differential bus voltage                              | 20% - 80% of V <sub>BUS</sub>                                              | 3.75         |     | 18.75        | ns    |

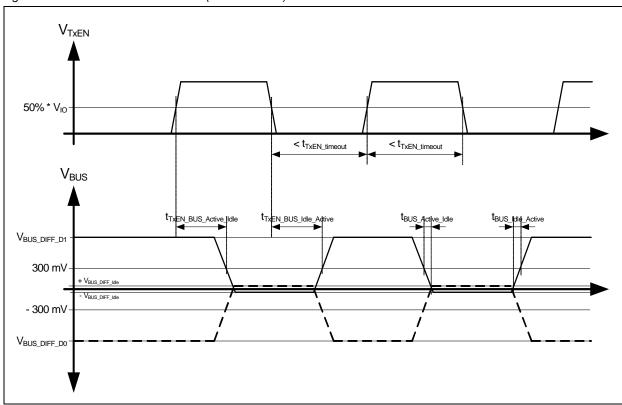

| t <sub>TxEN_BUS_Idle_Active</sub>                      | Delay time from TxEN to bus active                              |                                                                            |              |     | 50           | ns    |

| t <sub>TxEN_BUS_Active_Idle</sub>                      | Delay time from TxEN to bus idle                                |                                                                            |              |     | 50           | ns    |

| t <sub>TxEN_MISMATCH</sub>                             | Delay time from TxEN to bus mismatch                            | t <sub>TxEN_BUS_Idle_Active</sub>                                          |              |     | 50           | ns    |

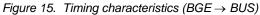

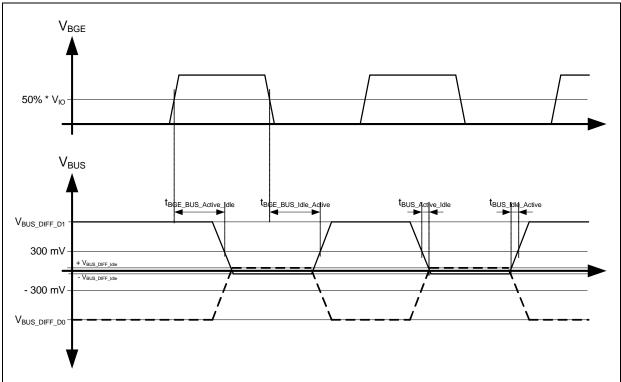

| tBGE_BUS_Idle_Active                                   | Delay time from BGE to bus active                               |                                                                            |              |     | 50           | ns    |

| tBGE_BUS_Active_Idle                                   | Delay time from BGE to bus idle                                 |                                                                            |              |     | 50           | ns    |

| tBUS_Idle_Active                                       | Differential bus voltage transition time: idle to active        |                                                                            |              |     | 30           | ns    |

Table 3. Electrical Characteristics

| Symbol                                               | Parameter                                                   | Conditions                                                                                                                  | Min         | Тур         | Max         | Units |

|------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------|

| t <sub>BUS_Active_Idle</sub>                         | Differential bus voltage transition time: active to idle    |                                                                                                                             |             |             | 30          | ns    |

| t <sub>TxEN_timeout</sub>                            | TxEN timeout                                                |                                                                                                                             | 0.64        |             | 3.07        | ms    |

| Receiver                                             |                                                             |                                                                                                                             |             |             |             |       |

| R <sub>BP</sub> , R <sub>BM</sub>                    | BP, BM input resistance                                     | Idle mode; R <sub>BUS</sub> =∞                                                                                              | 10          |             | 40          | ΚΩ    |

| R <sub>DIFF</sub>                                    | BP, BM differential input resistance                        | Idle mode; R <sub>BUS</sub> =∞                                                                                              | 20          |             | 80          | ΚΩ    |

| V <sub>BPidle</sub> ,<br>V <sub>BMidle</sub>         | Idle voltage in non low<br>power modes on pin BP,<br>BM     | Non low power modes;<br>V <sub>TxEN</sub> = V <sub>IO</sub>                                                                 | 0.4*<br>Vcc | 0.5*<br>Vcc | 0.6*<br>Vcc | ٧     |

| V <sub>BPidle_low</sub> ,<br>V <sub>BMidle_low</sub> | Idle voltage in low power modes on pin BP, BM               | Low power modes                                                                                                             | -0.2        | 0           | +0.2        | V     |

| I <sub>BPidle</sub>                                  | Absolute idle output current on pin BP                      | -40V < V <sub>BP</sub> < 50V                                                                                                | 0           |             | 7.5         | mA    |

| I <sub>BMidle</sub>                                  | Absolute idle output current on pin BM                      | -40V < V <sub>BM</sub> < 50V                                                                                                | 0           |             | 7.5         | mA    |

| I <sub>BPleak</sub> ,<br>I <sub>BMleak</sub>         | Absolute leakage current, when not powered                  | $V_{BP} = V_{BM} = 5V$ , $V_{CC} = 0V$ , $V_{BAT} = 0V$ ; $V_{IO} = 0V$                                                     | 0           |             | +10         | uA    |

| V <sub>BUSActiveHigh</sub>                           | Activity detection differential input voltage high          | Normal power modes;<br>VRECEIVE_COM:<br>-10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                                   | 150         | 225         | 400         | mV    |

| $V_{BUSActiveLow}$                                   | Activity detection differential input voltage low           | Normal power modes;<br>VRECEIVE_COM:<br>-10V < (V <sub>BP</sub> , V <sub>BM</sub> )< 15V                                    | -400        | -225        | -150        | mV    |

| V <sub>Data1</sub>                                   | Data1 detection differential input voltage                  | Pre-condition: activity already detected. Normal power modes;  VRECEIVE_COM: -10V < (VBP, VBM) < 15V                        | 150         | 225         | 300         | mV    |

| V <sub>Data0</sub>                                   | Data0 detection differential input voltage                  | Pre-condition: activity already detected. Normal power modes;  VRECEIVE_COM: -10V < (VBP, VBM) < 15V                        | -300        | -225        | -150        | mV    |

| V <sub>DataErr</sub>                                 | Mismatch between Data0 and Data1 differential input voltage | 2 x (   V <sub>Data0</sub>   -   V <sub>Data1</sub>   ) /<br>(  V <sub>Data0</sub>   +   V <sub>Data1</sub>  ) <sup>2</sup> |             |             | 10          | %     |

| V <sub>RECEIVE_</sub> COM                            | Max. common mode voltage range when receiving               | Normal power modes                                                                                                          | -10         |             | +15         | ٧     |

| t <sub>BUS_RxD10</sub>                               | Delay from BUS to RxD negative edge                         | C <sub>RxD</sub> = 15 pF <sup>3</sup>                                                                                       |             |             | 80          | ns    |

| t <sub>BUS_RxD01</sub>                               | Delay from BUS to RxD positive edge                         | $C_{RxD}$ = 15 pF $^3$                                                                                                      |             |             | 80          | ns    |

| t <sub>BIT</sub>                                     | Bit time                                                    | $C_{RxD} = 15 pF^3$                                                                                                         | 54          |             |             | ns    |

| t <sub>RxD_</sub> ASYM                               | Delay time from BUS to<br>RxD mismatch                      | C <sub>RXD</sub> =15 pF;<br> t <sub>BUS_RxD10</sub> -t <sub>BUS_RxD01</sub>   <sup>3</sup>                                  |             |             | 5           | ns    |

Table 3. Electrical Characteristics

| Symbol                       | Parameter                                                  | Conditions                                                              | Min  | Тур | Max  | Units |

|------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------|------|-----|------|-------|

| t <sub>RxD_FALL</sub>        | Fall time RxD voltage                                      | 80% - 20% of V <sub>RxD</sub> ;<br>C <sub>RxD</sub> =15 pF <sup>3</sup> |      |     | 5    | ns    |

| t <sub>RxD_</sub> RISE       | Rise time RxD voltage                                      | 20% - 80% of V <sub>RxD</sub> ;<br>C <sub>RxD</sub> =15 pF <sup>3</sup> |      |     | 5    | ns    |

| tBUSIdleDetection            | Idle detection time                                        | V <sub>BUS</sub> : 400mV → 0V                                           | 50   |     | 200  | ns    |

| tBUSActivitiyDetection       | Activity detection time                                    | V <sub>BUS</sub> : 0V → 400mV                                           | 100  |     | 250  | ns    |

| <sup>t</sup> BUSIdleReaction | Idle reaction time                                         | $V_{BUS}$ : 400mV $\rightarrow$ 0V                                      | 50   |     | 300  | ns    |

| tBUSActivityReaction         | Activity reaction time                                     | V <sub>BUS</sub> : 0V → 400mV                                           | 100  |     | 350  | ns    |

| Wake-Up Detector             |                                                            |                                                                         |      |     |      |       |

| t <sub>BWU_D0</sub>          | Data0 detection time in remote wake-up pattern             | -10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                       | 1    |     | 4    | μs    |

| t <sub>BWU_ldle</sub>        | Idle or Data1 detection time in remote wake-up pattern     | -10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                       | 1    |     | 4    | μs    |

| t <sub>BWU_Detect</sub>      | Total remote wake-up detection time                        | -10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                       | 48   |     | 140  | μs    |

| V <sub>BWUTH</sub>           | Bus wake-up detection threshold                            | -10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                       | -300 |     | -150 | mV    |

| V <sub>LWUTH</sub>           | Local wake-up detection threshold                          |                                                                         | -2   |     | 4    | V     |

| I <sub>LWUL</sub>            | Low level input current on local WAKE pin                  | VBAT = 12V; $V_{LWAKE} = 2V$ for t < $t_{LWUFilter}$                    | -20  |     | -5   | μΑ    |

| I <sub>LWUH</sub>            | High level input current on local WAKE pin                 | $VBAT = 12V; V_{LWAKE} = 4V \text{ for t}$ $< t_{LWUFilter}$            | 5    |     | 20   | μA    |

| t <sub>LWUFilter</sub>       | Local wake filter time                                     |                                                                         | 1    |     | 40   | μs    |

| Supply Voltage Mor           | nitor                                                      |                                                                         |      |     |      |       |

| V <sub>ВАТТНН</sub>          | VBAT undervoltage recovery threshold                       |                                                                         | 3.5  |     | 4.5  | V     |

| $V_{BATTHL}$                 | VBAT undervoltage detection threshold                      |                                                                         | 2.5  |     | 3.5  | V     |

| V <sub>ССТНН</sub>           | Vcc under-voltage recovery threshold                       |                                                                         | 3.5  |     | 4.5  | V     |

| VCCTHL                       | Vcc undervoltage detection threshold                       |                                                                         | 2.5  |     | 3.5  | V     |

| V <sub>IOTHH</sub>           | Vio undervoltage recovery threshold                        |                                                                         | 1.25 |     | 2.0  | V     |

| V <sub>IOTHL</sub>           | Vio undervoltage detection threshold                       |                                                                         | 0.75 |     | 1.5  | V     |

| tuv_detect                   | Detection time for undervoltage at VBAT, VCC, VIO          |                                                                         | 100  |     | 700  | ms    |

| t <sub>UV_REC</sub>          | Detection time for undervoltage recovery at VBAT, VCC, VIO |                                                                         | 0.7  |     | 5    | ms    |

| Bus Error Detection          | n                                                          |                                                                         |      |     |      |       |

| I <sub>THL</sub>             | Absolute bus current for low current detection             | NORMAL mode, Transmitter enabled                                        |      | 5   |      | mA    |

Table 3. Electrical Characteristics

| Symbol                    | Parameter                                                                       | Conditions                            | Min         | Тур | Max         | Units |

|---------------------------|---------------------------------------------------------------------------------|---------------------------------------|-------------|-----|-------------|-------|

| Ітнн                      | Absolute bus current for<br>high current detection                              | NORMAL mode, Transmitter enabled      |             | 40  |             | mA    |

| Vshort                    | Differential voltage on BP and BM for detecting short circuit between bus lines | NORMAL mode, Transmitter enabled      |             | 225 |             | mV    |

| t <sub>BUS_ERROR</sub>    | Bus error detection time                                                        | NORMAL mode, Transmitter enabled      |             | 20  |             | μs    |

| Over Temperature          |                                                                                 |                                       |             | •   |             |       |

| OT <sub>TH</sub>          | Over temperature threshold                                                      |                                       | 150         |     | 180         | °C    |

| $OT_TL$                   | Over temperature hysteresis                                                     |                                       | 10          |     | 20          | °C    |

| Power Supply Inter        | face                                                                            |                                       | •           | •   | •           | •     |

| $\Delta V_{OINH}$         | High level voltage drop on INH1, INH2                                           | I <sub>INH</sub> = 0.2mA, VBAT = 5.5V | 0           |     | 0.8         | V     |

| I <sub>IL</sub>           | Leakage current                                                                 | SLEEP mode, $V_{INH} = 0V$            |             |     | 5           | μA    |

| Communication Co          | ntroller Interface                                                              |                                       |             |     |             |       |

| $V_{TxDIH}$               | Threshold for detecting TxD as on logical high                                  |                                       |             |     | 0.7*<br>Vio | V     |

| $V_{TxDIL}$               | Threshold for detecting TxD as on logical low                                   |                                       | 0.3*<br>Vio |     |             | V     |

| I <sub>TxDIH</sub>        | TxD high level input current                                                    |                                       | 30          |     | 100         | μΑ    |

| I <sub>TxDIL</sub>        | TxD low level input current                                                     |                                       | -5          |     | 5           | μA    |

| $V_{TxENIH}$              | Threshold for detecting TxEN as on logical high                                 |                                       |             |     | 0.7*<br>Vio | V     |

| V <sub>TXENIL</sub>       | Threshold for detecting TxEN as on logical low                                  |                                       | 0.3*<br>Vio |     |             | V     |

| I <sub>TxENIH</sub>       | TxEN high level input<br>current                                                |                                       | -5          |     | 5           | μA    |

| I <sub>TxENIL</sub>       | TxEN low level input<br>current                                                 |                                       | -100        |     | -30         | μA    |

| $V_{RxDOH}$               | RxD high level output voltage                                                   | $I_{RxD} = -4mA$ , $V_{IO} = 5V$      | 0.8*<br>Vio |     | 1.0*<br>Vio | V     |

| $V_{RxDOL}$               | RxD low level output voltage                                                    | $I_{RxD} = 4mA$ , $V_{IO} = 5V$       | 0           |     | 0.2*<br>Vio | V     |

| Host Interface            |                                                                                 |                                       |             |     |             |       |

| V <sub>STBNIH</sub>       | Threshold for detecting STBN as on logical high                                 |                                       |             |     | 0.7*<br>Vio | V     |

| V <sub>STBNIL</sub>       | Threshold for detecting STBN as on logical low                                  |                                       | 0.3*<br>Vio |     |             | V     |

| I <sub>STBNIH</sub>       | STBN high level input current                                                   |                                       | 30          |     | 100         | μA    |

| I <sub>STBNIL</sub>       | STBN low level input current                                                    |                                       | -5          |     | 5           | μA    |

| tstbn_deb_lp              | STBN de-bouncing time low power modes                                           |                                       | 0.1         |     | 40          | μs    |

| t <sub>STBN_DEB_NLP</sub> | STBN de-bouncing time non low power modes                                       |                                       | 0.1         |     | 2           | μs    |

Table 3. Electrical Characteristics

| Symbol                      | Parameter                                      | Conditions                         | Min         | Тур | Max         | Units |  |

|-----------------------------|------------------------------------------------|------------------------------------|-------------|-----|-------------|-------|--|

| V <sub>ENIH</sub>           | Threshold for detecting EN as on logical high  |                                    |             |     | 0.7*<br>Vio | V     |  |

| V <sub>ENIL</sub>           | Threshold for detecting EN as on logical low   |                                    | 0.3*<br>Vio |     |             | V     |  |

| I <sub>ENIH</sub>           | EN high level input current                    |                                    | 30          |     | 100         | μA    |  |

| I <sub>ENIL</sub>           | EN low level input current                     |                                    | -5          |     | 5           | μA    |  |

| ten_deb_lp                  | EN de-bouncing time low power modes            |                                    | 0.1         |     | 40          | μs    |  |

| t <sub>EN_DEB_NLP</sub>     | EN de-bouncing time non low power modes        |                                    | 0.1         |     | 2           | μs    |  |

| V <sub>ERRNOH</sub>         | ERRN high level output voltage                 | I <sub>ERRN</sub> = -4mA, Vio = 5V | 0.8*<br>Vio |     | 1.0*<br>Vio | ٧     |  |

| VERRNOL                     | ERRN low level output voltage                  | I <sub>ERRN</sub> = 4mA, Vio = 5V  | 0           |     | 0.2*<br>Vio | ٧     |  |

| Bus Guardian Inter          | face                                           |                                    |             |     |             |       |  |

| V <sub>BGEIH</sub>          | Threshold for detecting BGE as on logical high |                                    |             |     | 0.7*<br>Vio | V     |  |

| $V_{BGEIL}$                 | Threshold for detecting BGE as on logical low  |                                    | 0.3*<br>Vio |     |             | V     |  |

| I <sub>BGEIH</sub>          | BGE high level input current                   |                                    | 30          |     | 100         | μA    |  |

| I <sub>BGEIL</sub>          | BGE low level input current                    |                                    | -5          |     | 5           | μA    |  |

| V <sub>RxENOH</sub>         | RxEN high level output voltage                 | $I_{RxEN} = -4mA$ , $V_{IO} = 5V$  | 0.8*<br>Vio |     | 1.0*<br>Vio | V     |  |

| V <sub>Rx</sub> ENOL        | RxEN low level output voltage                  | I <sub>RxEN</sub> = 4mA, Vio = 5V  | 0           |     | 0.2*<br>Vio | V     |  |

| Read Out Interface          | Read Out Interface                             |                                    |             |     |             |       |  |

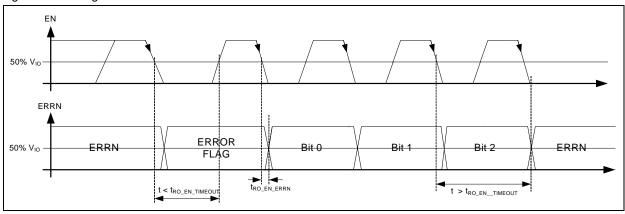

| t <sub>RO_EN_ERRN</sub>     | Propagation delay falling edge EN to ERRN      |                                    |             |     | 4.5         | μs    |  |

| t <sub>RO_EN_</sub> TIMEOUT | Error read out time out                        |                                    | 25          |     | 100         | μs    |  |

<sup>1.</sup> EN, STBN, ERRN, TxD, RxD, TxEN, BGE, RxEN, LWAKE, INH1, INH2: open

<sup>2.</sup> Test condition: (V<sub>BP</sub> + V<sub>BM</sub>) / 2 = 2,5V  $\pm$  5%

<sup>3.</sup> For test signal (see Figure 18)

# 7 Typical Operating Characteristics

Figure 3. Figure 4.

Figure 5. Figure 6.

Figure 7. Figure 8.

# 8 Detailed Description

The AS8221 is a high-speed fault tolerant device operating as an interface between a generic controller and the copper wire physical bus. The AS8221 is designed to extend the application range for high speed and safety critical time triggered bus systems in an automotive environment. The drivers are short circuit protected against the positive and negative supply voltage to increase the robustness and reliability of automotive systems. The AS8221 operates at baudrates up to 10 Mbps to increase the bandwidth for automotive applications.

## **Block Description**

The electrical AS8221 high-speed bus-system transceiver is the interface between a FlexRay<sup>™</sup> network node module and the channel. The transceiver provides differential transmit and receive capability to the bus, allowing the node module bidirectional time multiplexed binary data stream transfer. Besides the transmit and receive function, the transceiver provides low power management, supply voltage monitoring (under voltage detection) as well as bus failure detection and represents a ESD-protection barrier between the bus and the ECU.

The AS8221 consists of 9 different functional blocks(see Figure 1):

Table 4. Functional Blocks

| Functional Block                                          | Short Description                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Controller Interface (HCI)                           | Digital interface between the transceiver and the host controller (HC)  The host interface comprises the read out handler, which delivers failure and status information via the ERRN pin to the host controller.                                                                                      |

| Communication Controller Interface (CCI)                  | Digital interface between the transceiver and the FlexRay communication controller (CC)                                                                                                                                                                                                                |

| Bus Guarding Interface (BGI)                              | Digital interface between the transceiver and the FlexRay bus guardian (BG)                                                                                                                                                                                                                            |

| Power Supply Interface<br>(PSI)                           | The power supply interface consists of an sub functional block, the voltage monitor (VM) and includes two analogue inhibit outputs for signalling the internal state of the transceiver                                                                                                                |

| Internal Logic (IL)                                       | The digital signals from the functional blocks of the device are fed into the internal logic where the forwarding of FlexRay messages from analogue side to digital interfaces and vice versa is done. The state machine is performed in this block and is dealing the error, wake and power-on flags. |

| Bus Failure Detector (BFD)<br>Temperature Protection (TP) | The bus failure detector is directly connected to the bus pins, in order to detect several external failure conditions which may occur on the bus.  The temperature protection turns off the output driver when reaching the specified internal temperature in order to protect the device.            |

| Transmitter                                               | The transmitter provides the bus signals as specified on the bus lines.                                                                                                                                                                                                                                |

| Receiver                                                  | The receiver captures FlexRay valid signals on the bus lines and provides received data streams to the internal logic                                                                                                                                                                                  |

| Wake-Up Detector (WUD)                                    | The wake-up detector recognizes valid wake-up frames on the bus, recognizes a wake signal on the local WAKE pin and signals valid wake-up events to the internal logic.                                                                                                                                |

#### **Events**

Transitions in order to change between the operation modes are possible only when events are detected. The device supports three type of events, events on the host controller interface (STBN, EN), detection of undervoltage or supply voltage recovery, and detected wake events. Whenever an event is recognized, a transition can be performed.

## **Operating Modes**

The AS8221 provides the following operating modes:

- NORMAL: non low power mode

- RECEIVE ONLY: non low power mode

STANDBY: low power modeGO TO SLEEP: low power mode

■ SLEEP: low power mode

#### **NORMAL** mode

In this mode the transceiver is able to send and receive data signals on the bus. TxEN and BGE control the state of the transmitter. INH1 and INH2 outputs are set high. RxD reflects the bus data and reflect the bus state. The error read out mechanism is enabled. In this mode, the transmitter state can be selected as shown in the Table 5. In case the over-temperature flag is set the transmitter is disabled. The bus wires are terminated to Vcc/2 via receiver input resistances.

Table 5. Transmitter State

| BGE | TxEN | TxD | Transmitter state | Bus State                                   |

|-----|------|-----|-------------------|---------------------------------------------|

| Н   | L    | Н   | Enabled           | Data1 (BP is driven high, BM is driven low) |

| Н   | L    | L   | Enabled           | Data0 (BP is driven low, BM is driven High) |

| Х   | Н    | Х   | Disabled          | Idle (BP and BM are not driven)             |

| L   | Х    | Х   | Disabled          | Idle (BP and BM are not driven)             |

- If the differential bus voltage is higher than V<sub>BUSActivehigh</sub> or lower than V<sub>BUSActivelow</sub> for a time longer than t<sub>BUSActivityDetection</sub>, then activity is detected on the bus (Bus = active), RxEN is switched to logical "low" and RxD is released.

- If, after the activity detection, the differential bus voltage is higher than V<sub>Data1</sub>, RxD is high.

- If, after the activity detection, the differential bus voltage is lover than V<sub>Data0</sub>, RxD is low.

- If the absolute differential bus voltage is lower than V<sub>BUSActivehigh</sub> and higher than V<sub>BUSActivelow</sub> for a time longer than t<sub>BUSIdleDetection</sub>, then idle is detected on the bus (Bus = idle), RxEN and RxD are switched to logical "high"

#### **RECEIVE ONLY mode**

In this mode the transceiver has the same behaviour as in NORMAL mode but the transmitter is disabled.

#### STANDBY mode

In this mode the transceiver is not able to send and receive data signals from the bus, but the wake-up detector is active. The power consumption is significantly reduced respect the non low power operation modes. RxD and RxEN, reflects the negation of the wake-up flag. INH1 is set to high. If wake-up flag is set then INH2 is high, otherwise it is floating. The error read out mechanism is not enabled. The bus wires are terminated to GND (bus state: Idle\_LP).

#### **GO TO SLEEP mode**

In this mode the transceiver has the same behavior as in STANDBY mode but if this mode is selected for a time longer than t<sub>SLEEP</sub> and the wake flag is cleared the device enters into the SLEEP mode.

#### **SLEEP mode**

In this mode the transceiver has the same behaviour as in STANDBY mode but INH1 and INH2 are floating.

#### Non Operating Mode

The AS8221 provides the following non operating mode:

#### **POWER OFF**

In this mode the transceiver is not able to operate. RxD, RxEN are set to high and ERRN is set to low. INH1 and INH2 are floating. The bus wires are not connected to GND (bus state: Idle\_HZ).

# **Undervoltage Events**

## Undervoltage VBAT

When VBAT voltage falls below  $V_{BATTHL}$  for a time longer than  $t_{UV\_DETECT}$  then the undervoltage VBAT flag is set and it is reset when VBAT exceeds the voltage threshold  $V_{BATTHH}$  for a time longer than  $t_{UV\_REC}$  or in case a wake-up event has been detected. The flag can be set or reset in all the modes.

#### **Undervoltage** Vio

When Vio voltage falls below  $V_{IOTHL}$  for a time longer than  $t_{UV\_DETECT}$  then the undervoltage Vio flag is set and it is reset when Vio exceeds the voltage threshold  $V_{IOTHH}$  for a time longer than  $t_{UV\_REC}$  or in case a wake-up event has been detected. The flag can be set or reset in all the operation modes. The flag is reset at POWER OFF.

#### **Undervoltage Vcc**

When Vcc voltage falls below  $V_{CCTHL}$  for a time longer than  $t_{UV\_DETECT}$  then the undervoltage Vcc flag is set and it is reset when Vcc exceeds the voltage threshold  $V_{CCTHH}$  for a time longer than  $t_{UV\_REC}$  or in case a wake-up event has been detected. The flag can be set or reset in all the operation modes. The flag is reset at POWER OFF.

#### **Power On/Off Events**

- Starting from POWER OFF mode a power on event occurs in case VBAT undervoltage flag is reset.

- Starting from every operation mode a power off event occurs in case VBAT and Vcc undervoltage flags are set.

# **Wake-Up Events**

A wake-up event can be detected only in low power modes. The wake-up flag is set when the remote or local wake flag is set. The wake-up flag is reset when the remote and local wake-up flags are reset. The remote wake-up flag is set if a remote wake-up event occurs. The local wake-up flag is set if a local wake-up event occurs. The remote and local wake-up flags are reset entering a low power mode from a non low power mode, entering NORMAL mode, whenever an undervoltage event occurs and at POWER OFF.

#### Remote Wake-Up event

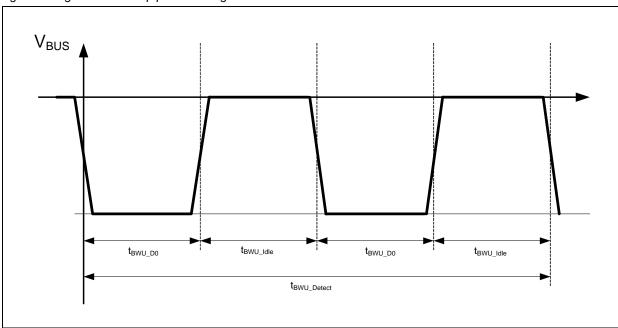

A remote wake-up event, only possible in low power mode, consists in the reception of at least two consecutive wake-up symbols via the bus within t<sub>BWU</sub>. The wake-up symbol is defined as Data0 longer than t<sub>BWU0</sub> followed by idle or Data1 longer than t<sub>BWUidle</sub> as in Figure 9 unless an undervoltage or wake-up event is present.

Figure 9. Signal for wake-up pattern recognition

# **Local Wake-Up Event**

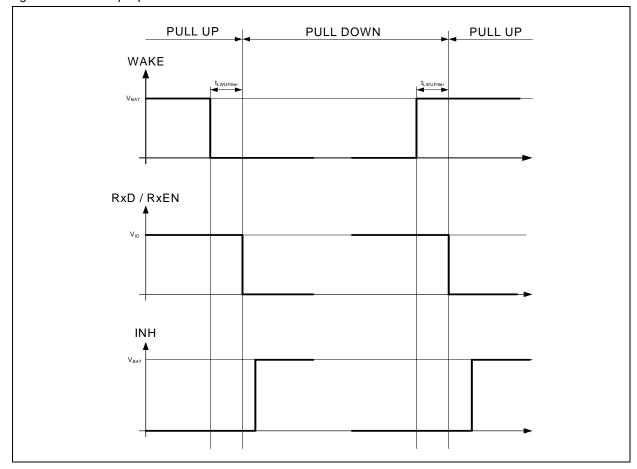

In all low power modes, if the voltage on the WAKE pin falls below  $V_{LWUTH}$  for longer than  $t_{LWFilter}$ , a local wake-up event is detected. At the same time the biasing of the pin is switched to pull-down. If the voltage on the WAKE pin rises above  $V_{LWUTH}$  for longer than  $t_{LWFilter}$ , a local wake-up event is detected. At the same time the biasing of the pin is switched to pull-up. The pull up and down mechanism is also active in non low power modes.

Figure 10. WAKE input pin behavior

# **System Description**

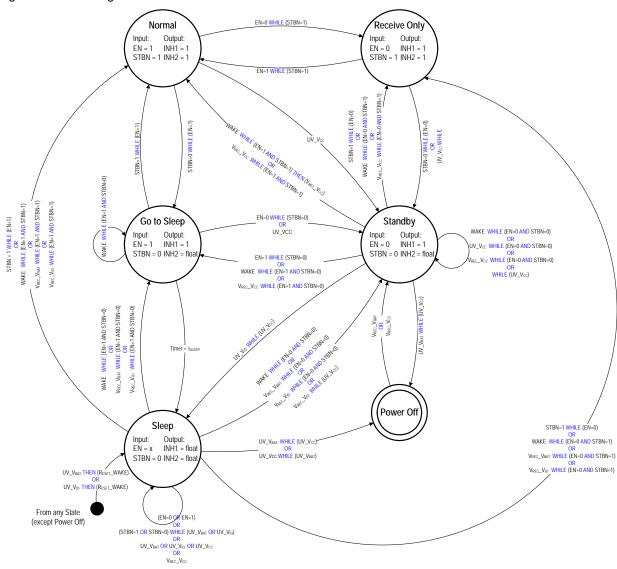

Figure 11. State Diagram

Note: This state diagram does not include all transitions, which are shown in Table 7

Prefix of "WHILE" is always the event and suffix in brackets checks the flags or in case of EN and STBN the input condition. For example: VREC\_VBAT WHILE (EN=0 AND STBN=0)

After the event VBAT supply voltage recovery is detected, the transition is performed if EN and STBN are "low". Legend:

UV\_VBAT: Undervoltage event and/or flag for VBAT supply voltage

UV\_V<sub>IO</sub>: Undervoltage event and/or flag for V<sub>IO</sub> supply voltage

$UV\_V_{CC}$ : Undervoltage event and/or flag for Vcc supply voltage

VREC\_VBAT: Voltage recovery event and/or flag for VBAT supply voltage

V<sub>REC</sub>\_V<sub>IO</sub>: Voltage recovery event and/or flag for V<sub>IO</sub> supply voltage

V<sub>REC</sub>\_V<sub>CC</sub>: Voltage recovery event and/or flag for V<sub>CC</sub> supply voltage

Wake: Wake event and/or flag

#### **Fail Silent Behavior**

In order to be fail silent, undervoltage detection on the three power supplies VBAT, VIO and Vcc is implemented

- VBAT: Battery supply voltage

- Vio: Supply voltage for I/O digital level adaptation

- Vcc: Supply voltage (+5V)

#### State transitions due to under voltage detection

- In case of VBAT or Vio undervoltage is detected, SLEEP mode will be entered regardless of the voltage present on pins EN and STBN.

- In case Vcc undervoltage is detected, STANDBY mode will be entered regardless of the voltage present on pins EN and STBN.

- VBAT and Vio undervoltage detection have higher priority than Vcc undervoltage detection.

- In case VBAT and Vcc undervoltage are detected, POWER OFF mode is entered (bus state: Idle\_HZ).

#### State transitions due to voltage recovery detection

- If the undervoltage recovers the device will enter the mode determined by the voltages at pins EN and STBN.

- Starting from the Power Off, the device enters the state indicated by the host input pins (EN, STBN) only when VBAT or VCC recovers (VBAT ≥ VBATTHH or VCC ≥ VCCTHH) while VIo is available (undervoltage flag of VIo flag not set). If the VIo undervoltage flag is set, the STANDBY mode will be entered. In both cases the Power On flag is set.

- When VBAT ≤ VBATTHL and VCC ≤ VCCTHL the device is in power off state and the bus wires are not terminated (bus state: Idle\_HZ).

#### **Wake-Up Mechanism**

The wake-up detector is active in all low power modes. In case a remote o local wake-up occurs the VBAT, VIO, VCC undervoltage flags are reset, the wake-up flag is set, INH outputs are switched on and the device enters the state indicated by the host pins.

#### Remote Wake-Up

A remote wake-up event or bus wake-up event is the reception of at least two consecutive wake-up symbols via the bus within t<sub>BWU</sub>. The wake-up symbol is defined as Data0 longer than t<sub>BWUIdle</sub>.

#### **Mode Transitions**

Starting from every operation mode the device enters POWER OFF in case a power off event occurs regardless the Vio undervoltage flag, the wake-up flag and the host input pins (EN, STBN) state.

Starting from the POWER OFF the device enters STANDBY only in case a power on event occurs.

Starting from every operation mode the device enters SLEEP in case VBAT or VIO undervoltage flag is set regardless the Vcc undervoltage flag, the wake-up flag and the host input pins state.

Starting from every operation mode except SLEEP the device enters STANDBY in case Vcc undervoltage flag is set and VBAT and VIO undervoltage flags are not set, regardless the wake-up flag indication and the host input pins state.

Starting from a low power mode the device enters the operation mode indicated by the host input pins if a wake-up event occurs.

In case all the undervoltage flags are reset the operation mode is selected by the wake-up flag and the host pins according to Table 6.

Table 6. Pin Signalling and Operating modes

| Inputs |        | Operation Mode               | OutPut                       |                              |                    |       |       |  |  |

|--------|--------|------------------------------|------------------------------|------------------------------|--------------------|-------|-------|--|--|

| STBN   | EN     | Operation Mode               | RxD                          | ERRN                         | RxEN               | INH1  | INH2  |  |  |

|        |        |                              | L<br>Bus = Data_0            |                              | L<br>Bus = Active  |       |       |  |  |

| НН     | NORMAL | H<br>Bus = Idle or<br>Data_1 | not (Error flag)             | H<br>Bus = Idle              | Н                  | Н     |       |  |  |

|        |        |                              | L<br>Bus = Data_0            |                              | L<br>Bus = Active  |       | Н     |  |  |

| Н      | L      | RECEIVE ONLY                 | H<br>Bus = Idle or<br>Data_1 | not (Error flag)             | H<br>Bus = Idle    | Н     |       |  |  |

| L      | Н      | GO TO SLEEP                  | not (Wake-up flag)           | not (Wake-upake-<br>up flag) | not (Wake-up flag) | Н     | Float |  |  |

| L      | L      | STANDBY                      | not (Wake-up flag)           | not (Wake-up flag)           | not (Wake-up flag) | Н     | Float |  |  |

| L      | Х      | SLEEP                        | not (Wake-up flag)           | not (Wake-up flag)           | not (Wake-up flag) | Float | Float |  |  |

| Х      | Х      | POWER OFF                    | Н                            | L                            | Н                  | Float | Float |  |  |

Where: H = Digital level high

L = Digital level low

x = Do not care

Float = The analog output is not driven

**Note:** If GO TO SLEEP is selected for more than t<sub>SLEEP</sub> then the device will enter SLEEP only if the wake-up flag is not set otherwise it will remain in GO TO SLEEP.

If wake-up flag is set INH2=H otherwise INH2=floating.

Starting from SLEEP, if the wake-up flag is set, the device enters STANDBY regardless the host pins state and UV flags. Starting from SLEEP, if the wake-up flag is not set, the only operating mode that can be entered through host pins are the non low power modes.

**Operating Mode Transitions**

Table 7. Transition Table

| Transition      |                 | Event | Under Voltage Flag |              |             | Wake    | Host Input |         | Remarks          |

|-----------------|-----------------|-------|--------------------|--------------|-------------|---------|------------|---------|------------------|

| Start Point     | Destination     | Event | <b>V</b> IO        | <b>V</b> BAT | <b>V</b> cc | Flag    | STBN       | EN      | Remarks          |

|                 | RECEIVE<br>ONLY | S     | L                  | L            | L           | Х       | Н          | (1) H→L |                  |

|                 | STANDBY         | U     | L                  | L            | (1) L→H     | (2) X→L | Н          | Н       |                  |

| NORMAL          | GO TO<br>SLEEP  | S     | L                  | L            | L           | (2) X→L | (1) H→L    | Н       | timer<br>enabled |

|                 | SLEEP           | U     | (1) L→H            | L            | L           | (2) X→L | Н          | Н       |                  |

|                 |                 | U     | L                  | (1) L→H      |             | (2) X→L | Н          | Н       |                  |

|                 | NORMAL          | S     | L                  | L            | L           | Х       | Н          | (1) L→H |                  |

|                 | STANDBY         | S     | L                  | L            | L           | (2) X→L | (1) H→L    | L       |                  |

| RECEIVE<br>ONLY | STAINDET        | U     | L                  | L            | (1) L→H     | (2) X→L | Н          | L       |                  |

|                 | SLEEP           | U     | (1) L→H            | L            | L           | (2) X→L | Н          | L       |                  |

|                 | SLEEP           | J     | L                  | (1) L→H      | L           | (2) X→L | Н          | L       |                  |

Table 7. Transition Table

| Transition  |                 | Unc   |             | der Voltage Flag |             | Wake    | Host    | Input   | Domorko              |

|-------------|-----------------|-------|-------------|------------------|-------------|---------|---------|---------|----------------------|

| Start Point | Destination     | Event | <b>V</b> IO | <b>V</b> BAT     | <b>V</b> cc | Flag    | STBN    | EN      | Remarks              |

|             | NODMAL          | U     | L           | L                | (1) H→L     | L       | Н       | Н       |                      |

|             | NORMAL          | W     | L           | L                | (2) H→L     | (1) L→H | Н       | Н       |                      |

|             |                 | S     | L           | L                | L           | Х       | (1) L→H | L       |                      |

|             | RECEIVE<br>ONLY | U     | L           | L                | (1) H→L     | L       | Н       | L       |                      |

|             |                 | W     | L           | L                | (2) H→L     | (1) L→H | Н       | L       |                      |

|             |                 | S     | L           | L                | L           | L       | L       | (1) L→H | timer<br>enabled     |

|             | GO TO           | S     | L           | L                | L           | Н       | L       | (1) L→H | timer<br>disabled    |

| STANDBY     | SLEEP           | U     | L           | L                | (1) H→L     | L       | L       | Н       | timer<br>enabled     |

| 01744221    |                 | W     | L           | L                | (2) H→L     | (1) L→H | L       | Н       | timer<br>disabled    |

|             | SLEEP           | J     | (1) L→H     | L                | L           | (2) X→L | L       | L       |                      |

|             |                 | U     | (1) L→H     | L                | Н           | L       | Χ       | Х       |                      |

|             |                 | U     | L           | (1) L→H          | L           | (2) X→L | L       | L       |                      |

|             | STANDBY         | W     | L           | L                | (2) X→L     | (1) L→H | L       | L       |                      |

|             |                 | U     | L           | L                | (1) L→H     | (2) X→L | L       | L       |                      |

|             |                 | U     | L           | L                | (1) H→L     | L       | L       | L       |                      |

|             |                 | S     | L           | L                | Н           | Г       | (1) L↔H | Х       |                      |

|             |                 | S     | L           | L                | Н           | L       | Х       | (1) L↔H |                      |

|             | NORMAL          | S     | L           | L                | L           | Х       | (1) L→H | Н       |                      |

|             | STANDBY         | S     | L           | L                | L           | Х       | L       | (1) H→L |                      |

|             | STAINDDT        | U     | L           | L                | (1) L→H     | (2) X→L | L       | Н       |                      |

| GO TO       |                 | S     | L           | L                | L           | L       | L       | Н       | t≥t <sub>SLEEP</sub> |

| SLEEP       | SLEEP           | U     | (1) L→H     | L                | L           | (2) X→L | L       | Н       |                      |

|             |                 | U     | L           | (1) L→H          | L           | (2) X→L | L       | Н       |                      |

|             | GO TO<br>SLEEP  | W     | L           | L                | L           | (1) L→H | L       | Н       | timer<br>disabled    |

Table 7. Transition Table

| Transition  |                |       | Under Voltage Flag |              | Wake        | Host    | Input   | Domonico |                   |

|-------------|----------------|-------|--------------------|--------------|-------------|---------|---------|----------|-------------------|